自对准硅化物 (Self -Aligned Silicide) 工艺

描述

自对准硅化物 (Self -Aligned Silicide) 工艺

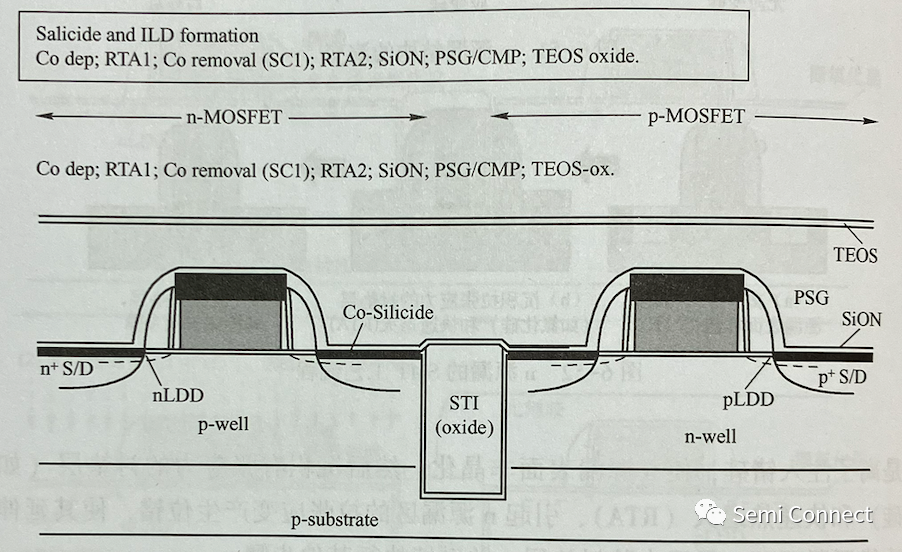

传统的 CMOS 工艺(如32nm或更早的节点上)是基于氧化硅/多晶硅结构形成源漏的(即非 HKMG 和非应变源漏的工艺流程),因此称为先栅 ( Gate-First)工艺。在有源区和多晶硅栅区多采用同时形成硅化物的自对准技术,如图所示。

形成多晶硅栅和源漏之后,先用湿法或干法清除在有源区 (AA)和多晶硅栅表面的氧化物,溅射一薄层(厚度范围 10~20nm)金属(钴Co 或镍Ni),紧接着进行第1次 RTA(温度范围为 400-550°C),与硅接触的金属发生反应形成金属硅化物(Metal Silicide)。然后,用 SC1 溶剂去掉氧化硅上剩余的未参与反应的金属,并进行第2 次RTA(温度约为 700°C),在有源区和多晶硅栅区域上留有金属硅化物,这一过程被称为自对准硅化物工艺。之后,沉积氮氧硅和磷硅玻璃(PSG),并用CMP 进行平坦化,再沉积一层 CVD 氧化物(TEOS-ox)来密封 PSG,形成栅-金属层间介质 (Inter-Layer Dielectrie, ILD)。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Salicide自对准硅化物工艺的定义和制造流程2025-12-26 205

-

自对准双重图案化技术的优势与步骤2025-05-28 1418

-

芯片制造中自对准接触技术介绍2025-05-19 1290

-

IBC技术新突破:基于物理气相沉积(PVD)的自对准背接触SABC太阳能电池开发2025-04-14 1283

-

Salicide工艺的制造流程2024-11-11 3310

-

ADXL355的self test作用是什么?2023-12-28 426

-

FinFET工艺之self-heating概念介绍2023-12-07 5101

-

半导体行业之刻蚀工艺技术2023-04-07 5078

-

集成电路芯片制造中的3种硅化物工艺介绍2022-11-21 11958

-

#硬声创作季 #制造 微纳加工技术-08.02 自对准硅化物-2水管工 2022-09-23

-

半导体制造的合金化热处理工艺2022-09-21 7021

-

Self-Oscillating_Converter电路设计2016-01-12 421

全部0条评论

快来发表一下你的评论吧 !