现实中微电子制造领域的静电问题

描述

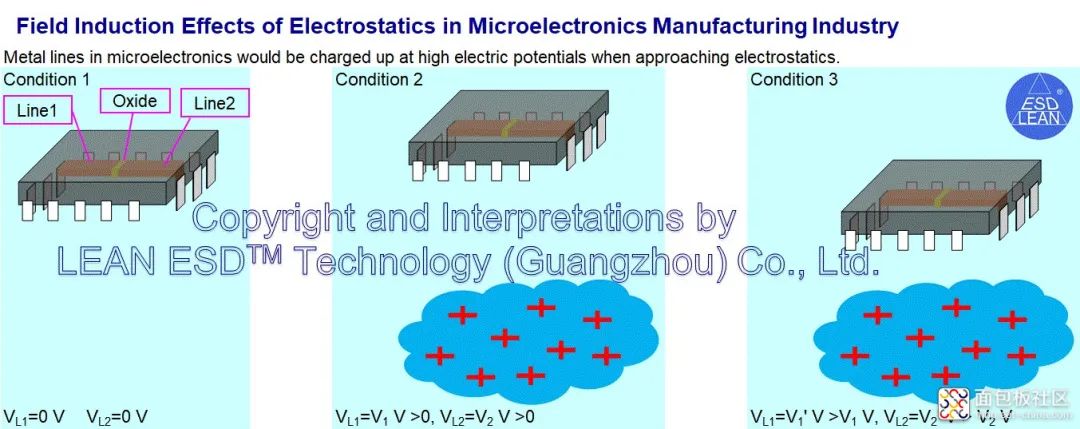

微电子制造中的静电问题都是存在于众多微小的细节之中。 微电子制造中存在大量的生产工序会产生并累积静电。 静电的直接影响之一就是通过静电感应作用将临近的微电子器件(确切而言,是其中的大量金属线路)充电至高静电位。

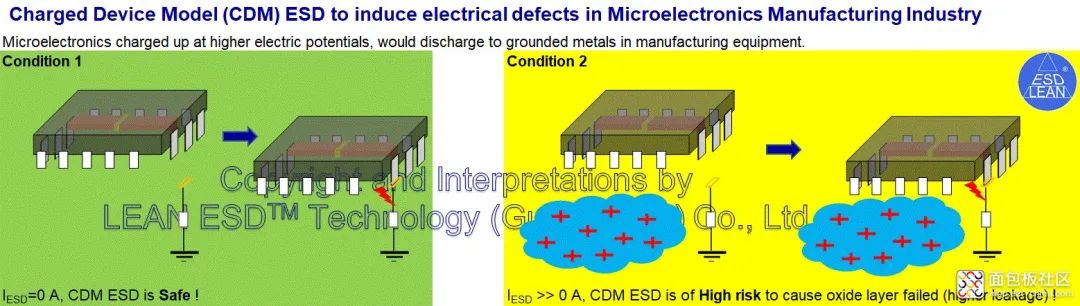

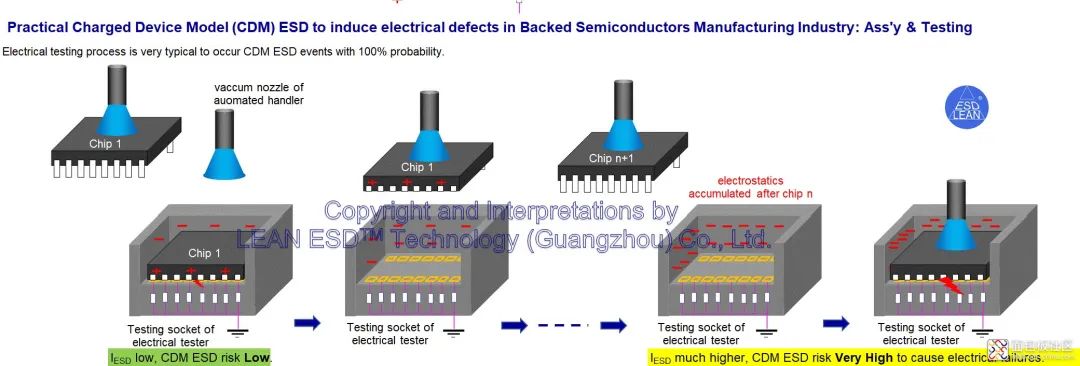

而微电子制造中涉及的许多电气测试机台(IC封测工厂就含有大量的电测工序),就是典型的CDM(Charged Device Model,器件带电放电模型) ESD关键工序(100%会发生CDM ESD),由此导致微电子器件的电性不良风险(主要是器件中的绝缘膜层漏电流过大,如gate oxide)必须得到重视并采取有效的管控措施;

而电气测试机台中的testing socket(测试插座)尤其是其中的器件装载导引机构大都采用绝缘塑胶或陶瓷材质,每颗器件的测试过程都会发生器件封装体与testing socket导引机构件之间的摩擦静电起电,随着测试机台测试越来越多的器件,如果testing socket上累积的静电得不到及时的有效消除,越到后面测试的器件发生CDM ESD导致的电气失效不良风险就越高。

当前基于28nm制程及以下的IC已经占比将近50%,其最高承受的CDM ESD电压大部分不超过100V。其中,最新的7nm、5nm制程的5G IC,CDM耐压更是降至50V以下,这种IC的设计与制程变化,给集成电路前段制造-Wafer Fab、集成电路后段制造-封装与测试、以及SMT工厂的生产工艺中的ESD防护带来了非常大的挑战。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

求问帖!静电消除器在电子半导体领域的具体应用与需求!2024-12-26 2315

-

汽车智能化电子制造趋势2011-01-24 2731

-

电子产品制造中的静电源2012-09-24 4021

-

实施防静电措施对产品设计及制造中的好处2013-01-28 1925

-

微电子封装技术2013-12-24 6376

-

静电对微电子制造业的影响2014-01-03 2973

-

浅谈静电发生器2017-07-31 3267

-

灵动微电子成功完成C轮融资2019-03-12 3130

-

微电子机械系统加速传感器在医疗领域有什么应用?2020-04-20 1759

-

浅谈电子制造过程中的静电及静电防护2009-12-18 945

-

微电子和电子制造领域的重要仪器设备——半导体推力测试仪2023-07-13 1144

-

数据挖掘定义及方法 数据挖掘在微电子领域的应用2023-07-18 744

-

揭秘微电子制造与封装技术的融合之路2023-12-18 1340

-

微电子制造和封装技术发展研究2023-12-19 1417

-

静电卡盘:半导体制造中的隐形冠军2025-03-31 3997

全部0条评论

快来发表一下你的评论吧 !