求一种PCI Express(PCIe)5.0规范的完整时钟解决方案

描述

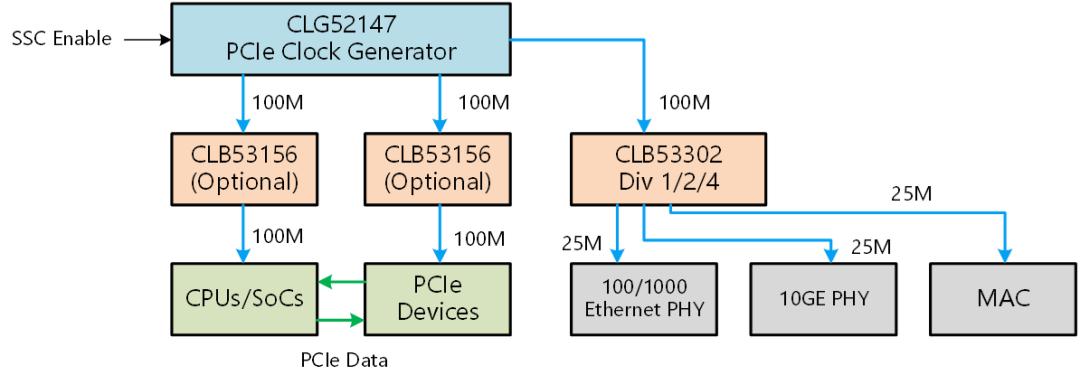

核芯互联日前推出了满足PCI Express(PCIe)5.0 规范的完整时钟解决方案,全系列产品完全兼容 PCIe Gen 5 通用时钟、分离参考无展频(SRNS)和分离参考独立展频(SRIS)架构,整体方案能够提供同类产品领先的抖动性能,留有显著的设计余量,同时向下兼容PCIe Gen1/2/3/4。

核芯互联日前推出了满足PCI Express(PCIe)5.0 规范的完整时钟解决方案,全系列产品完全兼容 PCIe Gen 5 通用时钟、分离参考无展频(SRNS)和分离参考独立展频(SRIS)架构,整体方案能够提供同类产品领先的抖动性能,留有显著的设计余量,同时向下兼容PCIe Gen1/2/3/4。

方案的所有器件全面支持SSC扩频技术以显著地降低EMI。方案的所有器件都可以工作在-40~125℃温度范围,并在AEC-Q100认证中。

其中时钟生成器CLG52147 PCIe可以提供9路100MHz独立的LP-HCSL时钟输出,在PCIe Gen 5.0 Common Clock架构下,RMS Jitter典型值仅为10fs; 时钟Buffer CLB53156可以提供6路PCIe 5.0兼容输出,在PCIe Gen 5.0 Common Clock架构下附加抖动仅为6fs;时钟Buffer CLB53302/53305可以提供多达10路任意形式差分或者20路任意形式单端输出,并且提供两组独立的1/2/4分频,在100MHz输入时钟的条件下,可以独立地输出两组(每组5个差分或者10个单端)100MHz、50MHz或者25MHz时钟,充分简化了了PCB设计。

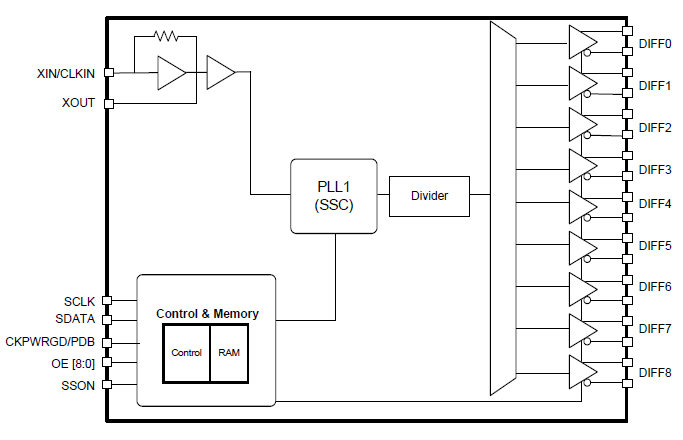

CLG52147

CLG52147是一颗高性能的PCIe参考时钟发生器,使用25MHz晶振或时钟输入,采用3.3V供电,符合PCIe Gen1/2/3/4/5规范,支持SRNS和Common Clock架构,支持SSC以降低EMI。CLG52147具有业界领先的抖动指标,PCIe Gen 5 CC的RMS Jitter 典型值为10fs。CLG52147有9个独立的控制引脚用来开启或关断输出以降低功耗。

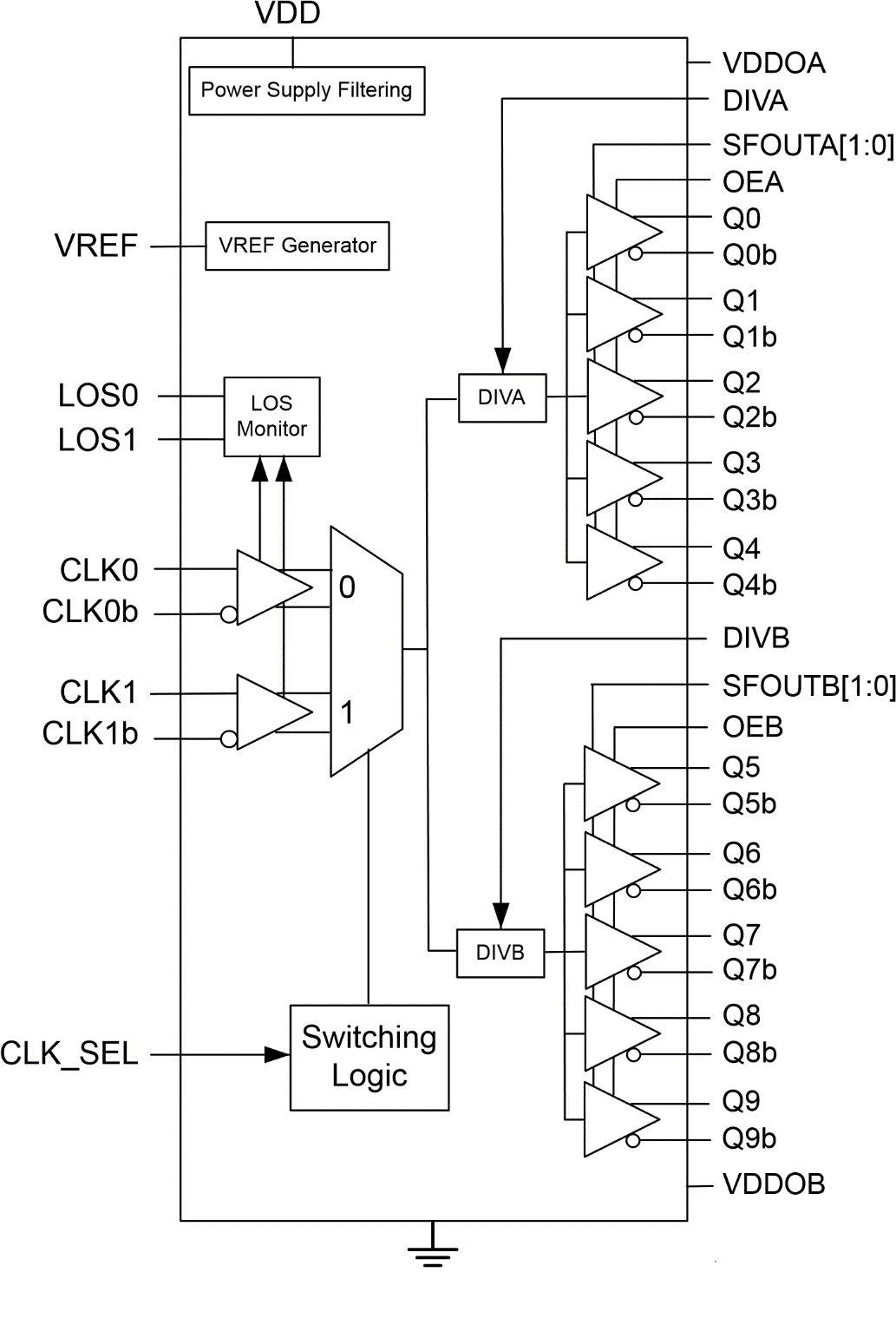

CLG52147功能框图

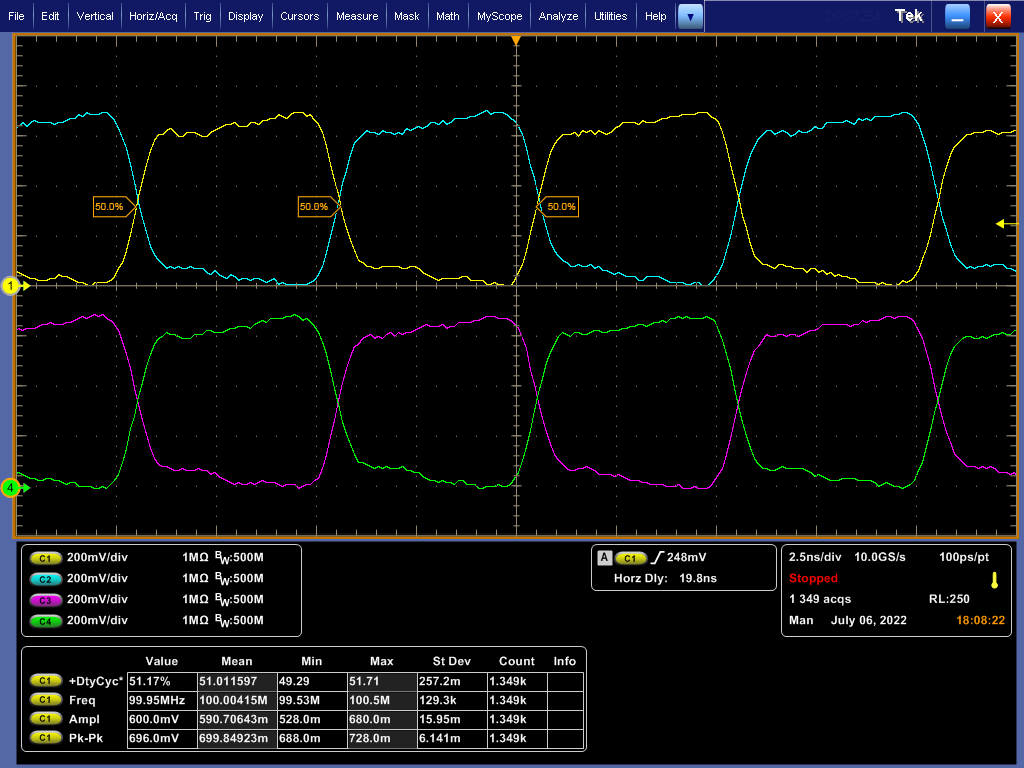

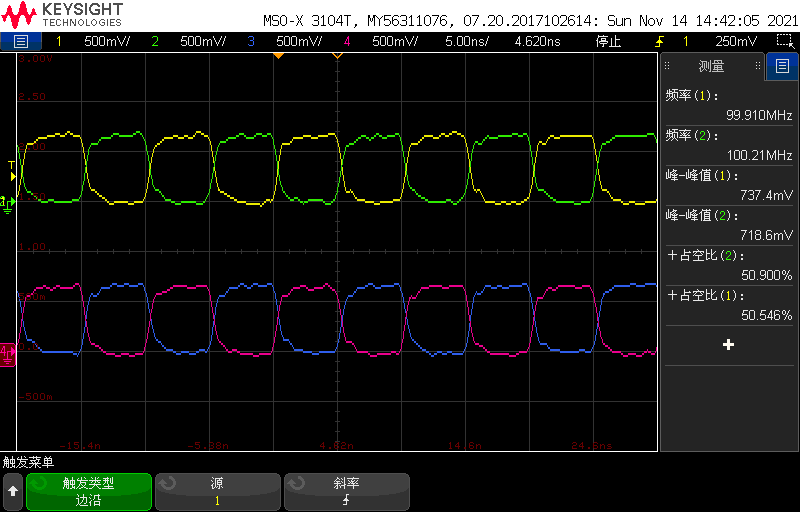

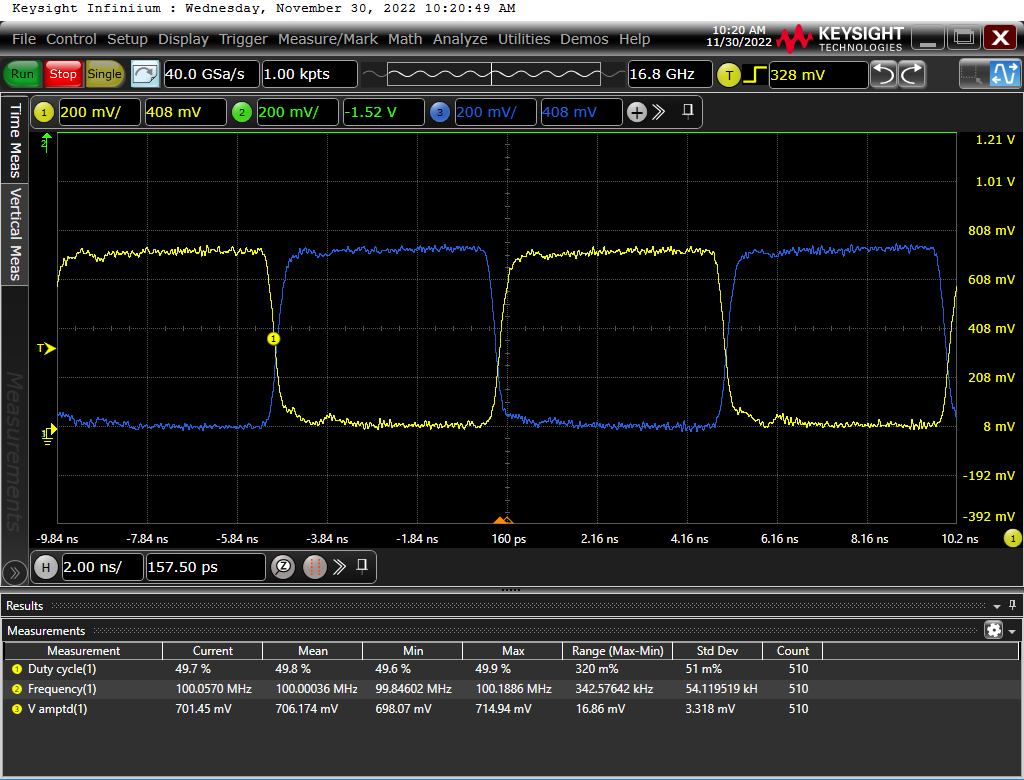

CLG52147差分输出波形

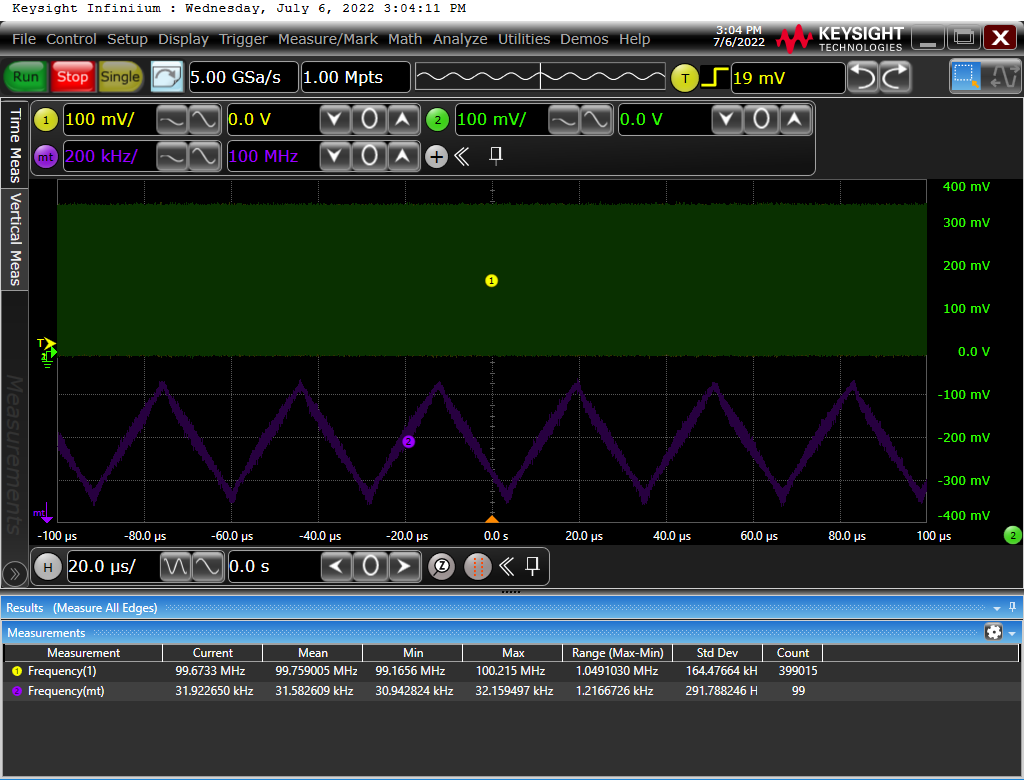

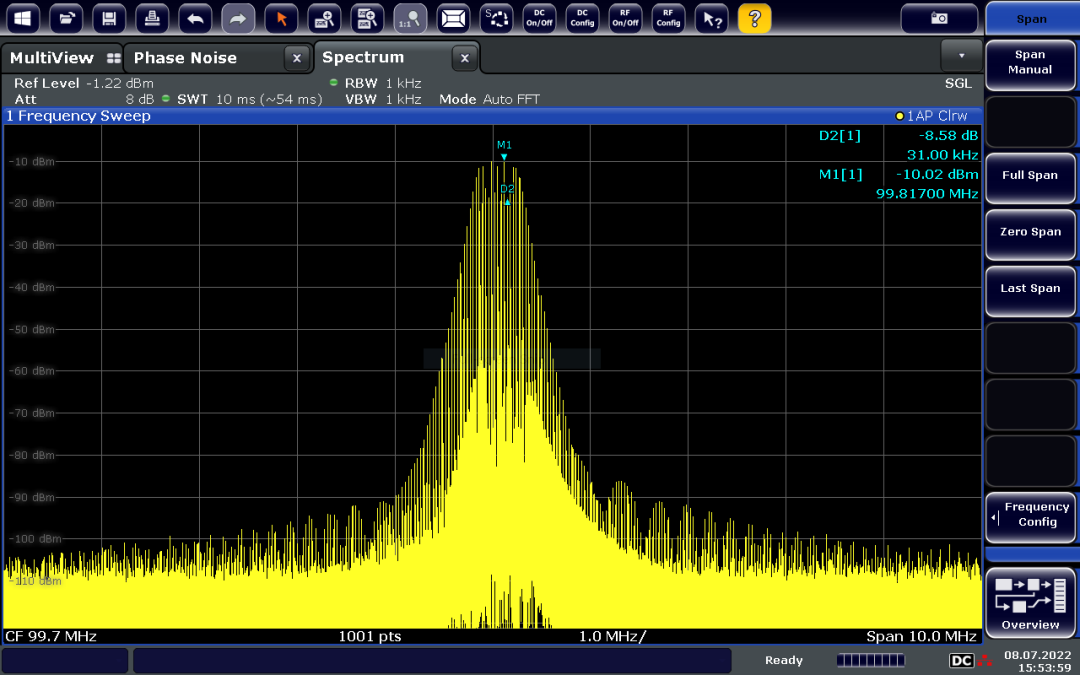

CLG52147 SSC展频

CLG52147 SSC展频频谱

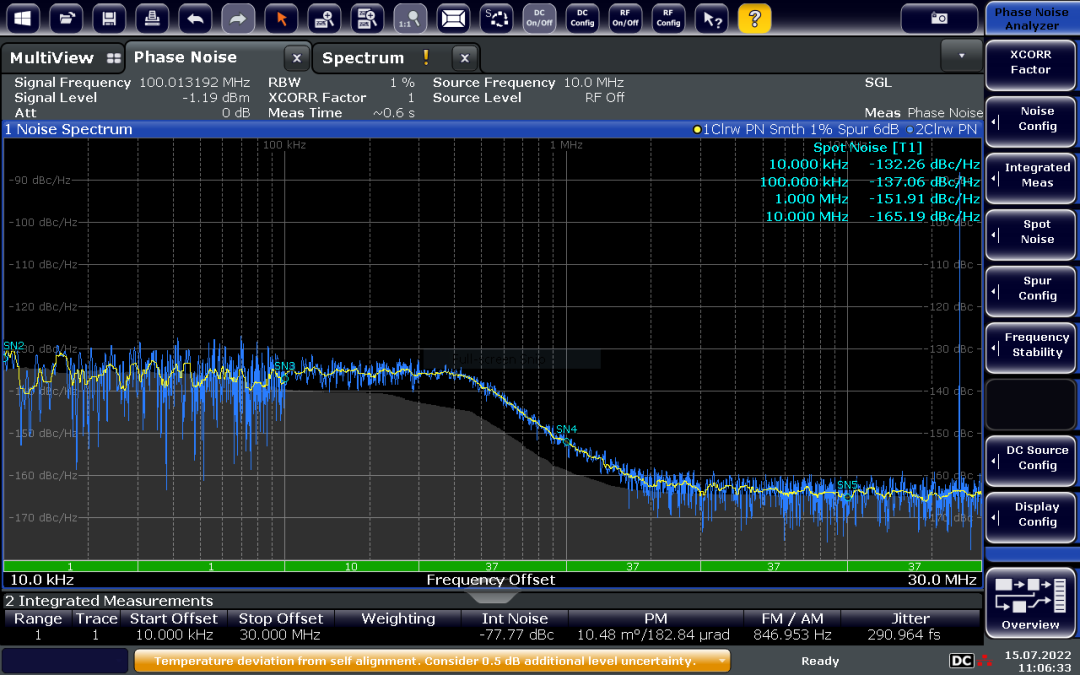

CLG52147典型相噪测试

CLB53156

CLB53156是一颗6路LP-HCSL输出的,满足PCIe 5.0规范的低抖动时钟Buffer芯片,该芯片同时也提供PCIe Gen 1/2/3/4的前向兼容性。CLB53156在PCIe Gen 5.0时附加抖动仅为6 fs,优秀的性能可以为设计人员提供更多的冗余而使整机获得更高的性能。

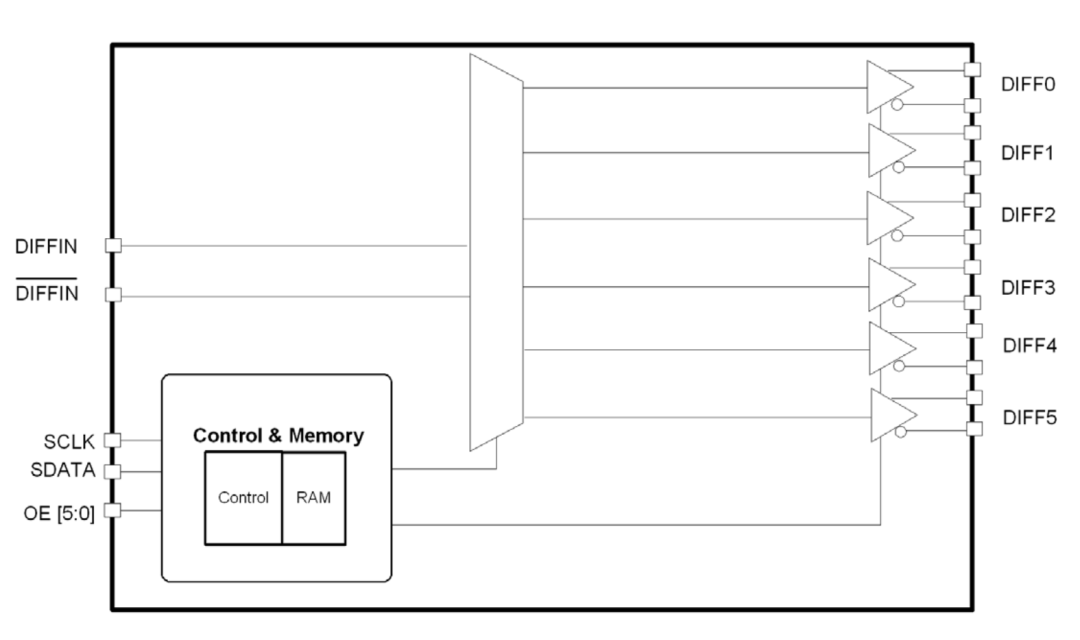

CLB53156功能框图

CLB53156差分输出波形

CLB53302/53305

CLB53302是一颗支持1/2/4分频的时钟通用时钟Buffer,可以支持20路任意形式单端输出或者10路任意形式差分输出,同时输入输出可以支持1.8V/2.5V/3.3V任意电压转换,可以用在包括PCIe 1/2/3/4/5、基站、存储、服务器、汽车等在内的任意场合,该芯片具有以下特性:

支持PCIe Gen1/2/3/4/5

支持1–750 MHz工作频率

支持任意输入输出格式:LVPECL, High Swing

CML, LVDS, CML, HCSL, LVCMOS

内置LDO以提高电源抑制比

支持20路单端或者10路差分输出

输出支持1/2/4分频

输入输出支持任意电压转换:1.8V/2.5V/3.3V

CLB53302功能框图

CLB53302 HCSL输出波形

审核编辑:刘清

-

PCIe 5.0验证实战,经常遇到的那些问题?2023-10-27 3003

-

PCI Express卡机电规格2023-03-13 800

-

Cadence PCIe 5.0技术通过PCI-SIG®认证测试2022-06-23 2833

-

如何去设计一种PCI Express接口?2021-05-21 1713

-

Cadence演示面向PCI Express 5.0系统的SoC硅芯片2021-05-14 2800

-

求一种PCIe接口的视频采集解决方案2021-04-30 1402

-

泰克推出PCI Express® 5.0收发机和参考时钟解决方案2021-02-26 2597

-

怎么使用一个多点信号分配PCIe时钟?2019-09-26 2345

-

PCI Express电源和迷你卡解决方案2019-09-03 1752

-

PCI Express的市场趋势及相关应用2019-05-08 1259

-

PCI Express解决方案的介绍2018-11-29 3923

-

国外PCIE的书籍《pci express system architecture》2017-06-06 24012

-

LSI推出PCI Express固态存储解决方案样片2010-03-23 1155

-

如何进行PCI-Express的一致性测试和分析2009-04-08 4303

全部0条评论

快来发表一下你的评论吧 !