如何获得符合EMI标准的电源技巧

EMC/EMI设计

描述

在您的电源中很容易找到作为寄生元件的100fF电容器。您必须明白,只有处理好它们才能获得符合EMI标准的电源。

从开关节点到输入引线的少量寄生电容(100毫微微法拉)会让您无法满足电磁干扰(EMI)需求。那100fF电容器是什么样子的呢?在Digi-Key中,这种电容器不多。即使有,它们也会因寄生问题而提供宽泛的容差。

不过,在您的电源中很容易找到作为寄生元件的100fF电容器。只有处理好它们才能获得符合EMI标准的电源。

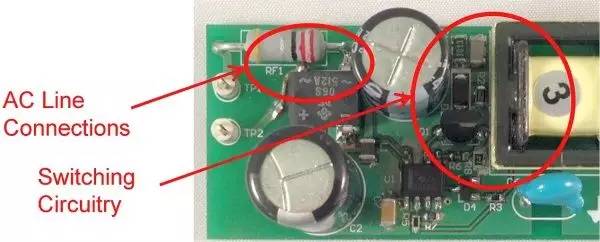

图1是这些非计划中电容的一个实例。图中的右侧是一个垂直安装的FET,所带的开关节点与钳位电路延伸至了图片的顶部。输入连接从左侧进入,到达距漏极连接1cm以内的位置。这就是故障点,在这里FET的开关电压波形可以绕过EMI滤波器耦合至输入。

图1. 开关节点与输入连接临近,会降低EMI性能

注意,漏极连接与输入引线之间有一些由输入电容器提供的屏蔽。该电容器的外壳连接至主接地,可为共模电流提供返回主接地的路径。如图2所示,这个微小的电容会导致电源EMI签名超出规范要求。

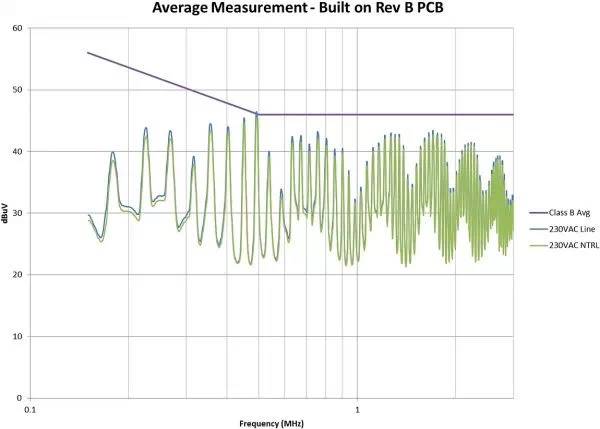

图2. 寄生漏极电容导致超出规范要求的EMI性能

这是一条令人关注的曲线,因为它反映出了几个问题:明显超出了规范要求的较低频率辐射、共模问题通常很明显的1MHz至2MHz组件,以及较高频率组件的衰减正弦(x)/x分布。

需要采取措施让辐射不超出规范。我们利用通用电容公式将其降低了:

C = ε ˙ A/d

我们无法改变电容率(ε),而且面积(A)也已经是最小的了。不过,我们可以改变间距(d)。如图3所示,我们将组件与输入的距离延长了3倍。最后,我们采用较大接地层增加了屏蔽。

图3. 这个修改后的布局不仅可增加间距,而且还可带来屏蔽性能

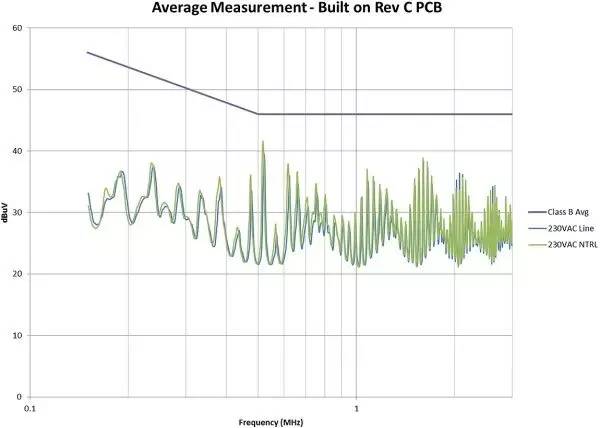

图4是修改后的效果图。我们在故障点位置为EMI规范获得了大约6dB的裕量。此外,我们还显著减少了总体EMI签名。所有这些改善都仅仅是因为布局的调整,并未改变电路。如果您的电路具有高电压开关并使用了屏蔽距离,您需要非常小心地对其进行控制。

图4. EMI性能通过屏蔽及增加的间距得到了改善

总之,来自离线开关电源开关节点的100fF电容会导致超出规范要求的EMI签名。这种电容量只需寄生元件便可轻松实现,例如对漏极连接进行路由,使其靠近输入引线。通常可通过改善间距或屏蔽来解决该问题。要想获得更大衰减,需要增加滤波或减缓电路波形。

编辑:黄飞

-

那些不得不知的电源技巧!2016-01-14 1662

-

如何处理好电源中的寄生电容才能获得符合EMI标准的电源2019-04-09 1960

-

电源中作为寄生元件的100fF电容器2022-08-04 881

-

小小的疏忽就能毁掉EMI性能2018-10-23 1519

-

如何处理好电源中的寄生电容获得符合EMI标准的电源?2019-05-14 2208

-

如何获得符合EMI的电源2019-10-18 2299

-

获得符合EMI标准电源的方法2020-10-29 1423

-

开关电源中使用100fF电容维持EMI性能的要点2021-10-21 3607

-

一个小小的疏忽就会毁掉EMI性能2017-11-15 875

-

怎么才能获得符合EMI标准的电源2018-05-06 7394

-

如何获得符合EMI标准的电源2020-08-31 1214

-

只有处理好它们才能获得符合EMI标准的电源2020-10-26 2717

-

寄生漏极电容导致超出规范要求的EMI性能2023-07-27 1011

-

开关电源的EMI/EMC测试标准2024-11-20 6893

全部0条评论

快来发表一下你的评论吧 !