DRAM的电容技术发展历程

描述

2006

Development of New TiN/ZrO2/Al2O3/ZrO2/TiN Capacitors Extendable to 45nm Generation DRAMs Replacing HfO2 based Dielectrics IEDM

从单层HfO薄膜过渡到堆叠结构,第一次提出ZAZ的结构,并在45nm工艺节点进行了可靠性验证。为DRAM电容介质提出了全新的研究方向。

通过控制温度来控制晶相,将非晶AlO、T相ZrO制作为新型介质薄膜。因为主要贡献点是EOT很低的新型薄膜,通过三个I_V曲线描述漏电性能,XRD表明晶相,C_V测算K值得到优越性能。最后还通过“浴缸图”、良率比较图等大数据证明其可靠性。

Tetragonal Phase Stabilization by Doping as an Enabler of Thermally Stable HfO2 based MIM and MIS Capacitors for sub 50nm Deep Trench DRAM IEDM

首次表明,通过四价(Si)和三价(Y,Gd)掺杂剂控制HfO2的结晶相,可以稳定其四方相,显著提高电容等效厚度(EOT)。(沟槽电容)、45nm工艺节点。

2007

Carbon / high-k Trench Capacitor for the 40nm DRAM Generation VLSI

奇梦达、trench,碳作高k电容电极、隔离层。40nm

韦博分布——龙老师擅长。

可以看作新思路。

2008

Al-Doped TiO2 Films with Ultralow Leakage Currents for Next Generation DRAM Capacitors ADVANCED MATERIALS

Al掺杂TiO2超低漏电流薄膜。内有XSP测试,有原理解释。可作为Si掺参考。

0.5 nm EOT low leakage ALD SrTiO3 on TiN MIM capacitors for DRAM applications IEDM

本文首次记录了在TiN底电极上用低温(250摄氏度)ALD沉积STO,通过改善其前驱材料和工艺,得到了低漏电的薄膜。

通过工艺设置Si-rich、Ti-rich、标准三种薄膜,得出Si-最佳的结果。还摸索出最佳退火温度。工艺创新,让最有潜力的材料可与便宜的TiN电极共同生长。对后续STO应用在DRAM中贡献很大。

2009

Scalability of TiN/HfAlO/TiN MIM DRAM Capacitor to 0.7-nm-EOT and Beyond IEDM

通过各个角度验证了HfO的优越性(然而现在主流并不用),主要是理论推导,teff-K、qφB0-K等。大量理论+少许实验,结论存疑,但能自洽。

2010

Enabling 3X nm DRAM: Record low leakage 0.4 nm EOT MIM capacitors with novel stack engineering IEDM

30nm,新型stackDRAM。本文运用了超薄Ru氧化工艺,在TIN上加了一层thin Ru改善了性能。主要是提出了不同的堆叠方式,各种材料的堆叠结构开始发展。

Recent Innovations in DRAM Manufacturing IEEE

4x节点开始上市,通过采用双层电容器、高k介质和提高源/漏等技术实现。

是一篇综述类文章,与电容关系不大,但可纵观产业。

Capacitors with an Equivalent Oxide Thickness of < 0.5 nm for Nanoscale Electronic Semiconductor Memory ADVANCED MATERIALS

新前驱体在TiN电极上形成了薄、均匀、密度更高的Ru和RuO层。金红石结构的tio2和al掺杂的tio2薄膜由于在二元氧化物中具有极高的介电常数,可能会填补ZAZ和srtio3 MIM电容器之间的空隙,其中都需RuO作为底电极。

还有一些对电极的工艺改良,可以一看。

Structure and property changes of ZrO2/Al2O3/ZrO2 laminate induced by low-temperature NH3 annealing applicable to metal–insulator–metal capacitor Thin Soild Films

对ZAZ进行480℃低温NH3退火。N确实可以加入到介质层板中,导致ZrO2层中出现四方向立方的相变和小晶粒。N化可减少杂质,改善形貌。

对ZAZ的工艺改进,可以研究下机理。

Theoretical Screening of Candidate Materials for DRAM Capacitors and Experimental Demonstration of a Cubic-Hafnia MIM Capacitor TED

采用TiN电极的立方HfO2是一种很有前途的DRAM候选材料。插入AlO层改善漏电。漏电机制由氧空位决定。

从漏电出发拉踩STO,提出相同EOT最小的漏电由HfO提供,在此基础上制备了al掺杂HfO2和TiN的MIM电容器。分析可借鉴。

A Novel Cylinder-Type MIM Capacitor in Porous Low-k Film (CAPL) for Embedded DRAM with Advanced CMOS Logics IEDM

CAPL,感觉是集成领域的,目前参考价值不大。

2011

Towards 1X DRAM: Improved leakage 0.4 nm EOT STO-based MIMcap and explanation of leakage reduction mechanism showing further potential VLSI

对0.4nmEOT的STO MIM 进行了改进,主要为了减少漏电,采用一种Ru/RuOx/TiOx/Sr-rich STO/TiN的结构。并得到结论,漏电是由STO中的氧空位缺陷引起的,RuO可以在结晶过程中改善消除甚至逆转电极附近的氧空位缺陷。

各种J-V图,能带原理分析图。

Advanced capacitor dielectrics: towards 2x nm DRAM IEEE

介绍富Sr (Sr/(Sr + Ti) ~ 62%)钛酸锶(STO)、金红石型TiO2等高级电容介质的介电常数均大于60的电学特性数据。

另提出了一种基于平面金属-绝缘体-金属(MIM)系统的实用电容模型。偏综述类

A High-Performance, High-Density 28nm eDRAM Technology with High-K/Metal-Gate IEDM

高K金属栅用于eDRAM,HKMG CMOS兼容(低热低充电过程)高k MIM电容,具有极低泄漏。研究T的,关联不大可以了解。

Improved EOT and leakage current for metal–insulator–metal capacitor stacks with rutile TiO2 Microelectronic Engineering

以RuO2/Ru为底电极,金红石TiO2为介质,TiN为上电极形成的MIMCAP结构。在TiO2原子层沉积(ALD)过程中,需要臭氧(O3)作为氧化剂,以获得金红石相(介电常数> 80),而用H2O得到锐钛矿型TiO2(介电常数40)。

2012

Reliability of SrRuO3/SrTiO3/SrRuO3 Stacks for DRAM Applications EDL

SrRuO3/SrTiO3/SrRuO3栈在DRAM应用中的可靠性研究,对比CET,电流与时间关系等,可靠性方面不失为高校研究的好方向。

The structural andelectrical characterization of a HfErOx dielectric for MIM capacitor DRAM applications Microelectronic Engineering

新材料HfErOx。稀土元素掺杂HfO2可以降低金属绝缘体硅(MIS)电容器[8]的漏电流,提高k值(Er掺杂浓度大概为15%)。

TEM表征、XRD确认、C-V、J-V性能分析,CET对比。值得研究。

2013

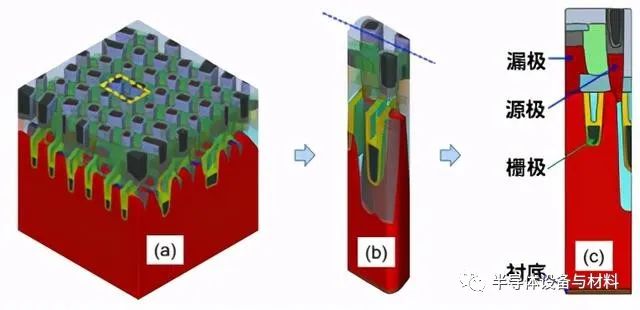

The Novel Stress Simulation Method for Contemporary DRAM Capacitor Arrays IEEE

富锶钛酸锶和金红石氧化钛薄膜的陷阱辅助泄漏中提取了有效电子隧穿质量,并与由假想能带结构第原理计算得到的理论值进行了比较。讨论了薄膜的最佳取向和化学计量学对隧道的影响。偏理论,可仔细研究。

Considerations for further scaling of metal– insulator–metal DRAM capacitors JVST

2014

Low leakage Ru-strontium titanate-Ru metal-insulator-metal capacitors for sub-20 nm technology node in dynamic random access memory APL

Ru/STO/Ru堆栈,通过控制Sr/Ti比和晶粒尺寸,采用非均相TiO2/STO基纳米层叠沉积和两步结晶退火,实现了MIMCAPs等效氧化层厚度、漏电流密度(Jg)和STO物理厚度的降尺度。

多步退火。

Leakage Control in 0.4-nm EOT Ru/SrTiOx/Ru Metal-Insulator-Metal Capacitors: Process Implications EDL

Ru/SrTiOx/Ru泄漏控制:工艺影响。上电极材料和沉积技术以及沉积后退火是控制上电极负偏压和正偏压泄漏的关键参数。没什么出众数据(?

2015

Sub-0.5 nm Equivalent Oxide Thickness Scaling for Si-Doped Zr1−xHfxO2 Thin Film without Using Noble Metal Electrode ACS

Si掺杂的ZHO体系分析!与研究方向高度重合!Si掺杂有助于稳定四方向,提高k值。

XRD验证表征、确定结构,Z与H比例改变,探究最佳。Hf的含量对器件k值也有很大的影响。注意本文表征解释部分。

20nm DRAM: A new beginning of another revolution IEDM

提出了蜂窝结构(HCS)和空气间隔技术。估计都是产业界在用的技术。主张不使用***生产。前言部分站在产业角度纵观,值得一读。

2016

Nonvolatile Random Access Memory and Energy Storage Based on Antiferroelectric Like Hysteresis in ZrO2 ADVANCED MATERIALS

反铁电随机存取存储器的概念证明,讲NRAM中ZrO的应用,注重极化角度,目前关系不大。

Conduction barrier offset engineering for DRAM capacitor scaling Solid-State Electronics

IPE检测,与漏电有关。描述ZAZ层的制作过程,给出详细的泄漏特性描述,表征结果和参数提取方法。

Low leakage ZrO2 based capacitors for sub 20 nm dynamic random access memory technology nodes JAP

将ZAZ层间材料由Al2O3改为SrO和顶部电极材料由TiN改为Pt。这两种方法结合得到的电容等效厚度值为0.47 。可以参考吧。

Extraction of the Defect Distributions in DRAM Capacitor Using I–V and C–V Sensitivity Maps EDL

利用I-V和C-V灵敏度图提取DRAM电容中的缺陷分布。灵敏图??

2017

Novel Approach for the Reduction of Leakage Current Characteristics of 20 nm DRAM Capacitors With ZrO2–Based High-k Dielectrics EDL

可通过去除电容外部杂质硼和氢,减少电容器形成后的热量预算,消除泄漏电流的退化,而不改变电容器的结构或材料。

提出了三种降低电容器漏电流退化的方法。

Investigation of ultrathin Pt/ZrO2eAl2O3eZrO2/TiN DRAM capacitors Schottky barrier height by internal photoemission spectroscopy Current Applied Physics

内发射光谱法研究超薄Pt/ZrO2eAl2O3eZrO2/TiN DRAM电容器的肖特基势垒高度,Pt/ZAZ/TiN叠层中Pt/ZAZ和ZAZ/TiN界面的SBH分别为2.77 eV和2.18 eV。上电极/氧化物和下电极/氧化物界面的SBH差异与Pt和TiN的功函数差异以及给定介质的亚隙缺陷态特征(密度和能量)有关。结合器件级的IPE实验分析和薄膜级的紫外光电子能谱和光谱椭偏分析,提出了带结构模型。

Doped Hf0.5Zr0.5O2 for high efficiency integrated supercapacitors APL

我们将10 nm厚的Hf0.5Zr0.5O2 (HZO)二元薄膜掺杂Al或Si (Al或Si掺杂HZO)。添加的掺杂剂提供了从铁电特性到反铁电特性的明显转变。

与课题关系密切。

2018

High-performance (EOT<0.4nm, Jg~10-7A/cm2) ALD-deposited RuSrTiO3 stack for next generations DRAM pillar capacitor IEDM

RuSrTiO3新型堆栈结构,数据图好看值得借鉴。

EDS测成分?

1-T Capacitorless DRAM Using Laterally Bandgap Engineered Si-Si:C Heterostructure Bipolar I-MOS for Improved Sensing Margin and Retention Time IEEE

电学特性,仿真。数字电路。

New Method for Reduction of the Capacitor Leakage Failure Rate Without Changing the Capacitor Structure or Materials in DRAM Mass Production TED

新方法降漏电(与2017类似)。减少B杂质。杂质运用原子探针层析技术测量。

电介质泄漏失效测试、电阻失效测试、可靠性结果也能通过。(20nm)

Simultaneous improvement of the dielectric constant and leakage currents of ZrO2 dielectrics by incorporating a highly valent Ta5+ element† JMC

ZrO2电介质加入高价Ta5+元素,由于Zr被Ta取代和VO的降低而引起的原子排列的变化增强了立方相的结晶度,使ZrO2薄膜的摩尔体积减小。

2019

Controlling the Electrical Characteristics of ZrO2/Al2O3/ ZrO2 Capacitors by Adopting a Ru Top Electrode Grown via Atomic Layer Deposition PSS

采用原子层沉积法生长Ru顶电极控制ZrO2/Al2O3/ ZrO2电容器的电特性。为应对ZAZ厚度减小后漏电的增加,将TE从TiN换成Ru。工艺详细。

Scaling the Equivalent Oxide Thickness by Employing a TiO2 Thin Film on a ZrO2–Al2O3-Based Dielectric for Further Scaling of Dynamic Random Access Memory PSS

新型结构ZAT,比传统ZAZ性能好。C-V、J-V都有进步。

Recent advances in the understanding of high-k dielectric materials deposited by atomic layer deposition for dynamic random-access memory capacitor applications JMR

就谈论和建议。电容材料方面的综述!!

A Sensitivity Map-Based Approach to Profile Defects in MIM Capacitors From I–V, C–V, and G–V Measurements TED

又是基于I-V、C-V、J-V方面的灵敏度图。

Influence of Etch Profiles on the Leakage Current and Capacitance of 3-D DRAM Storage Capacitors ISSN

刻蚀轮廓对三维DRAM存储电容器漏电流和电容的影响。仿真!可以仔细瞅瞅。

Trap-Assisted DRAM Row Hammer Effect EDL

Hammer效应。仿真!单电荷阱的三维TCAD模拟,我们发现了DRAM滚锤效应机理的直接证据。结果与之前报道的实验结果吻合良好。

Dielectric Enhancement of Atomic Layer-Deposited Al2O3/ZrO2/Al2O3 MIM Capacitors by Microwave Annealing NRL

ZAZ微波退火。1400 W、5 min的微波退火条件下,ZrO2的介电常数提高到41.9(提高了40%),衬底温度低于400℃,与线工艺的后端兼容。

2020

Double-Gate Junctionless 1T DRAM With Physical Barriers for Retention Improvement TED

双门无结1T DRAM与物理屏障的保留改进。对T的改善。

High-kHfxZr1-xO2 Ferroelectric Insulator by Utilizing High Pressure Anneal TED

HZO结构,高压退火。还有Z与H比例调节。

Anti-ferroelectric HfxZr1-xO2 Capacitors for High-density 3-D Embedded-DRAM IEDM

高密度三维嵌入式dram用反铁电HfxZr1-xO2电容器。P-V图的。

2021

105× Endurance Improvement of FE-HZO by an Innovative Rejuvenation Method for 1z Node NV-DRAM Applications VLSI

可靠性。铁电原理解释的透彻,亮点在于Pr的再生方法。

审核编辑 :李倩

-

通信直流开关电源产品的技术发展概述2010-06-24 3054

-

EDA技术从何而来?EDA技术发展历程2019-02-21 4170

-

封装天线技术发展历程回顾分析2019-07-17 3594

-

晶圆级三维封装技术发展2020-12-28 4457

-

光通信技术发展的趋势是什么2021-05-24 3240

-

高速球是什么?有什么技术发展趋势?2021-05-31 2027

-

汽车电子控制技术的发展历程及具体应用2021-08-30 4683

-

超级电容器技术发展与应用趋势分析2009-11-17 729

-

现代电容器产业的技术发展趋势2009-11-18 692

-

印制板制造技术发展50年的历程2006-04-16 991

-

中国铅酸蓄电池技术发展历程2009-10-29 2236

-

讲述Numonyx封装技术的发展历程2018-06-26 4057

-

长鑫存储副总裁披露DRAM技术发展现状和未来趋势2019-09-20 8698

-

数据存储技术发展历程简述2023-09-22 6143

-

铝电解电容技术发展与市场格局分析2025-06-23 1367

全部0条评论

快来发表一下你的评论吧 !