集总元件和分布元件描述

电子说

描述

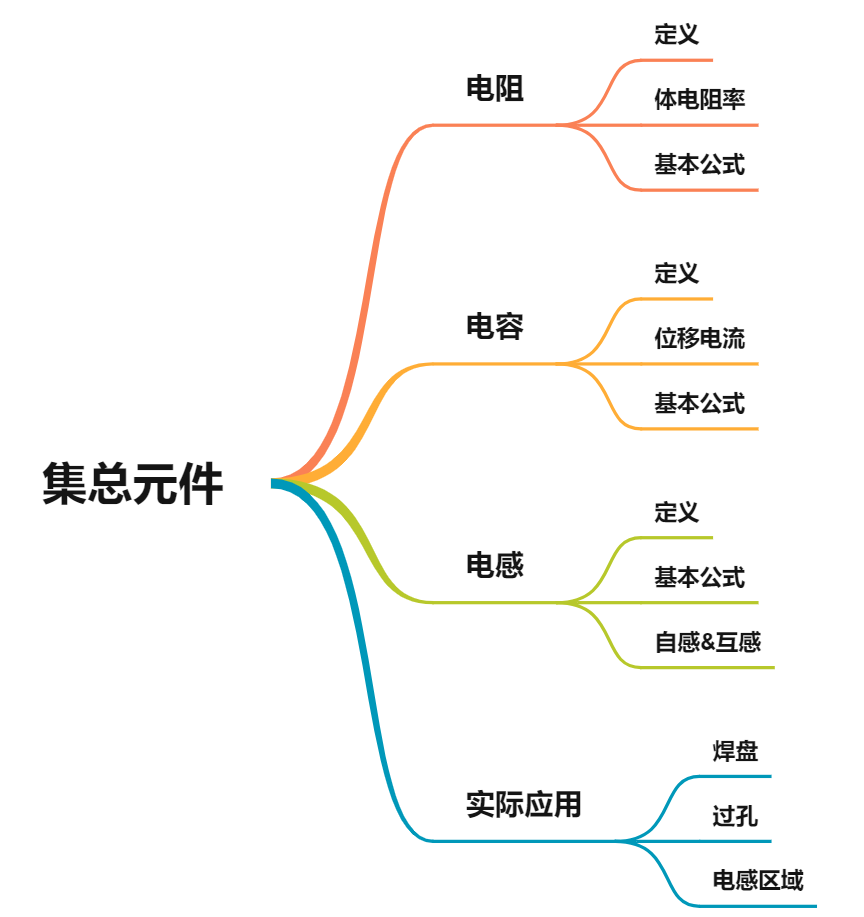

产品的设计中,研发选用很多无源器件,其中最为常用三大件:电阻、电容、电感。相对于分布元件(传输线),集总元件(电阻、电容、电感)是基于空间的点来做分析,信号完整性中的互连模型都是基于集总元件和分布元件来加以描述。

集总元件在硬件工程师看来,他们关注于其电气参数:电阻器(额定功率,负荷特性,温度系数等),电容器(额定电压,耐压值,频率特性等),电感器(额定电流,品质因数等)。

我们更关注于其对信号链路的影响,额外寄生参数(寄生电阻,寄生电容,寄生电感)的影响,也就是仿真中的参数提取。同时关注其能量损耗(电能变为热能,电磁能变为热能等),对应协议中相关损耗标准。

01

电阻

导体对电流阻碍作用的大小。

电阻(Resistor,通常用“R”表示)是一个物理量,电阻是导体本身的一种性质。不同的导体,电阻一般不同,因为导体的电阻随长度、截面大小、温度和导体成分的不同而改变。所以,电阻没有一个固定值。电阻的单位是欧姆,符号为Ω。

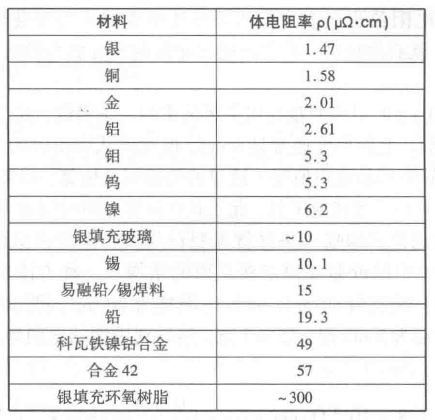

体电阻率:

不同于电阻会随着物理尺寸(长度,宽度等)而改变,体电阻率与其无关。

体电阻率是一种材料特性,材料不同,体电阻率也不同。

体电阻率和电导率互为倒数。

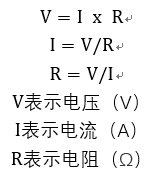

电阻作用是分压和分流,是基于欧姆定律:

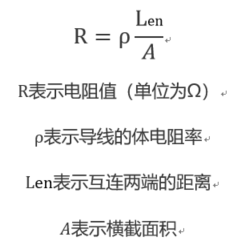

集总元件的电阻,将版图设计中的走线(铜)两点之间看成一个电阻,假设这段走线的横截面恒定,近似公式:

02

电容

两个导体,中间夹一层绝缘介质(包括空气),给定一定电压下的自由电荷量。

电容(Capacitance,通常用“C”表示)表示容纳电荷多少的物理量。电容量的大小和几何结构以及周边介质的材料属性有关。

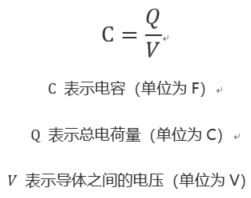

电容的基本公式:

需要注意的是:电压值增大,异性相吸的规则,电荷量也会增大,所以比值一般保持不变。

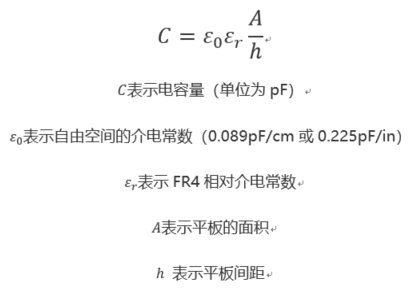

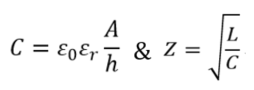

我们更多关注电容公式,如下:

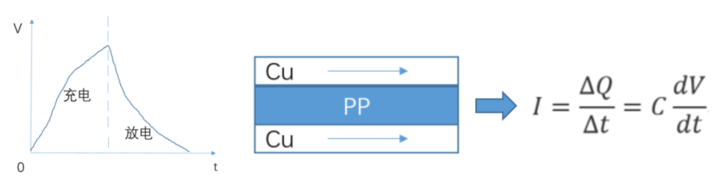

实际的版设计中,电容功能的充放电关注比较少。更多关注的是:PCB像平行电容,信号在铜线中流过,电流的变化,特别是交流信号,随着频率的不同,引起的串扰和信号完整性相关的问题。

需要注意的是,因为中间的绝缘介质,引出了“位移电流”的概念,这个不同于传导电流。

电容除了电源储能,信号滤波等作用。电源的轨道塌陷的解决之道,便是在电源和地之间多加去耦电容,降低PDN的阻抗,来保证电源压降的需求。

03

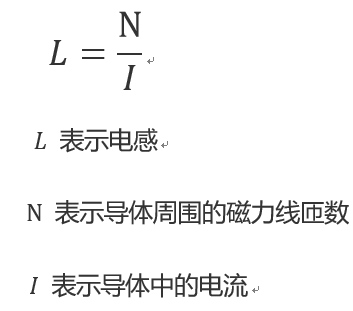

电感

流过单位安培电流时,环绕在导体周围的磁力线匝数。

当电流通过线圈后,在线圈中形成磁场感应,感应磁场又会产生感应电流来抵制通过线圈中的电流。

电感(Inductor,通常用“L”表示),闭合回路的一种属性,即周围环形磁力线圈。

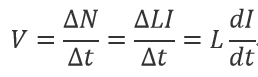

电感的电流发生变化,电感两端就会产生电压,也称之为感应电动势,该电压产生的感应电流会阻碍原电流的变化。

这个由电流变化产生的感应电压是我们需要避免的,它产生大多数电磁干扰源(串扰,地弹等)。

自感和互感

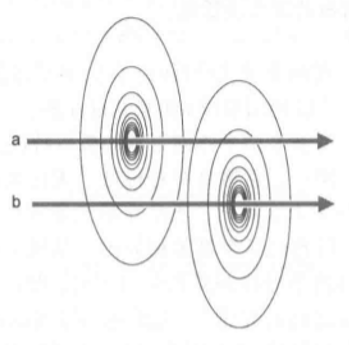

一个导体流过单位电流,产生自身的磁力线圈匝数,是自感。

产生在别的导体周围的磁力线圈匝数,是互感。

04

实际应用

在实际过程中,集总元件本身不需要太多关注,更多关注于寄生电阻,寄生电容,寄生电感等。

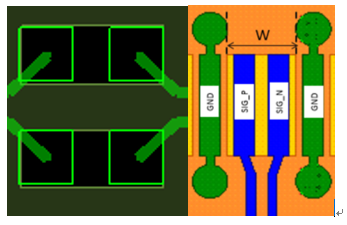

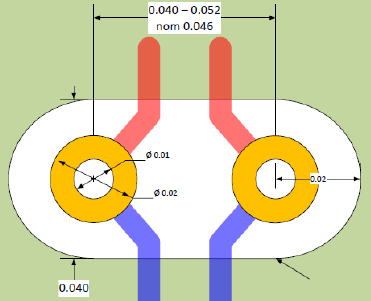

器件的引脚,亦或是焊锡丝的影响(体电阻率:铜是1.58,锡是10.1)等所引起的阻抗突变,在版图设计中的处理,更多是对焊盘的优化。

焊盘面积比走线大,面积增大,电容变大,阻抗变小。焊盘下方挖空,距离变大,电容变小,阻抗变大。通过这样的处理,来抑制阻抗的突变,降低反射,尽量保证阻抗匹配。

版图设计中,8Gbps以上速率的信号过孔,就是加大焊盘到铜皮的间距,来改变寄生电容的大小,同时尽量保持过孔寄生电感,来管控过孔阻抗。

当然,过孔的残桩也是需要考虑的主要因素,这里就不做展开了。

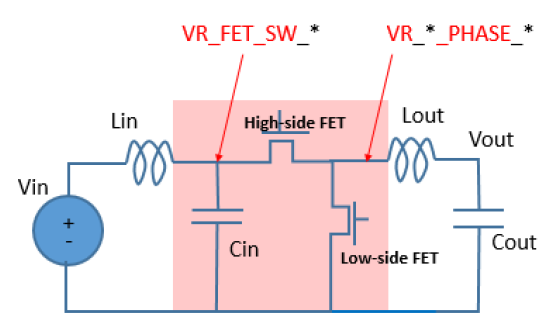

版图设计中,设计指导也会提出HSD(高速信号差分线)走线路径尽量远离电感,距离上每个产品会有不同的要求。很多产品都是15mils起。

特别是开关电源的输入,输出电感区域,是禁布区域。

很多设计规则都是考虑其信号完整性,设计规则就是规避这些风险,规则的优化和判定正是信号完整性工程师职责所在。所以信号完整性工程不仅仅是仿真工程师,更是产品的PCB板级信号质量的优化工程师。

审核编辑:刘清

-

如何在Momentum模拟中使用集总元件2019-02-21 3045

-

功率变换器中的功率磁性元件分布参数2021-11-09 3455

-

MAX2240 2.45GHz非线性PA输出匹配集总元件2008-08-19 1450

-

什么是集总参数和分布参数2010-03-05 21992

-

数字设计基础知识--集总与分布系统2010-05-28 2890

-

红米手机元件原理图2015-10-29 2029

-

iphone6 4.7元件分布图2015-11-26 4730

-

iphone 4S 元件分布图2015-12-23 1585

-

元件知识集1集合一2016-03-18 899

-

诺基亚3100主板元件分布图2016-03-22 1690

-

iPhone6 元件分布图2016-04-26 4636

-

PCB布局规范之PCB元件分布要衡量元件与定位孔间距等问题2018-06-11 10659

-

iphone6主板元件分布图2022-11-28 5209

-

基于IPD技术的集总元件低通滤波器设计方案(下)2023-10-25 2260

-

集总电路元件及其特性2024-08-12 530

全部0条评论

快来发表一下你的评论吧 !