深入开源处理器内部,RISC-V技术分析

处理器/DSP

描述

译者 君谦 在此特别鸣谢!

本文摘自《开源处理器内部—RISC-V简介》一书,其经过格式化和轻编辑,内容和页面布局达到Elektor期刊的标准。FPGA技术与(V)HDL的结合在电子专家中很受欢迎,RISC-V为专业应用增加了开源途径。在本文中,我们测试了一些在Elektor的“Alchitry”系列的Lattice和 Xilinx FPGA板上运行的示例应用程序的并行比较以及结果。

过去,在 FPGA工具流中设置项目是一项艰巨的任务。随着技术趋于成熟,这种设置变得简单许多。在这里的例子中大部分工作已经完成。值得注意的是,大型项目或最大限度利用FPGA功能的项目不可避免地会变得复杂得多。

具体到Lattice和 Xilinx,除了为项目选择合适的FPGA目标之外,只需要在工具中链接到3个文件。在这种简化的方法中,所有的项目文件都需要在同一个目录中。建议读者阅读FPGA的Alchitry教程软件安装和项目设置,这里仅仅涉及基本的细节。

1 Lattice( Alchitry Cu)注意事项

该开发板使用的FPGA需要 Lattice iCEcube2软件。这是一款成熟的产品,没有太多花哨的功能,但有几点需要注意:

① 确保使用正确的设备选项设置项目。Alchitry Cu使用CB132封装中的 iCE4O系列HX8K器件,所有I/O组都使用3.3V电源。

② 只有yrv_alchitry.v文件需要作为设计文件输入,因为所有其他设计文件将自动以正确的顺序包含在内。

③ 对于合成工具﹐需确保选择Lattice LSE合成。逻辑综合期间不需要约束文件。

④综合完成后,在运行其余工具之前,yrv_ alchitry.pc/pin约束文件和 timing. sdc时序约束文件需要被链接。各种日志文件中会有许多警告,但是它们都没有重要到需要采取任何措施。

2 Xilinx ( Alchitry Au和Au+)注意事项

在这些开发板上使用的FPGA需要Xilinx Vivado软件。这是一个非常复杂的产品,本项目仅使用这个软件的一小部分功能。这里有一些要记住的事情:

① 只有yrv_alchitry.v文件需要作为设计文件输入。

② 只有yrv_alchitry.mdc约束文件是必需的。该文件包含引脚约束、时序约束以及编程电压规格。

③ 正确的器件选项是用于Au板的xc7a35tftg256 -i和用于Au+板的xc7aiootftgzS6 -i。

在这些设备的日志文件中有更多的警告﹐同样,它们都没有重要到需要采取任何措施。

3 FPGA结果

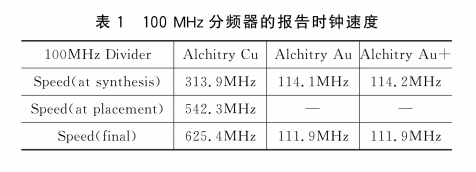

该示例项目已在所有3种目标FPGA开发板上实施,具体结果将在以下部分介绍。在对一些结果进行并列比较时是很有趣的。表1显示了100 MHz分频器的报告时钟速度。

100 MHz分频器设计用于最大速度,触发器之间只有一级逻辑,这意味着这个结果应该代表技术的能力。如果报道属实﹐点阵设备的速度令人印象深刻。最有趣的是,随着逻辑综合到逻辑布局再到最终布线结果,报告的速度变得更快,而且可能更准确。虽然最终的性能比最初的预期值要好,但是相差两倍是不理想的,因为这可能导致错误地将其作为一个不可行的项目而放弃。

Xilinx工具不会在逻辑布局时给出单独的速度估计,但逻辑综合和最终结果之间报告的速度几乎相同。从设计师的角度来看,这是首选。

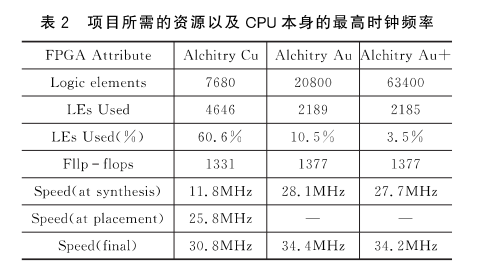

表2显示了项目所需的资源以及CPU本身的最大时钟频率。这些结果不包括RISC-V特权架构中的任何64位计数器。

表2的第二行说明了为什么比较FPGA结果会很复杂。从表中可以看出,Xilinx实现所需的资源不到1attice实现所需资源的一半﹐但是Xilinx逻辑无件包含的逻辑比点阵逻辑元件多得多。此外,Xilinx设计使用了 Lattice设备所没有的专用DSP模块。

查看所用逻辑元件的百分比,可以发现3种FPGA之间的尺寸差异。yrv_mcu设计需要一半多一点的 Lattice器件,是大约1/10的中端Xilinx器件,不到大型Xilinx 的1/20。这种用法符合不同开发板的成本要求。

正如预期的那样,设计所需的触发器数量在3种FPGA中是相似的,确切地说,数量更多的是逻辑综合工具的功能而不是其他。逻辑综合工具将复制触发器以提高性能或简化布线。

速度行显示3种 FPGA提供大致相同的性能,这有点令人惊讶,因为Lattice FPGA 不包含Xilinx实施中使用的专用DSP模块。

4 关于Alchitry Cu

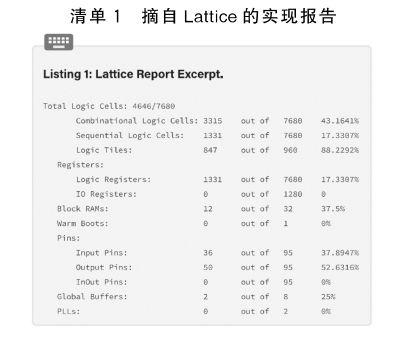

清单1直接摘自 Lattice 的实现报告,显示了资源利用的细节。图1取自Lattice Floorplanner工具的屏幕截图﹐显示了分布在器件中的逻辑元件的使用情况。这种分布在整个设备中相当均匀,尽管总体使用率只有60%左右。

5 关于Alchitry Au

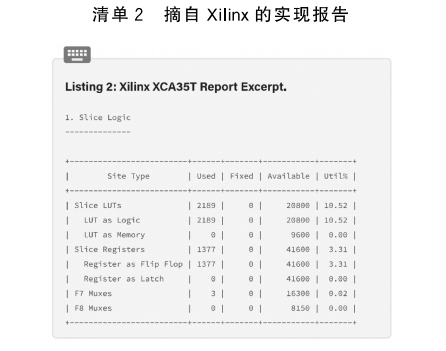

清单2直接摘自Xilinx实现报告,显示了资源利用的细节。完整的Xilinx报告要大得多,涵盖了FPGA中所有可用的专用硬件。

图2为Xilinx Floorplanner 工具的屏幕截图,显示了分布在整个器件中的逻辑元件的使用情况,以及专用逻辑模块如何分布在整个器件中。放置工具似乎总是从设备的左下角开始。

6 关于Alchitry Au+

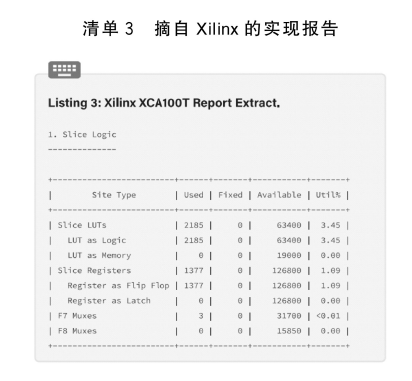

清单3也直接摘自Xilinx的实现报告﹐显示了资源利用的细节。请注意,两台Xilinx设备使用的资源数量几乎相同。图3也取自Xilinx Floorplanner工具的屏幕截图。有趣的是,尽管该FPGA包含3倍数量的逻辑元件,但本例所需的总面积与第一个 Xilinx实施中几乎相同。

7 硬件编程

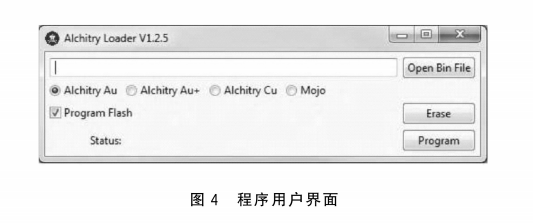

使用Alchitry Loader 程序时,将 FPGA 比特流下载到Alchitry开发板非常简单。该独立程序作为Alchitry的一部分,自动安装Alchitry提供的实验室软件。图4显示了这个程序的用户界面。

对用于加载FPGA的开发板上的闪存器件进行编程也很简单,只需指定位流文件、选择目标板,然后单击“编程”按钮。

默认情况下,程序会查找.bin类型的比特流文件,这是iCEcube2软件使用的默认设置。Vivado 软件生成. bit类型的比特流文件。因此,在加载Xilinx 比特流文件时要记住这一点。

编辑:黄飞

-

从零开始写RISC-V处理器2022-03-17 3282

-

risc-v在人工智能图像处理应用前景分析2024-09-28 1097

-

关于RISC-V和开源处理器的一些解读2020-06-22 2249

-

学习RISC-V入门 基于RISC-V架构的开源处理器及SoC研究2020-07-27 4366

-

RISC-V是什么?如何去设计RISC-V处理器?2021-06-18 2736

-

RISC-V开源处理器核介绍2021-07-23 2414

-

阿里平头哥宣布开源玄铁RISC-V系列处理器2021-10-20 2461

-

RISC-V系列处理器的相关资料推荐2022-02-28 1384

-

从零开始写RISC-V处理器之一 二 前言 绪论2022-08-22 5164

-

RISC-V和开源处理器之间是什么关系?2023-03-09 835

-

读书分享会 | 玄铁RISC-V处理器入门与实战电子书免费下载!2023-04-12 1207

-

UltraSoC宣布推出业界首款支持RISC-V的处理器跟踪技术2017-07-03 1098

-

RISC-V是通用RISC处理器还是可定制的处理器?2020-11-17 4520

-

商业级RISC-V 64位高性能处理器开源了?!2021-10-19 1999

-

平头哥宣布开源玄铁RISC-V系列处理器2021-12-08 1223

全部0条评论

快来发表一下你的评论吧 !