瑞萨RH850 FCL、FDL和EEL库的配置和使用

电子说

描述

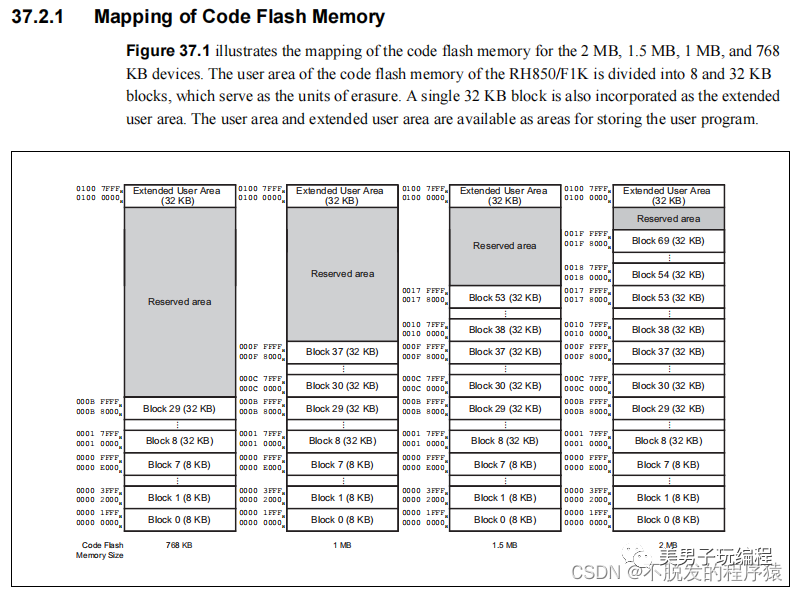

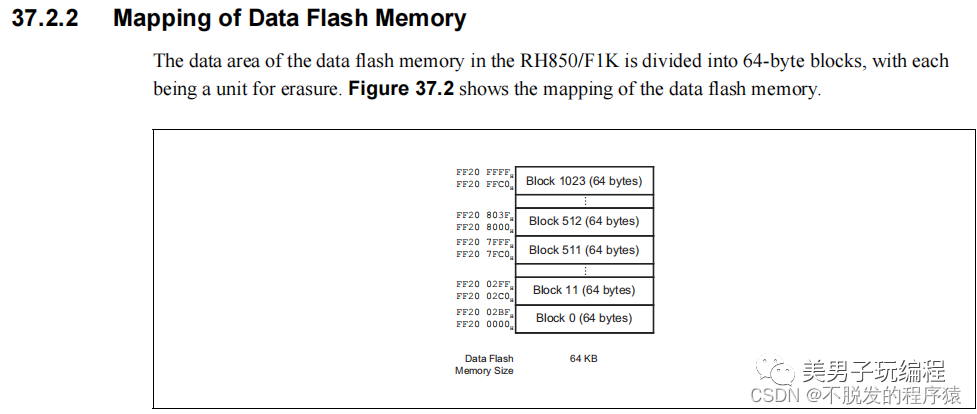

瑞萨RH850 Flash中有两种存储类型:Mapping of Code Flash Memory和Mapping of Data Flash Memory。

Mapping of Code Flash Memory存储代码,Mapping of Data Flash Memory存储数据。

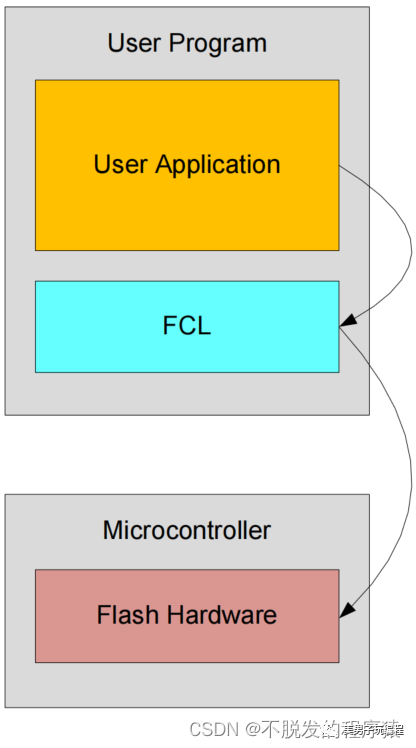

瑞萨车规级MCU操作Flash没有直接提供寄存器接口,需要安装官方提供的库文件,有三种形式:

FCL:程序存储区仿真库,可使用此库访问程序存储区,一般用于程序自升级操作;

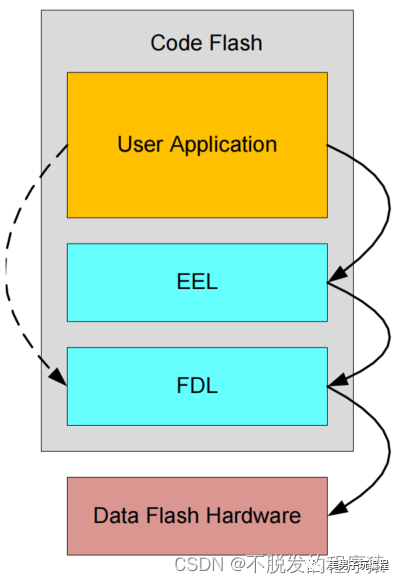

FDL:数据存储区仿真库,可通过此库操作数据区,需要人为定义地址和数据长度,占用Flash空间比EEL略少,但占用RAM大;

EEL:EEPROM仿真库,可使用此库来访问数据内存区,该方法类似于访问外部EEPROM,使用此库时,不用管理对数据区闪存写和擦除操作,其占用Flash容量大,需配合FDL库来操作。

1FCL库

1.1、配置FCL库

第1步:下载FCL库(点击阅读原文查看)。

FCL库官网地址

RH850 FCL库与用户手册地址

第2步:安装FCL库。

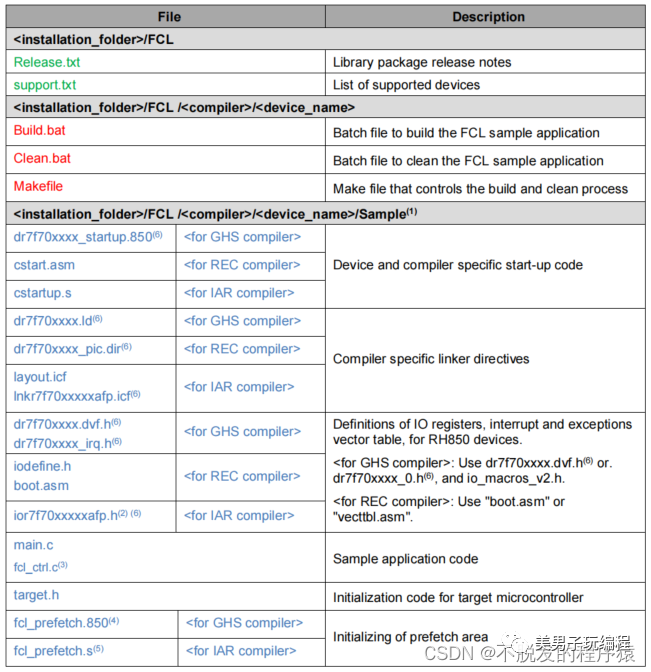

安装完成后可见官方库文件和用户使用文件两部分:

文件系统结构说明如下所示:

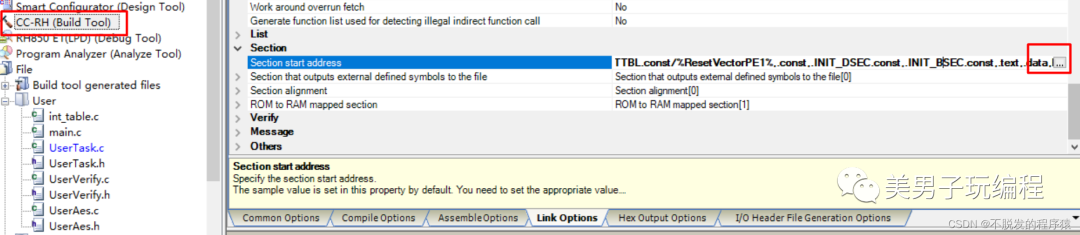

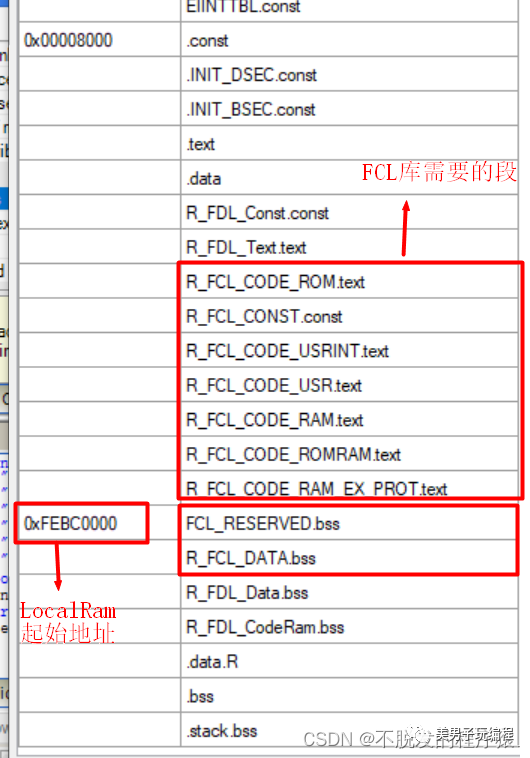

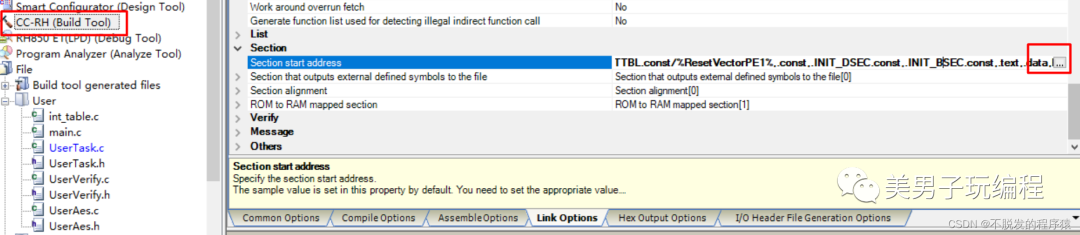

第3步:将官方库文件和对应的用户使用文件添加到自己的工程后,在CS+工程中的添加FCL需要的代码段,如下图所示:

注意:

在这些代码段中请不要插入其他段;

FCL_RESERVED.bss段:在RAM中存放FCL库运行的代码,即复制上面代码段的内容到此RAM中。如果定义了R_FCL_HANDLER_CALL_USER,则用户代码R_FCL_CODE_USER.text也在RAM中运行。在实际应用中定义FCL_RESERVED预留的大小,大小必须包含该库代码量和用户代码量(如果定义了R_FCL_HANDLER_CALL_USER );

/* This array reserves the copy area in the device RAM */ #define FCL_RAM_EXECUTION_AREA_SIZE 0x8000 R_FCL_NOINIT uint8_t FCL_Copy_area[FCL_RAM_EXECUTION_AREA_SIZE];

R_FCL_DATA.bss:FCL内部运行数据段;

在CS+环境下,FCL编译后会出现3个对齐失配警告,请忽略。

W0561322:Section alignment mismatch : "R_FCL_CODE_USR.text" W0561322:Section alignment mismatch : "R_FCL_CODE_RAM.text" W0561322:Section alignment mismatch : "R_FCL_CODE_ROMRAM.text"

第4步:修改fcl_cfg.h文件。

#define R_FCL_COMMAND_EXECUTION_MODE R_FCL_HANDLER_CALL_USER //修改成 #define R_FCL_COMMAND_EXECUTION_MODE R_FCL_HANDLER_CALL_INTERNAL

R_FCL_HANDLER_CALL_USER(user mode):user模式,用户代码运行在RAM区,在自编程命令执行期间,可以运行用户代码,用户可以轮询库的运行状态。需要消耗一定的RAM空间;

R_FCL_HANDLER_CALL_INTERNAL (internal mode):internal模式,不需要轮询库的状态,在自编程命令执行期间没有状态值的返回,直到命令执行结束。消耗RAM空间小。

第5步:修改fcl_descriptor.h文件。

#define FCL_CPU_FREQUENCY_MHZ (240) /*!< CPU frequency in MHz */

#define FCL_AUTHENTICATION_ID {0xFFFFFFFF,

0xFFFFFFFF,

0xFFFFFFFF,

0xFFFFFFFF} /*!< 128Bit authentication ID */

#define FCL_RAM_ADDRESS 0xFEBC0000 /*!< RAM address range blocked for FCL */

FCL_CPU_FREQUENCY_MHZ:CPU工作频率配置,请不要在库的运行期间改变CPU的工作频率,如果需要改变,改完后必须重新初始化FCL库;

FCL_AUTHENTICATION_ID:如果设备设置了ID验证码,需要提供相应的ID码,在FCL初始阶段需要验证ID,如果ID验证不通过,不能成功执行FCL命令;

FCL_RAM_ADDRESS:根据相应的设备配置RAM起始位。

第6步:修改r_fcl_types.h文件。

#define R_FCL_NO_BFA_SWITCH

#if ((defined R_FCL_MIRROR_FCU_COPY) && (defined R_FCL_NO_FCU_COPY))

#error "r_fcl_types.h: Invalid define for support device macro"

#elif ((defined R_FCL_MIRROR_FCU_COPY) && (defined R_FCL_NO_BFA_SWITCH))

#error "r_fcl_types.h: Invalid define for support device macro"

#elif ((defined R_FCL_NO_FCU_COPY) && (defined R_FCL_NO_BFA_SWITCH))

#error "r_fcl_types.h: Invalid define for support device macro"

#elif (defined R_FCL_MIRROR_FCU_COPY)

#define R_FCL_INNER_NO_BFA_SWITCH

#elif (defined R_FCL_NO_FCU_COPY)

#define R_FCL_INNER_NO_FCU_COPY

#elif (defined R_FCL_NO_BFA_SWITCH)

#define R_FCL_INNER_NO_BFA_SWITCH

#define R_FCL_INNER_NO_FCU_COPY

#endif

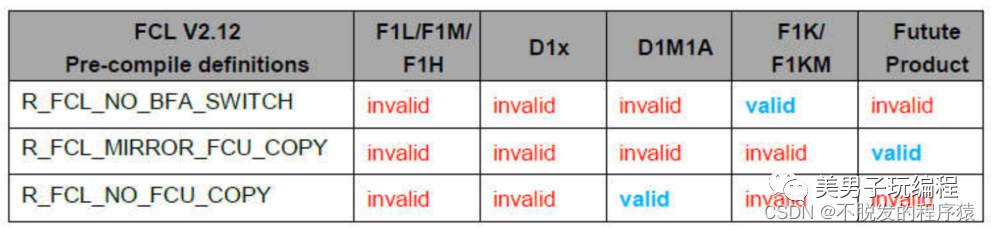

在FCL V2.12版本中增加了R_FCL_NO_FCU_COPY、R_FCL_MIRROR_FCU_COPY和R_FCL_NO_BFA_SWITCH预编译配置选项。

在执行FCL库环境准备命令时,为了从MCU内部固件读取数据,需要开关CodeFlash几次。有些设备需要更少的开关来完成这个准备工作,需要定义R_FCL_NO_BFA_SWITCH 宏;

R_FCL_NO_BFA_SWITCH 宏和R_FCL_NO_FCU_COPY、R_FCL_MIRROR_FCU_COPY 不能同时被定义。

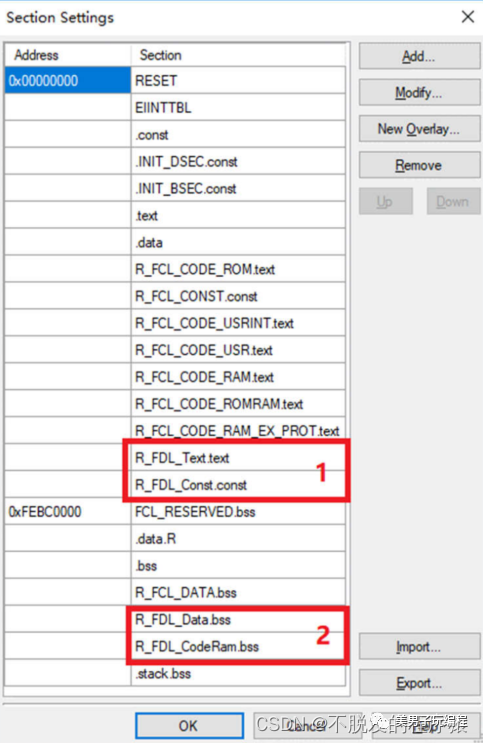

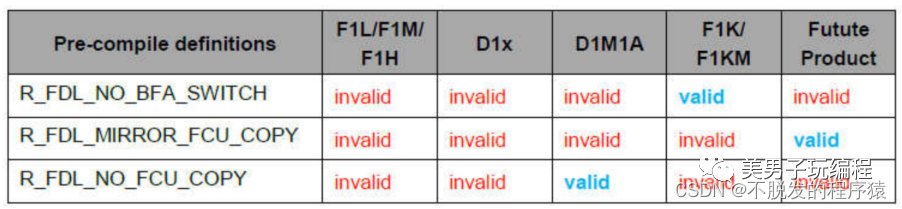

预编译目标设备所需的定义如下表所示:

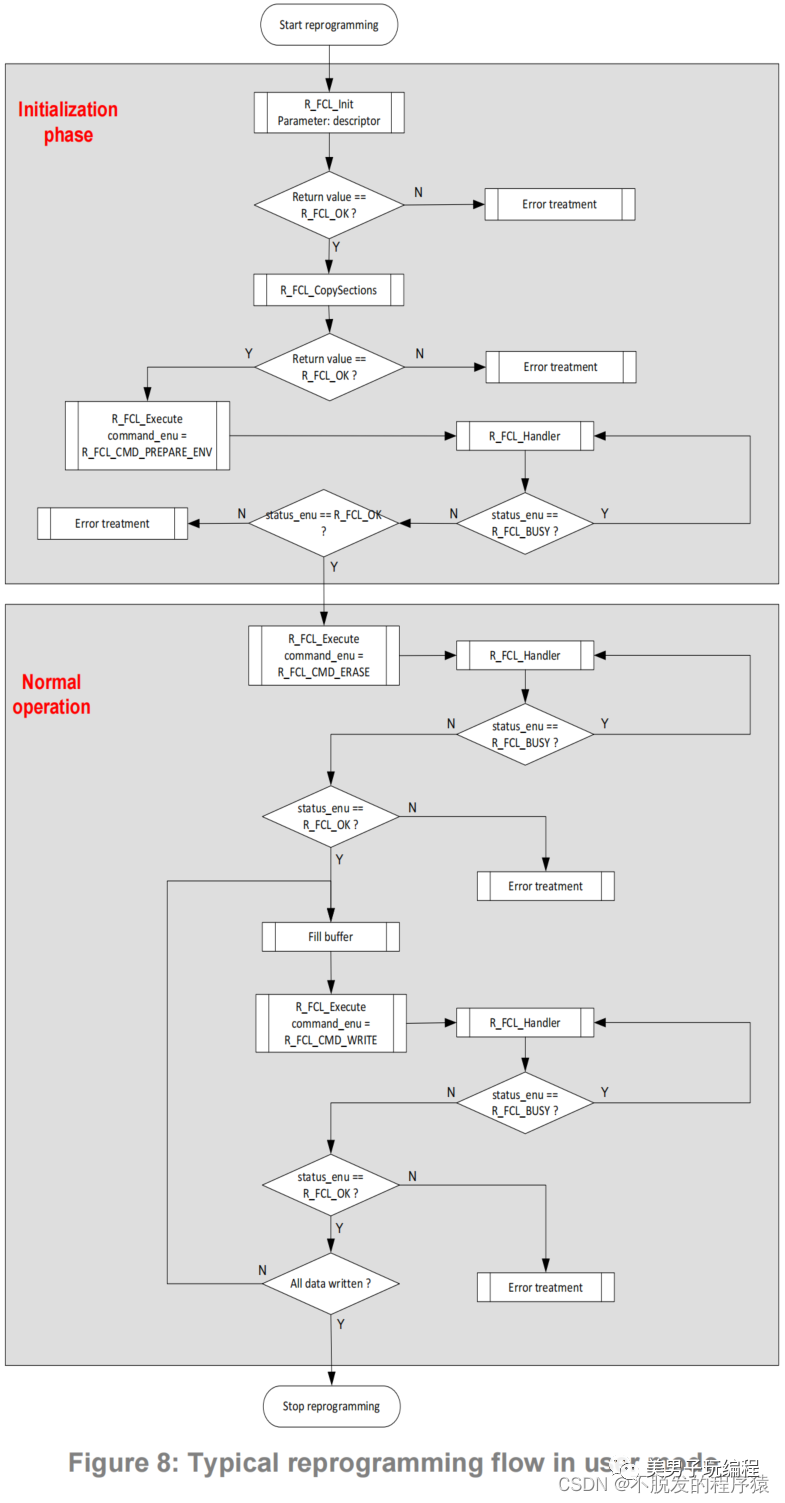

1.2、使用FCL库

2FDL库

2.1、配置FDL库

第1步:下载FDL库(点击阅读原文查看)。

FDL库官网地址:https://www.renesas.cn/cn/en/software-tool/data-flash-libraries#download

RH850 FDL库与用户手册地址:https://www.renesas.cn/cn/en/products/microcontrollers-microprocessors/rh850-automotive-mcus/rh850f1km-s4-high-end-automotive-microcontrollers-ideal-body-applications/design-support#hardware_tools

第2步:安装FDL库。

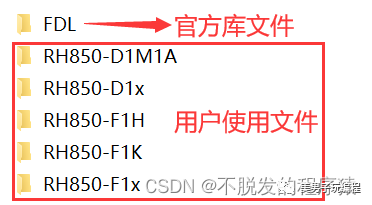

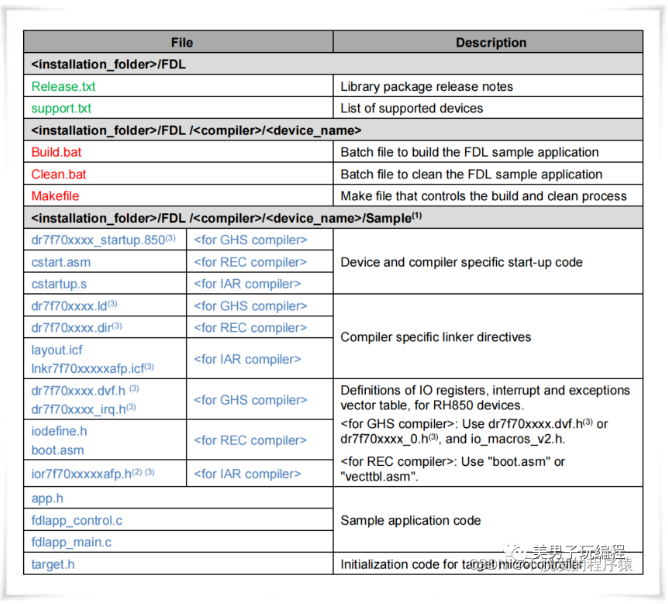

安装完成后可见官方库文件和用户使用文件两部分:

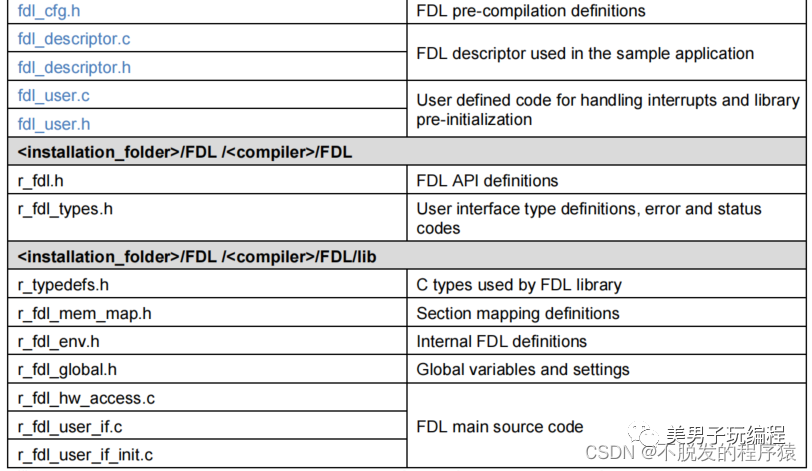

第3步:将官方库文件和对应的用户使用文件添加到自己的工程后,在CS+工程中的添加FDL需要的代码段,如下图所示:

注意:

FDL库的代码段请按照如图样例1设置,位置可以任意,但不要插在FCL代码的中间;

R_FDL_Data.bss:FCL内部运行变量数据段;

R_FDL_CodeRam.bss: 在执行FDL环境准备期间,Code Flash不可用,需要从RAM中运行代码。

第4步:修改r_fdl.h文件。

#define R_FDL_NO_BFA_SWITCH

/* Global compiler definition */

#if ((defined R_FDL_MIRROR_FCU_COPY) && (defined R_FDL_NO_FCU_COPY))

#error "r_fdl.h: Invalid define for support device macro"

#elif ((defined R_FDL_MIRROR_FCU_COPY) && (defined R_FDL_NO_BFA_SWITCH))

#error "r_fdl.h: Invalid define for support device macro"

#elif ((defined R_FDL_NO_FCU_COPY) && (defined R_FDL_NO_BFA_SWITCH))

#error "r_fdl.h: Invalid define for support device macro"

#elif (defined R_FDL_MIRROR_FCU_COPY)

#define R_FDL_INNER_NO_BFA_SWITCH

#elif (defined R_FDL_NO_FCU_COPY)

#define R_FDL_INNER_NO_FCU_COPY

#elif (defined R_FDL_NO_BFA_SWITCH)

#define R_FDL_INNER_NO_BFA_SWITCH

#define R_FDL_INNER_NO_FCU_COPY

#endif

在FDL V2.12版本中增加了R_FDL_NO_FCU_COPY, R_FDL_MIRROR_FCU_COPY和R_FDL_NO_BFA_SWITCH预编译配置选项。

在执行FDL库初始化时,为了从MCU内部拷贝固件,需要在固件区和用户区来回切换几次,需要定义宏R_FDL_NO_BFA_SWITCH 。有些设备不需要拷贝固件(比如RH850/D1M1A),需要定义R_FDL_NO_FCU_COPY宏。

不要同时定义R_FDL_NO_BFA_SWITCH和R_FDL_NO_FCU_COPY, R_FDL_MIRROR_FCU_COPY 。

预编译目标设备所需的定义如下表所示:

第5步:修改fdl_descriptor.h文件。

/* The Flash programming hardware is provided with a clock, derived from the CPU subsystem frequency. Check that

the frequency is correct as this has an impact on the programming quality and performance! */

#define CPU_FREQUENCY_MHZ (240) /**< CPU frequency in MHz */

/*****************************************************************************************************************

* Important definitions for run-time configuration of the FDL:

* - EEL/FDL Pool -

*****************************************************************************************************************/

/* The physical erase unit of the Data Flash is 64Byte.

The Renesas EEL works with a ring buffer consisting of ring buffer (virtual) blocks that merge a certain number

of physical blocks.

E.g. virtual block size of 2kB equals 32 physical blocks of 64Bytes --> EEL_VIRTUALBLOCKSIZE = 32

virtual block size of 4kB equals 64 physical blocks of 64Bytes --> EEL_VIRTUALBLOCKSIZE = 64

Note: If the Renesas EEL is not used, an alignment is not necessary "EEL_VIRTUALBLOCKSIZE" need not be defined

and the pools start and size definitions can be set free to the application needs */

#define EEL_VIRTUALBLOCKSIZE (64u)

#define FDL_POOL_SIZE (16u * EEL_VIRTUALBLOCKSIZE) /**< Number of Data Flash blocks, accessible by

the FDL. Typically it is the complete

no. of available Data Flash blocks */

#define EEL_POOL_START (1u * EEL_VIRTUALBLOCKSIZE) /**< 1st block of the EEL pool */

#define EEL_POOL_SIZE (6u * EEL_VIRTUALBLOCKSIZE) /**< no. of blocks for the EEL pool */

CPU_FREQUENCY_MHZ:CPU工作频率配置,请不要在库的运行期间改变CPU的工作频率,如果需要改变,改变后必须重新初始化FDL库;

EEL_VIRTUALBLOCKSIZE虚拟块定:Data Flash物理块的大小为64Bytes,在EEL(EE2PROM Emulation Library)库中,需要合并一定数量的物理块虚拟成一个虚拟块作为EEL的缓冲区,用户可以根据实际应用定义虚拟块的大小;

如果没有使用EEL,设EEL_VIRTUALBLOCKSIZE = 0。如果使用EEL,例如要定义2KB的虚拟块,则需要32块64B的物理块组成,那么设EEL_VIRTUALBLOCKSIZE = 32。

FDL_POOL_SIZE :设备Data Flash的物理块的数量;

EEL_POOL_START、EEL_POOL_SIZE:EEL池的起始块和大小定义。

如果没有使用EEL,设EEL_POOL_START = 0, EEL_POOL_SIZE = 0;

如果使用EEL,例如,EEL_POOL_START = 0u * EEL_VIRTUALBLOCKSIZE、EEL_POOL_SIZE = 5 * EEL_VIRTUALBLOCKSIZE。

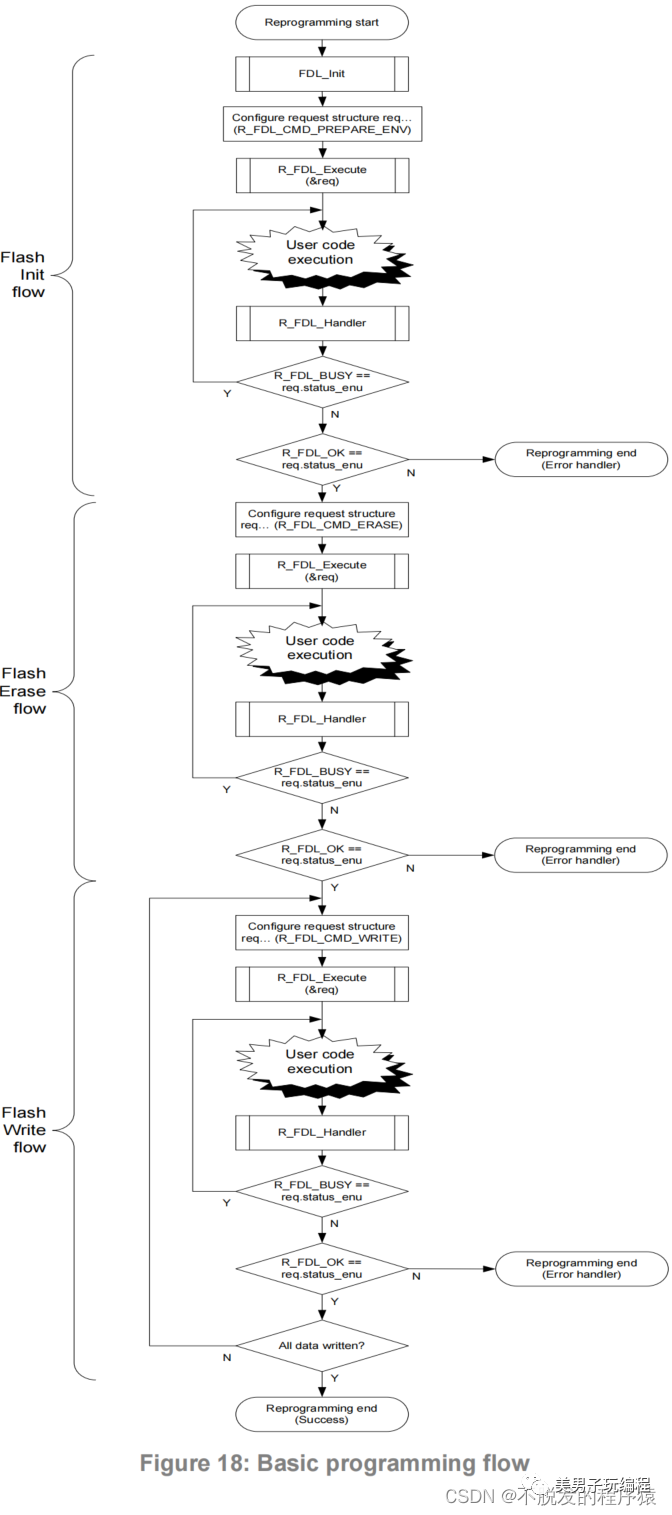

2.2、使用FDL库

3EEL库

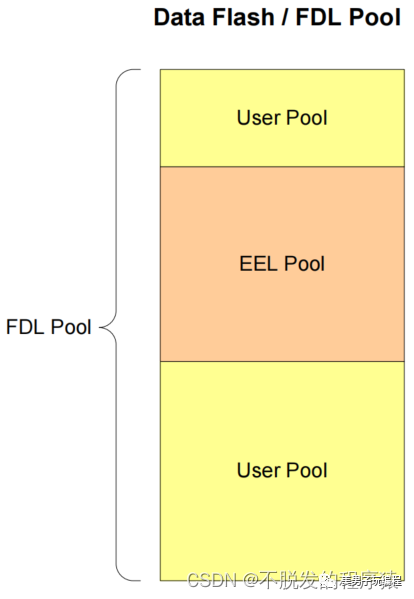

FDL和EEL都是操作Data Flash Memory,EEL依托于FDL,在FDL库中已经讲解了使用EEL的方法。EEL和FDL关系如下图所示:

EEL PooL:EEL Pool为EEL提供存储数据和管理信息;

User PooL:所有不是EEL Pool分配的FDL Pool空间都可由用户应用程序自由使用,因此称为User PooL。

审核编辑:汤梓红

-

IAR借助在瑞萨RH850/U2A MCU MCAL支持,加速汽车软件开发2025-09-05 1032

-

RH850智能配置器e²studio用户指南2024-01-30 547

-

rh850是什么芯片?2023-08-15 5835

-

瑞萨RH850 R7F7010693 谁能破解2023-04-22 2241

-

RH850 智能配置器用户指南:CS+2023-03-16 663

-

瑞萨RH850P1M-C芯片或者RH850P系列谁用过,用什么配置软件啊?2023-01-18 1928

-

RH850 智能配置器用户指南:IAREW、MULTI2023-01-09 776

-

如何配置***编译器使其可以结合瑞萨E1仿真器对RH850进行仿真调试?2022-02-16 1728

-

瑞萨RH850F1x开发环境的搭建方法2022-01-27 2198

-

结合GHS MULTI使用瑞萨E1仿真器实现对瑞萨RH850单片机的仿真调试2021-12-20 1888

-

RH850/F1L用户手册的CAN接口部分介绍2021-12-09 4480

-

瑞萨推出汽车电子应用的新RH850系列微控制器2012-03-12 2307

全部0条评论

快来发表一下你的评论吧 !