人工智能会改变EDA吗?

电子说

描述

近年来,人工智能(AI)与机器学习 (ML) 已经在诸多应用领域取得了突破。而在传统的半导体领域,研究者们也探索了基于机器学习的芯片设计新方法。这些新算法通常会最先反映在芯片设计工具上,也就是我们常说的EDA工具。因此,这一研究方向通常可以被称为ML for hardware design,或者ML for EDA(严格来说前者的范围更大一些)。有时也称做智能化的EDA算法或者智能的IC设计方法。 本文将介绍ML for EDA这一EDA领域的热门研究方向。这一方向涉及到机器学习,数据结构与算法,电路设计与制造等基础知识,是典型的交叉研究方向。我们将从EDA的背景知识开始,介绍什么是ML for EDA, 为什么我们研究ML for EDA,该研究方向早期一些代表性的工作,当前商业化的进程,其他相关的研究方向,以及ML for EDA可能面临的挑战。

01 什么是EDA? – EDA与芯片设计基础

芯片在我们的生活中无处不在。芯片的设计与实现涉及一个复杂的流程。以数字芯片为例,假设设计团队从已经完成的Verilog/VHDL代码出发,标准设计流程至少还要包括逻辑综合(logic synthesis),布局规划 (floorplan),时钟树综合(CTS),布局布线(placement & routing)等步骤。除此之外我们还需要进行大量的仿真和验证工作。在这个过程中,工程师需要权衡功耗,频率,面积等多个设计目标,同时还要确保制造出的芯片将正确运行各种功能。另外随着摩尔定律的进展,当下大规模的芯片已经可以包含超过 100 亿个晶体管。考虑到这种流程与设计的复杂性,几乎所有设计团队都需要商业EDA工具来辅助完成整个芯片设计。因此,如果我们把整个半导体产业比作一座金矿,EDA工具则也许可以被看做挖矿的铲子。在美国频繁限制半导体出口的当下,本身市值并不大的EDA产业越来越为人们所重视。

EDA的全称为Electronic Design Automation,即电子设计自动化。经过几十年的发展,EDA工具已经被用于芯片设计与制造流程的方方面面。EDA工具的质量将会影响最终芯片的质量(功耗,频率,面积)以及设计效率(产品上市时间)。因此,EDA算法研究者的目标通常至少包括两方面,一是芯片优化效果(功耗,频率,面积),二是EDA工具本身的效率(总耗时=工具单次运行时间* 使用该工具的次数)。 这里我们强调了EDA工具的使用次数,因为芯片设计不是一次完成的。通常工程师需要多次迭代各个设计步骤直至达成设计目标。每一次迭代,工程师可以修改工具参数或者芯片设计,并重新运行EDA工具,以期更好的芯片效果。对于大规模的芯片设计,仅执行部分设计流程每次即可花费数天至数周时间。因此,迭代次数越多,花费在EDA工具上的时间越多,最终流片以及产品上市日期就会越晚。后文将会介绍,很多ML for EDA工作的原理就是减少迭代次数,尽快让芯片质量收敛到设计目标。

02 什么是ML for EDA?– 预测与优化

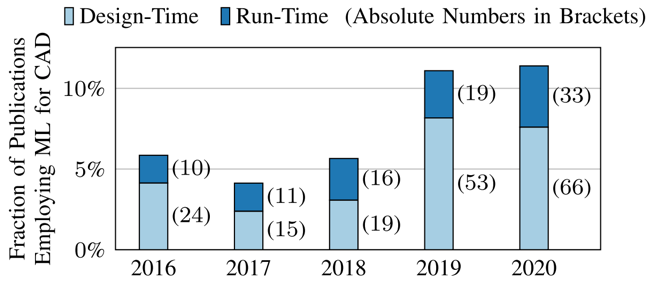

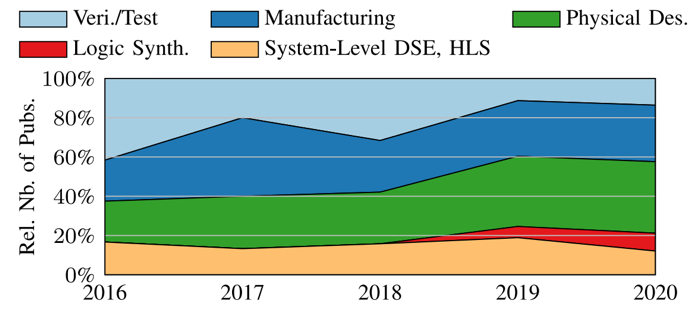

近年来,我们看到越来越多的ML for EDA方向的探索。如下图 [1] 所统计,发表在代表性EDA会议(DAC, ICCAD,ASP-DAC, ...)与期刊(TCAD)的相关工作数量逐年增加。

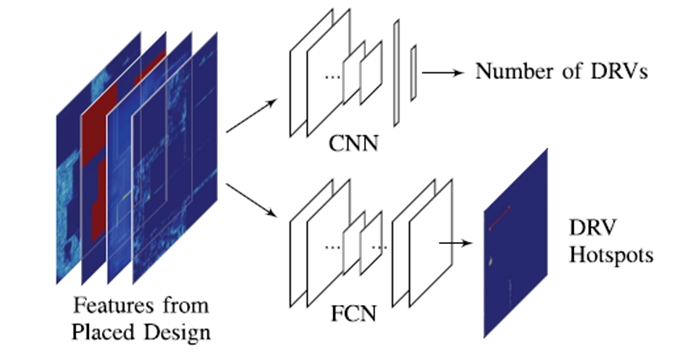

图1 历年发表的ML for EDA论文数量呈增加趋势 [1] 这些ML for EDA的方法在芯片设计流程中的作用大体可以分为预测(prediction)与优化(optimization)两大方面。下面我们分别举例来介绍这两类应用。 预测类工作通常使用ML模型对芯片优化的最终目标进行早期快速预测。利用ML模型的预测,设计师可以减少对耗时的EDA工具的使用,而直接预测EDA工具运行后的大致效果。基于ML预测,设计者可以及时调整设计参数。换句话说,ML模型通过快速预测EDA工具的行为,减少了运行EDA工具的次数。 一个典型的预测类工作例子就是,使用CNN模型在芯片绕线之前对(绕线后将会产生的)DRC热点(hotspot)进行提前预测 [2]。DRC热点指的是绕线后违反设计规则的区域。通过预测,EDA工具可以提前设法修改布局,避免未来阶段将会产生的DRC热点。这个工作可以类比于用CNN进行图像分类或者语义分割,其中芯片版图类似于图片,而需要预测的DRC热点位置类似于图片上需要分割的区块。

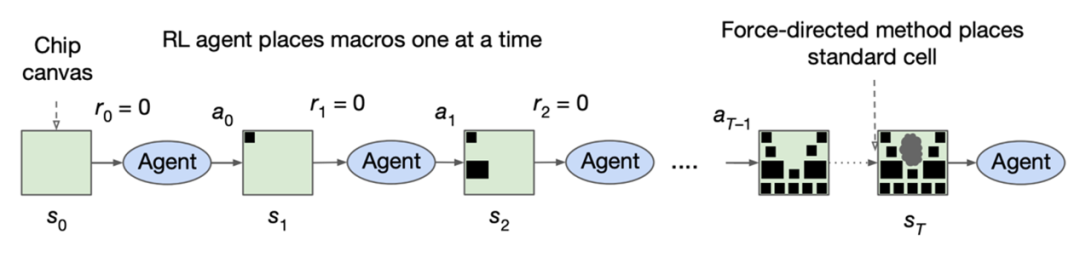

图2 预测类方法举例:使用CNN对DRC热点进行预测 [2] 相比于预测类工作,优化类工作需要做得更多。这里说的优化是一种比较宽泛的概念,指的是直接解决一些EDA问题。事实上大量EDA问题本质都是对于芯片在一定约束下的优化问题,而很多传统EDA算法是大家多年积累的(对这些问题的)优秀启发式解法。那么优化类ML方法追求的是比传统EDA算法更优或者更快的解法。这个解法可以帮助生成真实精确的芯片设计结果。 一个典型的优化类例子就是谷歌使用强化学习(Reinforcement Learning)进行macro 摆放(placement)[3]。通过强化学习算法,这个工作可以类比于AlphaGo进行围棋落子,其中芯片版图类似于围棋棋盘,而每一个macro元件的摆放位置类似于围棋每次最佳的落子位置。

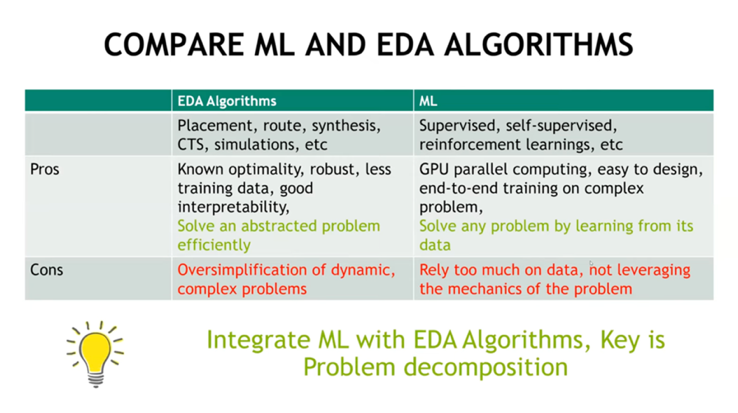

图3 优化类方法举例:使用强化学习进行macro摆放 [3] 按照这种不太严格的分类方式,预测类ML方法能够减少EDA算法的使用次数,从而提高芯片设计效率。而优化类ML方法能够帮助生成更快或更好的设计。如果想要完全取代某些传统EDA算法,我们需要的是优化类方法。当然像布局布线这样包括百万元件的大规模优化问题,想直接取代传统EDA方法是困难的。目前我们看到更多的是ML方法融入EDA框架,起到重要的辅助性作用 [4]。

图4 EDA和ML方法的比较:应该将ML融入EDA方法 [4]

03 为什么研究ML for EDA?

在深入介绍其他工作之前,一个需要回答的问题是,为什么我们要研究ML for EDA?换句话说,ML for EDA相比传统EDA算法有什么核心优势吗?这里尝试提供一种简单化的解释 [5]。

如背景中介绍,设计流程分为多个阶段。在大部分阶段,EDA工具很难直接去优化最终的设计目标,因为最终的设计目标只有在整个流程走完之后才会确定。于是EDA工具只能对最终的设计目标进行一个粗略估计。举例来说,布局(placement)算法可能会优化总线长(HPWL)与拥塞(congestion),但这个优化目标这并不总能反映最终的设计目标(最终芯片的功耗,频率,面积,DRC热点,等等)。 因此,除非每次都走完漫长的设计流程,不然前期的EDA工具并不能准确知道自己的解是否够好。为了保证设计收敛,一种策略是使用保守的早期估计,以给后期阶段留足余地(margin)。但这显然会牺牲芯片质量。另一种策略是不断调整参数进行反复多次迭代,以期获得更好的芯片质量。而这非常依赖专业设计师的经验,并且会花费大量设计时间。 ML for EDA算法的特点是它是由数据驱动的方法。通过学习已有的设计数据,早期使用ML预测可以获得更准确的最终优化目标,作为重要的早期反馈(early feedback)。于是预测类ML方法打通了不同设计阶段之前的障碍。而对于优化类ML方法,强化学习类型的方法通过探索巨大的设计空间,有可能获得比传统启发式算法更优的解。另外,一些ML方法可以学到工程师的优化经验,减少了对工程师经验的依赖。最后,ML方法在预测时通常非常快,所以如果不是规模太大,ML方法通常在运行速度上比传统方法会有数量级上的优势。

04 代表性的ML for EDA研究工作

事实上ML for EDA的工作远远不止前文介绍的两个例子。而这些工作可以通过多种方法进行分类。

如果我们根据ML应用的阶段或步骤分类,ML已经被研究者尝试用于绝大部分设计阶段。根据相关文章的总结 [1],应用ML模型的阶段可以包括1. 高阶综合(HLS)与设计空间搜索(DSE),2. 逻辑综合,3. 物理设计(从布局规划到布线),4. 光刻与制造,5. 验证与测试。除开数字电路之外,一些ML研究也对模拟电路的布局布线有一些尝试。

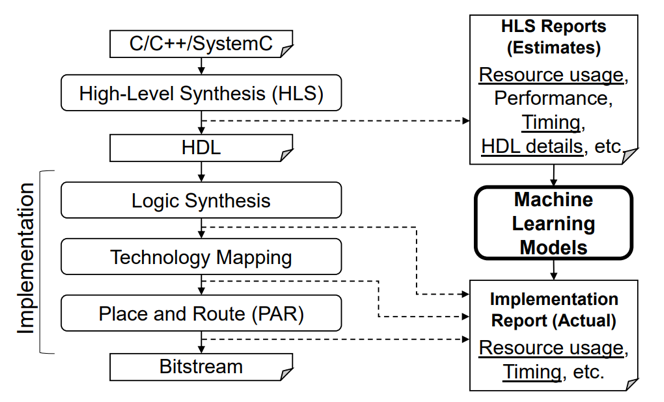

图5 历年应用在不同设计阶段的ML for EDA论文比例 [1] 如果我们根据ML预测或优化的目标分类,ML已经被研究者尝试用于大部分芯片优化目标,包括但不限于1.功耗(power),2.频率与延迟(delay or slack),3.面积与线长,4.拥塞(congestion)与规则检查(DRC),5.电压降(IR drop)与串扰(crosstalk), 6. 可制造性(Manufacturability)。 以下尝试简单列举一些具体的ML for EDA工作。篇幅所限,显然难以穷尽。因此同类型里尽量列举较早期且较高引用的工作。对于更新更完整的ML for EDA工作总结,读者可以参考论文 [1] 或视频 [4]。 对于FPGA平台,在高阶综合(HLS)阶段,有工作训练ML模型来预测最终的FPGA资源的利用率以及是否时序收敛 [6]。其中预测的FPGA资源包括RAM,FF,LUT和DSP等。ML模型是MLP或XGBoost。ML模型的输入,输出,使用阶段如下图所示。

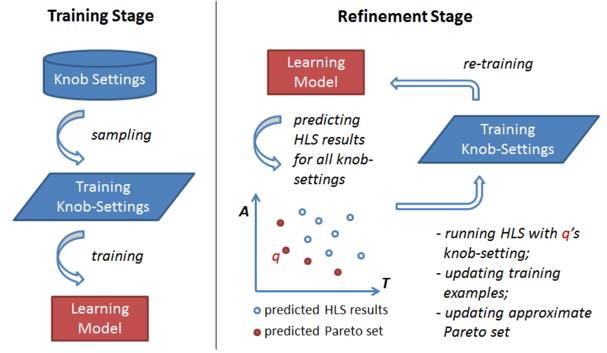

图6 HLS阶段对FPGA 资源利用率进行预测 [6] 同样在HLS阶段,ML可以进行设计空间探索(DSE)[7]。基本的方法就是用ML模型的预测结果指导每一次采样,然后根据采样结果重新训练ML模型,反复循环直至采样的设计获得足够好的结果。这里用到的ML模型是随机森林(RF)。这类探索任务也并不仅限于高阶综合。例如热门的用ML对EDA工具调参问题也属于相似的空间搜索任务。

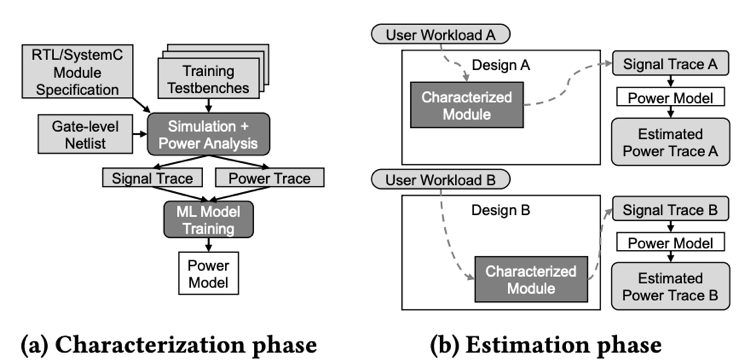

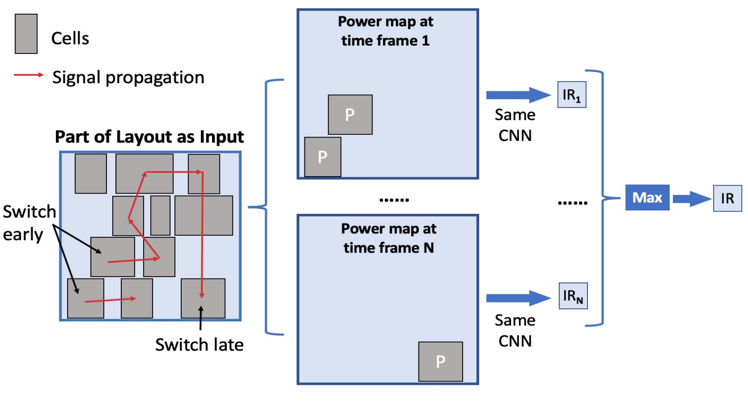

图七 用ML(随机森林)进行设计空间探索(DSE)[7] 在RTL阶段,ML可以用于对逻辑综合后的功耗进行快速估计 [8]。换句话说,ML模型在设计早期进行快速功耗模拟。ML模型的输入是芯片每个周期所有RTL信号的翻转值(1代表信号翻转,0代表在该周期信号不变),而输出是芯片每个周期的总功耗。选取这个输入是因为芯片的动态功耗与逻辑门的翻转率正相关。这个工作 [1] 尝试了包括线性回归,PCA降维,CNN的各类基础ML模型。

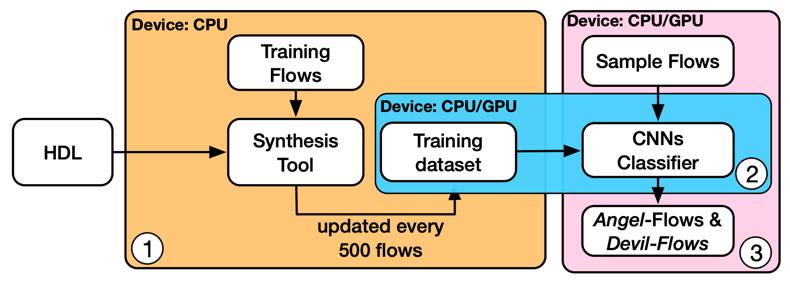

图八 用ML模型(CNN或线性模型)来模拟每周期的芯片功耗 [8] 在逻辑综合阶段,ML模型可以用于对逻辑综合这一步骤的流程进行选择 [9]。这里ML模型被训练来预测最适合当前芯片设计的synthesis transformation的组合。该工作把各种transformation的组合方式编码成二维矩阵,然后用CNN模型来进行处理,预测它们属于是好流程还是坏流程。

图9 用ML(CNN模型)选择合适的逻辑综合流程 [9] 在物理设计(从布局规划到布线)阶段,一开始提到的macro摆放和DRC热点预测两个例子都属于这个阶段的工作。另外一个例子是对芯片上的电压降(IR drop)分布进行预测 [10]。类似于之前的例子,CNN模型可以预测IR drop过高的热点(hotspot)。这里模型的输入是瞬时的功耗分布。需要预测的IR drop与区域内的瞬时的功耗成正相关。

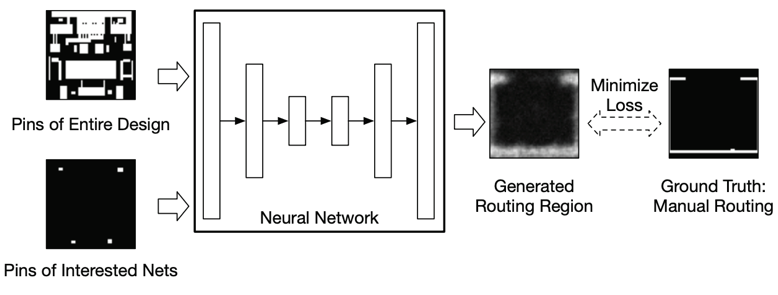

图10 用ML(CNN模型)预测电压降(IR drop)热点 [10] 除了以上这些用于数字电路的工作,对于模拟电路的探索也非常多。一个例子是直接使用ML生成对模拟电路绕线的指导(guidance) [11]。这里使用的ML模型是变分自编码器(VAE)。这个VAE模型的输入来源于模拟电路完成布局后,绕线之前的版图。

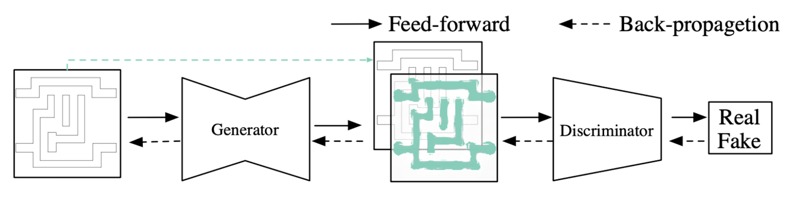

图11 使用ML(VAE模型)辅助模拟电路绕线 [11] 设计完成后,为了进行芯片制造,需要生成***使用的掩膜(mask)。对于先进制程,在掩膜生成的过程中,为了在晶圆上得到和设计相同的图形,光学邻近校正(OPC)是一个重要步骤。ML可以用于进行OPC [12]。这个工作使用生成对抗网络(GAN)来快速生成OPC后的掩膜。

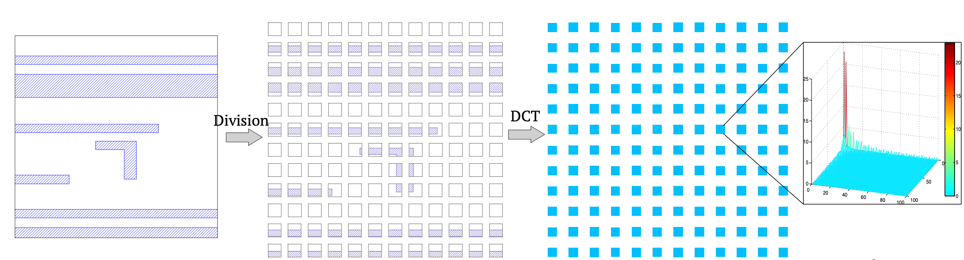

图12 使用ML(GAN模型)进行光学邻近校正(OPC)过程 [12] 另外为了提高制造良率(yield),需要进行光刻(lithography)热点(hotspot)检测。光刻热点指的是制造后可能会出现短路或断路的区域。ML可以用于预测光刻热点 [13]。这个工作对每一块输入的芯片区域先进行离散余弦变换(DCT),然后使用CNN模型来判断该区域是否为光刻热点。

图13 用ML(CNN模型)对光刻(lithography)热点检测 [13]

05 代表性的ML for EDA商业探索

除了学术界的探索,在工业界,EDA公司和芯片设计公司也对ML for EDA的方向表现出了很大兴趣。两大EDA公司Cadence和Synopsys已经推出了融合了一些ML算法的商业产品。

例如Cadence公司的物理设计工具Innovus在新版本中已经里面集成了一些机器学习工具,比如说在布线(routing)前提供对(布线后)时序的更准确估计。这个ML功能似乎获得了一些不错的评价 [14]。另外之前有报道Cadence集成的sign-off工具Project Virtus(Voltus + Tempus)也使用了ML [15]。更有影响力的是Cadence的Cerebus工具,通过基于强化学习的ML模型来调整RTL-to-GDSII的设计流程,减少对人工设计师的依赖 [16]。不过作为相关从业人员,我们很难了解这个产品的技术细节,例如这里的强化学习算法是如何迁移到不同的芯片设计的。 类似的,Synopsys也在更早推出了DSO.ai工具,也是用强化学习的方法自动优化设计流程 [17]。Synopsys的PrimeTime ECO工具也使用了ML模型。另外曾经的Mentor Graphics(现Siemens)也推出过使用基于ML预测的光学邻近效应修正(OPC)工具。 除了EDA公司之外,谷歌和英伟达的研究团队也积极探索了ML for EDA方向。这些是更偏研究性的工作。具体可以参考谷歌Jeff Dean和英伟达Bill Dally的相关主题演讲。 而在国内,受美国半导体政策影响,近年来不少优秀的国产EDA初创公司涌现。一些公司也开始探索了ML在EDA领域的应用。例如某国内公司最近发布了基于机器学习技术与布局规划工具,应该是将类似前文提到的谷歌macro摆放算法[1]实现了产品落地。个人认为这是一个比较有挑战性的任务。

06 其他与ML for EDA相关的研究

除去以上介绍到的工作,还有一些热点研究方向也经常被大家归类到ML for EDA的研究当中。但严格来说,个人认为这些方向也许不能完全属于狭义的ML for EDA的范畴。

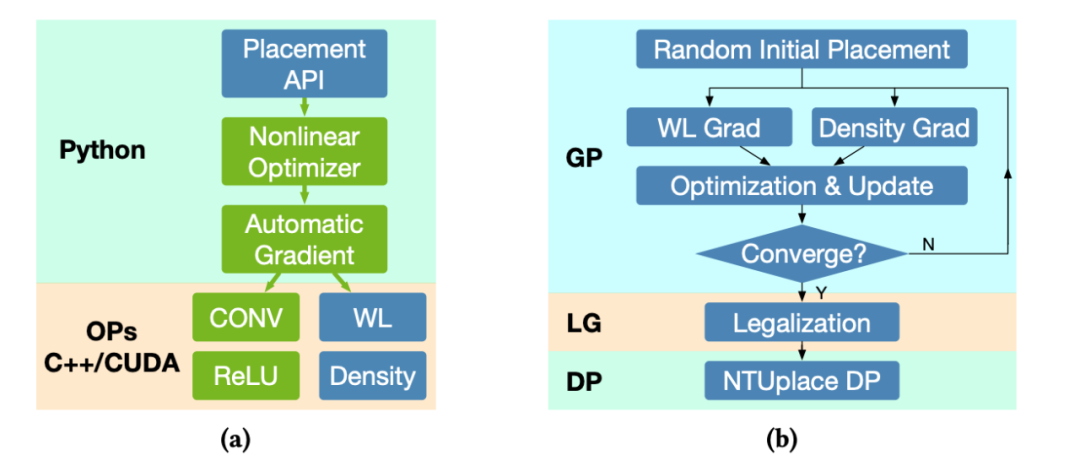

使用GPU对EDA算法进行加速是近年来非常火热的研究方向。例如使用GPU加速布局过程 [18]。这些方法巧妙利用了EDA问题的优化过程与深度学习训练过程的相似性。于是它们可以利用已有的深度学习框架,例如PyTorch,来进行基于GPU的快速优化。但这类方法不会去应用具体的ML模型,也没有基于数据的训练过程。

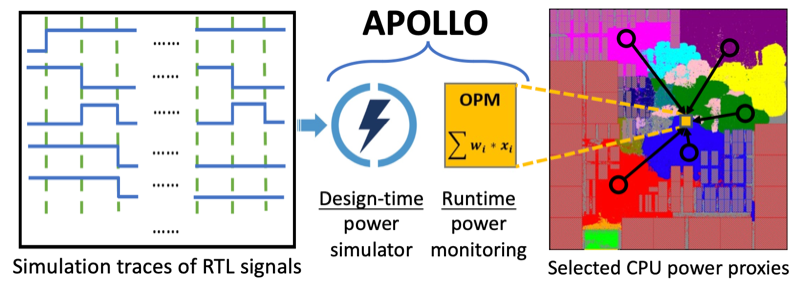

图14 使用GPU加速芯片布局过程 [18] 另外一个常被归类为ML for EDA的方向是:在芯片上实现ML模型,将它用于进行芯片运行时的监测,控制,或管理。例如利用ML方法,开发一个片上的实时功耗检测工具 [19]。使用ML方法的目的是减少这个模型在芯片上的硬件开销。严格意义上说,这更接近芯片设计而非EDA工具范畴,也许可以将它归类到ML for hardware design的范畴。

图15 使用ML开发的高效片上功耗检测模型 [19]

07 ML for EDA面临的挑战

最后简单总结一下 ML for EDA可能会面临的一些挑战。而针对这些挑战,近年来大家也进行了一些尝试。

第一,训练所需的芯片设计数据非常难以获得。对于这个问题,一方面一些研究者开始提供公开的芯片设计数据集 [20]。另一方面,研究者探索了在保护数据隐私条件下的模型训练,例如基于联邦学习的方法 [21],或者对训练数据进行一些加密。第二,开发和维护ML模型需要大量ML背景的工程师,而这对半导体公司来说并不容易。为了进一步提升自动化的程度,研究者探索了一些自动化的ML模型开发方法 [22]。这些工作一般基于深度学习领域已有的AutoML或者神经网络架构搜索(NAS)方法,然后对特定问题进行一些定制化设计。第三,由于芯片设计与制程的差异,ML方法的准确性难以保证可迁移性。另外ML方法的安全可靠性也需要更多保证。已经有不少研究ML方法安全与可靠性的初步工作。论文 [23] 中提供了一些总结。第四,从实际工程角度,ML方法如何更好地融入现有的EDA工具与芯片设计流程。这一点也许需要研究者与工业界共同进行探索。

08 结语

本文大致介绍了ML for EDA这一热门研究方向。总体来说,ML方法在EDA领域提供的数据驱动的优势是极其独特的。考虑到这些特点,我个人确信更多的ML算法未来会融入芯片设计流程之中。但至于ML算法究竟会在未来的设计流程中占到多大比重,这当然取决于大家未来的探索与实践。非常期待基于ML的新方法能够推动EDA产业,特别是国产EDA产业的发展。

审核编辑 :李倩

-

请问一个人工智能方面的专业名词2015-05-10 2862

-

人工智能是什么?2015-09-16 6402

-

人工智能:革命还是伤害?2016-10-10 10142

-

百度人工智能大神离职,人工智能的出路在哪?2017-03-23 7978

-

人工智能成热潮,嵌入式如何分杯羹?2017-09-06 2968

-

人工智能就业前景2018-03-29 8390

-

解读人工智能的未来2018-11-14 4857

-

人工智能医生未来或上线,人工智能医疗市场规模持续增长2019-02-24 5820

-

人工智能:超越炒作2019-05-29 4977

-

什么是基于云计算的人工智能服务?2019-09-11 5900

-

人工智能芯片是人工智能发展的2021-07-27 6630

-

物联网人工智能是什么?2021-09-09 5297

-

嵌入式与人工智能关系是什么2021-10-27 3404

-

【开源硬件系列04期】AI人工智能技术带给EDA的机遇和挑战(文中含回放+课件)2023-01-17 6865

-

《移动终端人工智能技术与应用开发》人工智能的发展与AI技术的进步2023-02-17 2323

全部0条评论

快来发表一下你的评论吧 !