使用肖特基钳位电路提高三极管开关速度

描述

上期从三极管放大的角度来分析了三极管开关电路的由来,并且将输入信号频率提高后,引发了输出信号延迟的现象,造成开关速度慢。主要讲了通过加速电容来提升速度的方法,这期重点另一种加速开关速度的方法,使用肖特基钳位电路。

关键词:肖特基钳位电路;

为了更好的理解,将三极管开关速度慢重述一遍!

01开关速度慢的原因

1.1、仿真电路结构

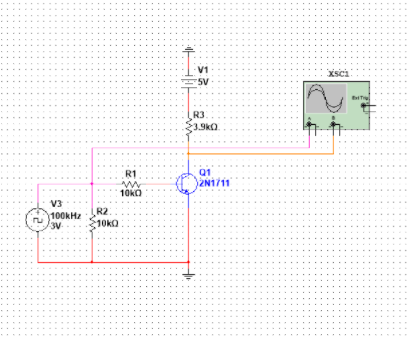

图1-1是系统仿真电路图:

图1-1 系统仿真电路

1.2、仿真波形分析

现象:

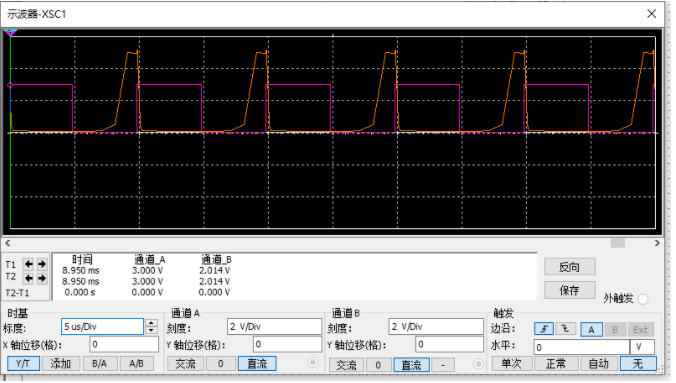

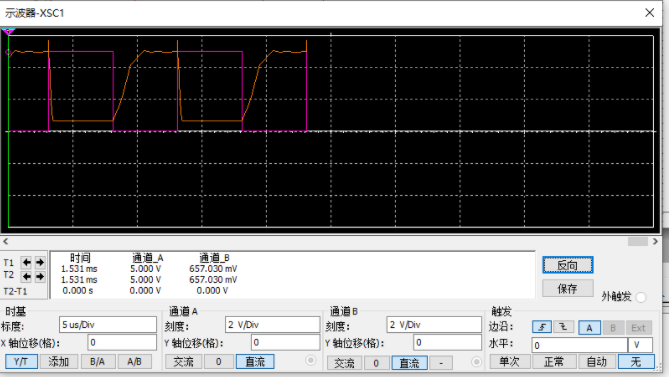

图1-2是图1-1的电路输入100KHz、0V/+3V方波时的输入输出波形。当输入信号从0V变化到+3V时,晶体管立即由截止变化到导通状态,输出信号也应立即响应,从+ 5V变化到0V。但是,输入信号从0V变化到+3V时,晶体管从导通状态变化到截止状态时却花费了一些时间,输出信号从从0V变化到+5V时滞后了3.34us。

原因:

晶体管处于导通状态时有基极电流流过,所以在基区内积累有电子,因此,在这种状态下即使输入信号变成了0V,基区中的电子并不能立即消失(电荷存储效应)。而且在基极限流电阻R1的作用下,也不能立即从基区取出全部电子,这就造成时间滞后的原因,在开关调节器之类使负载告诉开关的应用电路中,这种时间滞后是非常不利的。

图1-2 输处信号出现延迟

02提高开关速度

使用晶体管开关时,上述图1-1所示的开关速度往往不能满足要求,许多应用需要更高的开关速度,这里就需要提高速度的基本技术进行试验,这里注重分析两种提高开关速度的方法:使用加速电容、使用肖特基钳位。

2.1、使用肖特基钳位

提高晶体管开关速度的另一个方法是利用肖特基二极管钳位,这种方法是74LS、74ALS、74AS等典型的数字IC TTL的内部电路中所采用的技术。

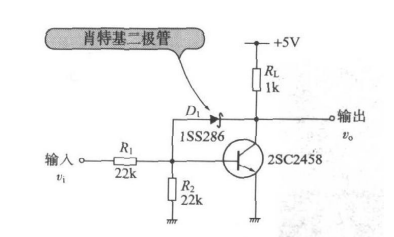

图1-3是对图1-1电路进行肖特基钳位的电路,所谓肖特基钳位就是在三极管的基极-集电极之间接入肖特基二极管。这种二极管不是PN结,而是由金属与半导体接触所形成具有整流作用的二极管,其特点是开关速度快,正向电压降Vf比硅PN结小,准确地说叫做肖特基势垒二极管。

图1-3 进行肖特基钳位的电路

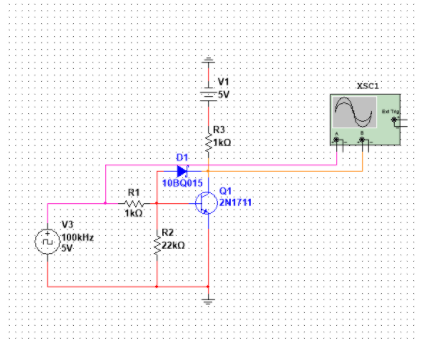

在仿真电路中加入肖特基电路如图1-4所示:

图1-4 仿真电路

图1-4电路与图1-1电路相比,适当地调整了基极电阻R1,其原因是基极电阻不能太大,否则加了肖特基二极管将起不到什么作用!

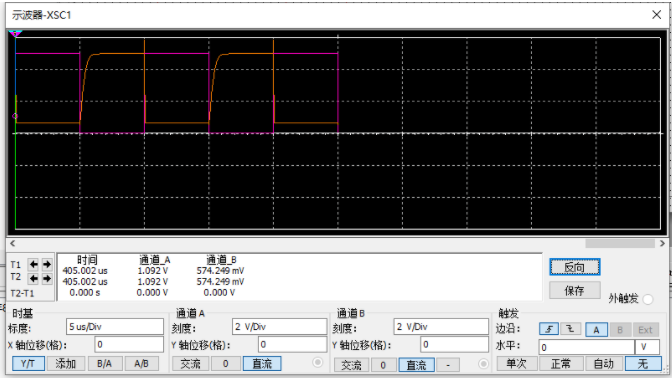

图1-5是给图1-3的电路输入100KHz、0V/+5V方波时的输入输出波形。可以看出其效果与接入加速电容时相同,晶体管从到导通状态变化到截止状态时没有看到时间滞后。

图1-5 输出波形与输入波形对比

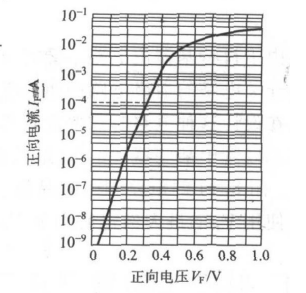

图1-5是图1-3的电路中晶体管处于导通状态(输出0V)时的动作,如图1-6所示,肖特基二极管的正向电压降Vf比晶体管的Vbe小(图1-3电路中Vf≈0.3V),所以本来应该流过晶体管的大部分基极电流现在通过二极管D1被旁路掉了,这时流过晶体管的基极电流非常小,所以可以认为这时晶体管的导通状态很接近截止状态。

图1-6 肖特基二极管的正向电压降Vf

因此,图1-5所示从导通状态变化到截止状态时的时间滞后非常小(基极电流小,所以电荷存储效应的影响小)。图1-5中,输出波形从0V变化到+5V时之所以波形上升沿不是很陡峭,是由于电阻R1与晶体管密勒效应构成低通滤波器的影响,与电荷存储效应没有关系。

03如何提高输出波形的上升速度

图1-7是图1-4所示的电路中基极电阻R1=200时的开关波形(入100KHz、0V/+5V方波)。可以看出当基极电阻R1小时,由于低通滤波器的截止频率升高,所以输出波形从0V变化到+5V的上升速度加快了。

加速电容是一种与减小基极电阻R1等效的提高开关速度的方法(减小基极电阻R1,也会加快输出波形的上升速度)。肖特基钳位可以看作改变晶体管的工作点,减小电荷存储效应的影响,提高开关速度的方法。

图1-7 改变基极电阻R1=200的波形图

由于肖特基钳位电路不像接入加速电容那样会降低电路的输入阻抗,所以当驱动开关电路的前级电路的驱动能力较低时,采用这种方法很有效。

在设计这种电路时需要注意肖特基二极管的反向电压的最大额定值,肖特基二极管中某些元器件的反向电压的最大额定值非常低(高频电路中应用的某些器件仅为3V),图1-4的电路中,因为晶体管截止时电源电压原封不动地加载二极管D1上,所以必须使用反向电压最大额定值大于5V的器件。

-

影响三极管开关电路的导通速度的因素是什么2019-05-17 11852

-

三极管的应用电路 NPN和PNP型三极管的区别2023-04-03 12554

-

三极管的分类和工作特性 如何提高三极管开关速度2023-07-28 6429

-

提高三极管开关速度的几种方法2023-08-01 3692

-

三极管开关电路图2007-06-06 11681

-

三极管,三极管是什么意思2010-03-06 11436

-

三极管钳位器工作原理2010-05-24 17678

-

如何提高三极管的开关速度?2017-11-22 53996

-

详解三极管开关电路的设计方法2017-12-07 50473

-

三极管和继电器的区别 三极管电路总结2018-09-23 21645

-

开关三极管的应用_开关三极管常用型号2019-08-18 13239

-

PNP三极管和NPN三极管的开关电路2021-10-23 5879

-

硬件电路设计之“三极管开关速度”2022-02-09 1189

-

使用加速电容提高三极管开关速度2023-01-13 5833

-

提高三极管的开关速度的几种方法2023-10-31 3532

全部0条评论

快来发表一下你的评论吧 !