监控器IC监控电池供电设备

描述

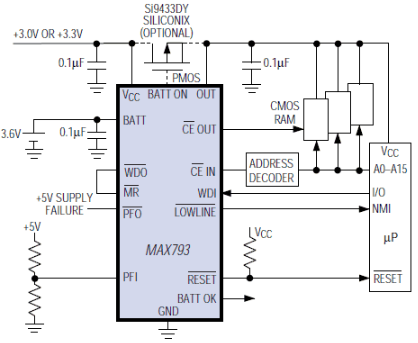

为确保正确运行,大多数基于微处理器的系统都需要在上电和关断期间以及进入或退出关断或休眠模式时进行监控。监控器可能仅提供上电复位,也可能提供附加功能,例如备用电池管理、存储器写入保护、低线预警或软件看门狗(图1)。

图1.功能丰富的μP监控器(IC1)借助μP本身,在这个典型的应用电路中执行各种功能。

通过选择众多可用的微处理器 (μP) 监控器 IC(也称为上电复位、电源良好电路、复位电路等)之一,可以同时或以各种组合方式获得这些功能。以下讨论可帮助您选择最适合您应用的方法,并为许多常见的μP监督问题提供解决方案。

首先,确定Vcc将发出复位的阈值电压。(RESET的置位在电源电压超出容差时阻止μP操作。典型的上电复位电路由基准电压源、比较器和定时器组成。比较基准电压与上升的V电压抄送(通过分压器)使比较器能够在 V 时进行输出转换抄送超过阈值 (VRST) 由分隔线设置。此转换会触发定时器,定时器根据需要保持复位,以防止软件执行,直到系统振荡器启动并稳定下来。

当 Vcc低于 VRST,主管再次发出复位并保持它,只要 V抄送仍低于 VRST.对于某些微控制器(μC),建议使用简单的RC电路来定时此上电复位;其他器件在μC芯片上提供复位电路。然而,这些方法假设电源电压行为是可预测的。它们不能防止由于掉电或更重要的是,在“掉电”期间可能发生的代码执行错误,其中 V抄送可能会在很长一段时间内略微脱离监管。监控IC对于这些关断和掉电条件最有价值。

影响阈值的因素包括 Vcc上的公差、系统IC允许的最小和最大电源电压,以及可能需要为这些变量的最坏情况组合指定设计。对于许多系统,复位功能并非旨在涵盖所有可能的条件,包括温度范围内的最坏情况组合。例如,系统可能包括仅指定为4.75V(最小值)的IC,但取决于最小/最大跳闸门限为4.5V/4.75V的监控器。在这种情况下,主管仅在 Vcc之后断言重置已降至 IC 工作保证的最低电压以下。

另一种方法是在4.75V和(可能)4.85V之间选择一个复位门限。但是,这些值可能允许在需要之前进行重置。通常,您必须决定是否可以容忍较低的阈值,以便在较低电压下获得工作时间;或者与更高阈值相关的额外费用和减少的运行时间是否是为了提高准确性而进行的公平交易。监控器IC现在的复位阈值容差高达±1%(图2)。

图2.这三款IC提供不同的监控功能组合,但每款IC都监控V抄送准确率为 ±1%。

监控多个电源

许多应用需要5V和3.3V电源,如果其中任何一个失去稳压,通常必须复位整个系统。您还需要适当的上电复位持续时间,以确保在上电期间正常运行。具有电源故障比较器和手动复位输入(/MR)的监控IC为这些问题提供了经济高效的解决方案。

如果选择内部门限设置为监控 3.3V 的监控 IC,则可以使用非专用电源故障比较器来监控 5V 电源:只需将电源失效比较器输出 (PFO) 路由回/MR 输入(图 3)。当任一电源失去稳压时,这些连接使IC置位/复位。IC由3.3V供电,因此/RESET输出在工作时摆幅为3.3V。该级别满足 VIH大多数 5V 处理器的要求,因此/RESET输出通常可以驱动3V和5V处理器。如有必要,您可以通过二极管OR连接将其他系统复位信号路由到/MR输入。(即使没有这些连接,也需要从/MR输入到PFO输出的二极管。

图3.如图所示配置,该监控IC可监视3.3V和5V电源。

停机例程预警

关键系统通常需要在电源电压(V抄送) 开始下降。该警告允许μP有时间存储重要数据,并在V下降之前执行“内务”工作抄送导致管理引擎发出硬重置。如果原始直流输入电压可访问,则可以使用欠压或电源故障比较器对其进行监视,该比较器反过来置位处理器中断以指示未稳压电源何时崩溃。

如果您无法访问此原始输入电压,则必须在监视同一稳压电源的同时生成预警和复位信号。您可以对低线信号使用单个阈值检波器,对复位信号使用延迟定时器,也可以使用两个不同的比较器,一个用于低线一个用于 tRST.无论哪种方式,您都必须确保 V抄送保持足够长的有效期,以完成低线信号中断后的关断例程。

完成关机/备份例程所需的时间因应用而异,V 的下降率也是如此抄送.因此,您必须根据应用将延迟从低线调整为复位。双阈值方法比延时复位方法更灵活。通过将低线阈值调整到复位阈值以上数十毫伏并调整V抄送下降速率 为了符合关断例程的时间要求,可以使一个IC服务于许多不同的应用。

在大多数电池供电的便携式系统中,电池中的备用能量提供了充足的时间,以便在低线警告和复位之间的时间间隔内完成关断程序。如果 V抄送下降时间很快,如正常工作时打开高边开关时,在开关负载侧增加电容以减缓V的下降抄送并提供执行关机例程的时间。例如,在MAX814监控器中,电源故障比较器的延迟(小于50μs)可能会影响也可能不会影响您的应用。

首先,计算关断例程所需的最坏情况时间。使用此值,最差情况下的负载电流和最小低线至复位阈值差(VLR(分钟)),计算复位发生前完成关断例程所需的电容:

我在哪里负荷是从电容器中排出的电流,VLR(分钟)是低线阈值和复位阈值之间的最小差值,并且SHDN是有序关断所需的时间,包括复位比较器的传播延迟。

将低线阈值置于复位阈值以上可能会因噪声而产生错误的低线触发。为了克服这个问题,通过适当的旁路滤除噪声,并在关断程序完成后使用软件监控低线中断。当处理器从低压线比较器接收到中断时,它会完成备份/关断例程,然后返回监视中断。如果线路或负载瞬态导致低压线路相对较快地返回高电平,则软件会通过重新加载存储的参数来启动“热”启动。如果发生电源故障,低线信号后跟复位信号,并开始正常的备用电池工作模式。

DC-DC 升压电路延长关断时间

如果备份/关断例程需要的时间超过存储电容器的合理时间,则可以使用 DC-DC 转换器来维持 Vcc当关机例程正在进行时。备份完成后,μP 可以关断 DC-DC 转换器。

例如,在图4中,IC2是一个升压转换器,当5V主电源发生故障时,它为系统和μP监控器(IC3)提供5V电压。在这种电源故障开始时,当主电源降至4.65V以下时,IC1关断Q1,使IC2退出关断状态,并中断μP。未达到复位阈值,因此不会发出对μP的复位。当μP完成其关断程序时,只需将IC2再次拉入关断状态,系统进入正常的电池备份模式。

图4.V 的威胁抄送损耗导致升压转换器 (IC3) 导通并恢复 V抄送到其标称水平。

升压转换器可提供高达 100mA 的电流,同时由已耗尽至 2.5V 的锂电池供电。如果需要,您可以为 RAM 备份和升压转换器提供单独的电池。

防止错误重置

监控电路不得响应系统噪声或V发出复位抄送负载瞬变。数字电源线上大约50mV的噪声很常见。模块、外设和其他子系统打开或关闭时发生的负载瞬变,如果复位比较器的传播延迟太短,可能会导致严重问题。

通过选择复位比较器传播延迟为10μs至30μs的监控电路,可以避免错误复位。较短的传播延迟(几百纳秒)对 Vcc 做出快速反应瞬态,因此可能会产生错误复位。另一方面,长时间的延迟可以让 Vcc在重置处理器之前,超出系统 IC 的工作范围太远。大多数 5V 应用包括足够的电容以降低 Vcc下降率,使得复位发生在 Vcc低于 IC 电气特性中规定的最低水平。

备用电池

对于需要非易失性存储器的关键系统,设计人员可以选择可擦除/可编程存储器或带备用电池的CMOS RAM。EEPROM和闪存的额定值不仅包括存储器容量,还取决于它们可以经历的写入周期数。最常见的非易失性存储器包括一个开关,用于将CMOS RAM连接到锂备用电池或Vcc,以较高者为准。

大电容器(约0.5F)提供了一种提供短期内存备份的常用方法。称为超级电容™或最大电容™,这些电容器从 V 充电抄送正常工作期间通过二极管(图5)。充电电流受电容器内部串联电阻的限制,该电阻相对较高。内存从 V 切换抄送到电容器时 V抄送折叠到IC的复位阈值以下。可用的备份时间取决于进入RAM和监控器IC的静态电流水平,以及电容器本身的自放电泄漏。对于许多在备份模式下仅消耗数十微安电流的系统,这种备份电容器可以保持数小时的内存内容。例如,Maxim监控器的1μA静态电流通常微不足道。

图5.一个非常大的电容器(在本例中为0.47F)可以用作低静态电流系统中的备用电池。

3V 应用中的备用电池切换带来了挑战:如何确定何时在 3.3V Vcc之间切换和3.6V锂备份电池?一种方法是定义一个高于CMOS RAM最小待机电压的接地参考电压。因此,V抄送为内存供电,直到它下降到略高于 2V 的电压;然后将RAM切换到备用电池(图6)。

图6.当 V抄送吸收至略高于 2V 的电压,该系统将 CMOS RAM 从 V 切换抄送到备用电池。

特殊情况

为了节省电池能量,电池供电便携式设备的设计人员通常使用80CL51 μC的省电模式。如果CMOS存储器内容的保存至关重要,IC1的/低线输出(图6)会产生中断。当主电池电压低到足以导致V时,此中断信号可以触发关断程序抄送失落于容忍度。RAM 内容物通过电池中剩余的任何能量保持活力。

当μC处于省电模式且监控器的RESET直接连接到μC的RST端子时,Vcc低于重置阈值将导致重置变高。这反过来又唤醒μC并将其置于运行模式,将其静态电流从大约100μA增加到6mA。电池电压继续下降,Vcc保持在阈值以下,因此6mA将耗尽电池电量,从而大大缩短可用的备份时间。

只需将/低电平有效和复位与AND门相结合(图7),即可确保IC3的RST仅在复位超时周期内驱动为高电平(而不是当Vcc时正在下降)。换句话说,RST 在 V 之后变高抄送已恢复(通过为电池充电或安装新电池)并重新越过低线阈值。因此,AND门允许休眠控制器保持休眠状态。

图7.AND 栅极通过防止微控制器操作中不必要的转换(从睡眠模式到更高电流的空闲模式)来节省电池能量。

与 V抄送在其正常工作范围内,RESET为低电平,/低电平有效为高电平。当 V抄送降至低电平线门限以下(通常比复位门限高 45mV),/低电平有效变为低电平,向 80CL51 发出关断程序信号。重置断言当 V抄送遇到复位门限,但/低电平有效迫使AND栅极输出保持低电平。

上电时,/LOWLINE保持低电平,因此RST保持低电平,直到V抄送越过低线阈值。然后,RESET在重置超时周期内传播到RST终端。因此,80CL51 仅在 V抄送有效。

在此应用中,还希望能够检测电池在睡眠期间的任何时间是否已放电到安全RAM备份电压以下。使用此信息,系统决定是根据 RAM 的内容执行“热启动”,还是从头开始执行“冷启动”,因为低电池电压可能已损坏 RAM 数据。IC1的BATT端子(引脚16)告诉μC哪种导体合适。

IC1有一个低电池电量比较器,通常指示连接到其BATT端子的备用电池的状态。此比较器输出(BATT OK)未锁存。图 7 中的应用没有备用电池,因此您可以使用 BATT 锁存 BATT OK 的状态。 只需将 BATT 连接到 80CL51 上的可用 I/O 引脚,并通过 10kΩ 电阻连接到 BATT OK 端子。

为了设置为正常工作,μC将I/O线路脉冲至高电平约30μs,然后将线路配置为高阻抗输入。IC1中的比较器将BATT OK驱动为高电平,从而将BATT拉高并在该条件下锁定。比较器由V供电抄送,所以它在高状态下的输出接近V抄送.如果 Vcc在休眠期间的任何时候都低至 2.25V,比较器输出捕捉到低电平并将 BATT 拉低,将其锁存于低电平。Vcc之后恢复(通过为主电池充电或更换主电池)μC 在继续之前轮询 BATT:高表示热启动,低表示冷启动。

摩托罗拉 68HC11 等 μC 具有双向复位引脚,可能会与监控 IC 的/复位有效抗争。例如,如果监控器复位为高电平,而μC试图将其拉低,则结果可能是不确定的逻辑电平。图8的连接允许监控器和μC对系统进行有效的复位,并确保复位脉冲有足够的持续时间(μC复位对于系统中的某些器件来说可能太短)。

图8.这些连接允许对缓冲复位线路进行双重控制,并延长μP发出的复位持续时间。

该电容支持从监控器和μC复位,以将/MR拉低电平。/MR变为低电平在监控器内启动200ms超时,在其/RESET端子(引脚2)上产生200ms最小脉冲,该脉冲覆盖μC/RESET,并通过缓冲器驱动系统复位线路。当电容充电时,/MR返回高电平。当μC/RESET在超时延迟后解除置位时,电容通过/MR上拉电阻和一个内部ESD保护二极管放电。

审核编辑:郭婷

-

TI电池监控器IC的HDQ通信基础知识2024-10-12 542

-

是否存在真正的无毛刺电压监控器IC?2023-08-08 1925

-

如何提高电压监控器IC的性能2023-07-10 1797

-

监控器IC监控电池供电设备2023-06-26 1753

-

带有图表和电池监控器的温度和湿度监控器2022-10-21 718

-

微控制器监控器集成电路中的故障保护分析2022-03-26 10435

-

电压检测器和监控器和复位IC怎么选择2019-08-06 3996

-

如何选择合适的电压检测器、监控器和复位IC?2019-07-31 3100

-

电源IC 电流和电力监控器、调节器2018-07-30 1317

-

可用于电池充电和监控 PC 的监控器PMP5214技术参考资料及物料清单下载2018-07-13 1390

-

【FireBLE申请】学生写字坐姿监控器2015-08-05 2273

-

无线监控器2014-03-28 2845

全部0条评论

快来发表一下你的评论吧 !