浅析OSAT的高性能封装技术

电子说

描述

摘 要:

高性能计算、人工智能和 5G 移动通信等高性能需求的出现驱使封装技术向更高密度集成、更高速、低延时和更低能耗方向发展。简要地介绍了半导体封测企业、晶圆代工厂和 IDM 在高性能封装领域的发展现状,分析了国内企业在此领域的布局和发展状况,并结合国家政策和国际环境变化,展望了未来国内封测企业在该领域的发展方向。

0 引言

1965 年 4 月 ,Intel 创始 人之 一戈 登· 摩尔(Gordon Moore)在《电子学》杂志上刊载《让集成电路填满更多的组件》,文章中预言:当价格不变时,半导体芯片上集成的元器件数目(如晶体管和电阻数量)约每隔 18~24 个月增加 1 倍,性能提升 1 倍。这个著名的摩尔定律,在过去的几十年间一直推动着半导体技术的发展。

为满足该定律的要求,晶圆代工厂不断地缩小晶体管栅极特征尺寸。直到20世纪90 年代,该理论开始遇到经济学和物理学上的双重阻碍。相比于技术节点 90 nm,3 nm 的投资成本增加了 35~40 倍 ,仅英特尔(Intel)、三星(Samsung)和台积电(TSMC)3 家企业有能力跟随,可以继续在该赛道上竞争。与此同时,科技浪潮向高性能计算、人工智能、深度学习和 5G 通信等领域快速地发展,其愈加依赖超高性能的高速芯片。除芯片自身往更高技术节点推进外,高性能封装技术也成为主要的解决方案之一。

高性能封装作为一种前沿的封装技术,其主要特点为I/O的高密度(≥16/mm 2 )和细间距(≤130 μm),其 典 型 的 代 表 为 高 速 专 用 集 成 电 路(application specific integrated circuit ,ASIC )处理 芯片 和大 约4 000 个 端 口 的 高 带 宽 存 储 器(high bandwidth memory,HBM)的超高密度连接,该异构芯片集成封装技术将整体性能推向极致。

据 Yole development预测,从 2019~2025年,高性能封装的市场营收将由8 亿美元增至 43 亿美元 ,年平均复合增长率约为31%。对此,封测企业(OSAT)、晶圆代工厂和垂直整合制造厂(integrated design andmanufacture,IDM)纷纷强势加入该赛道,布局相关发明专利,抢占市场。

本文主要介绍国内、外现有的高性能封装技术,阐述其结构特点,分析我国在该领域的现状,为国内封测企业在高性能封装技术的研发和产业化上提供必要的信息支持。

1 主要的高性能封装技术

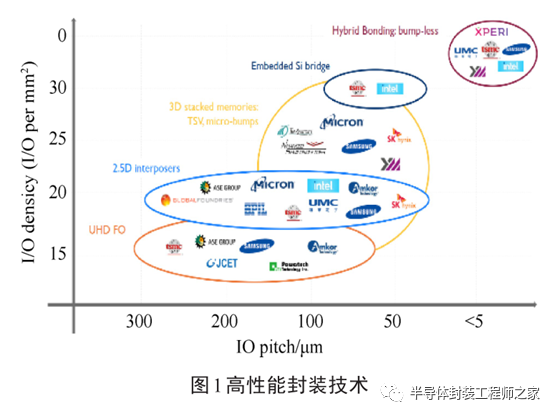

目前,高性能封装技术主要包括:超高密度扇出封装(ultra-high densityfan-out,UHD FO)、2.5D interposer、3D stacked memories 、embedded Si bridge和 hybrid bonding,其关键技术基本掌握在世界头部封测企业(OSAT)、先进的晶圆代工厂和 IMD 手中,如长电科技、日月光 、安靠、台积电(TSMC)、三星(Samsung)和英特尔(Intel)等,如图1所示。

在高性能封装技术中,芯片间的异构或异质封装集成扮演着重要作用,涉及TSV技术、高密度重布线(RDL)、micro bump 和 bump less 混合键合等先进工艺,这些工艺对设备 、无尘室等级均有较高的要求,而且前期资本投入很高。晶圆代工厂和 IDM 利用自身先进的制造能力、强大的人才和经济实力,在高性能封装技术领域占据着绝对优势地位。

1.1 OSAT的高性能封装技术

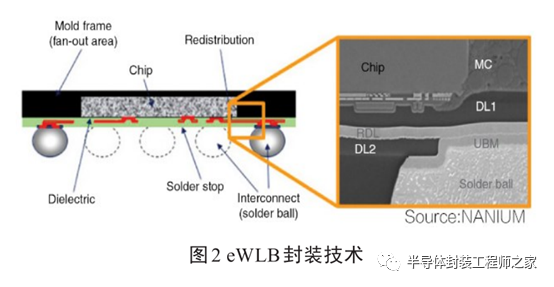

在高性能封装方面,OSAT厂的代表封装技术为Fan out和 2.5D 封装。其中,Fan out的典型技术为嵌入式晶圆级球栅阵列(embedded wafer level BGAe,WLB),由英飞凌在 2014 年提出 ,通过专利授权 ,在日月光(ASE)、星科金朋(STATS ChipPAC,被长电科技收购)、Nanium(被 Amkor 收购)等公司实现规模化量产。

eWLB 结构如图 2 所示,采用模塑料将 1 颗或多颗芯片进行封装。OSAT 基于 eWLB 技术,积极开发高密度基底上扇出型芯片(fanout chip on substrate,FOCoS)封装 ,其结构根据上芯的顺序 ,又可分为先芯片的基底上扇出型芯片(FOCoS chip last,FOCoS-CL)和 后 芯 片 的 基 底 上 扇 出 型 芯 片(FOCoS chip first,FOCoS-CF)。

在结构上,eWLB 通过不断缩减RDL线宽(Line,L)/间距(Space,S),由L/S 5 μm /5 μm递减至 OSAT普遍使用的 L/S 2 μm /2 μm;同时,RDL的层数将继续增加,最后由 bump pitch 小于 55 μm 的micro bump实现HBM和ASIC芯片间的高密度互连,打破内存对处理能力的限制(即“存储墙”)。

为进一步提升Fan out封装的I/O的互连密度,基于 FOCoS 的 堆 栈 Si 桥 接 的 基 底 上 扇 出 型 芯 片(stacked Si bridge FOCos,sFOCoS)被开发出来,该结构利用前道晶圆代工能力,制作线路 L/S 为 0.8 μm /0.8 μm的Si bridge,再将其埋入molding材料中,实现更高密度的互连;同时,可以降低Si interposer开发导致的高昂费用。

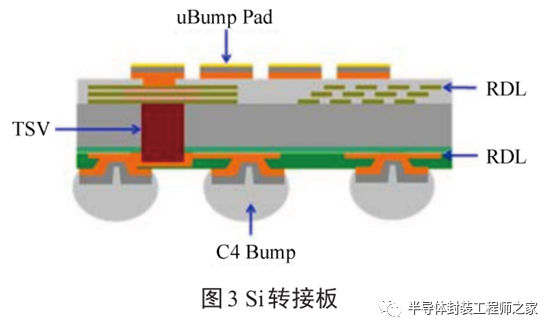

在2.5D封装方面,Si 转接板为其重要组成之一,能够实现异质芯片互连,满足高计算能力和高带宽的要求,如图3所示。

在 Si转接板上,可制作尺寸小于 1 μm 的线宽和过孔,在满足超高I/O密度方面具有明显的优势。但是,上述工艺均需采用晶圆代工厂的设备和工艺,技术成本高,因此,在OSAT厂未得到广泛使用。

1.2 晶圆代工厂和IDM的高性能封装技术

晶圆代工厂和 IDM 凭借技术、人才和资源等优势,积极地布局高性能封装,其中,最具实力的代表企业包括TSMC、Samsung和Intel。

1.2.1 TSMC的高性能封装技术

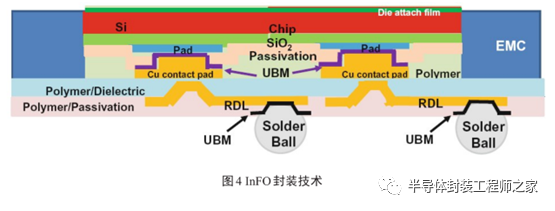

2016 年,TSMC 成 功 研 发 集 成 扇 出 封 装(integrated fan-out,InFO)技术,如图 4所示,并首次应用在当年苹果的旗舰机型 iPhone 7与 iPhone 7Plus中的 A10 处理器 ,成为 TSMC 独占苹果 A 系列处理器订单的关键,开启了整个半导体业界研发 2D 及3D FO 堆叠技术的热潮,并衍生出一系列相关产品,如InFO-oS,InFO-MS,InFO-AiP等。

InFO 与 eWLB 有类似的 Fan out 技术,无需印刷线路板,将已知合格芯片(known gooddie,KGD)进行晶圆重组,实现同质、异质芯片间直接互联,大大缩短互连长度;另外,TSMC 拥有 4层细线宽/线间距(2 μm/2 μm)的重布线和 36 μm 的芯片间 I/O pitch的加工能力,能够封装更多I/O的芯片,满足移动通信领域对于半导体器件的超小体积和更多功能的要求。

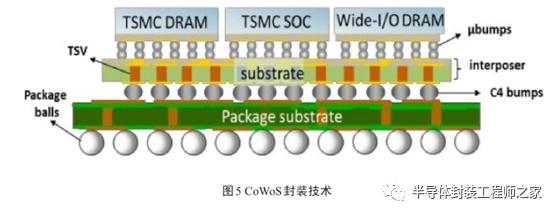

为进一步提高封装体的集成度,TSMC开发了配套晶圆基底(chip on wafer on substrate,CoWoS)封装技术,其结构如图5所示。根据Si interposer的使用情况 ,CoWoS 分为 CoWoS@-R 和 CoWoS@-S ,前者使用OSAT的光刻技术,可实现5层细线宽/线间距(2 μm /2 μm)的制作;后者直接使用晶圆代工厂的光刻和大马士革工艺,在 Si interposer 上制作亚微米级L/S 的 金 属 层 ,高 效 地 实 现 高 性 能 计 算(high performance compute,HPC)和 HBM 连接 ,并在苹果和高通产品上得到了重要的应用。

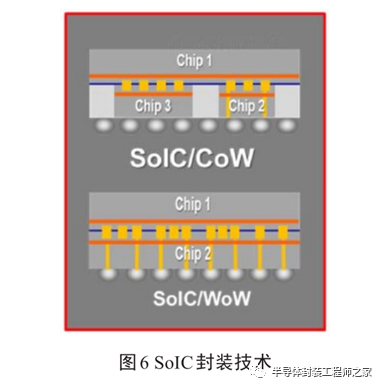

在 3D IC 方面 ,TSMC 在 2019 年提出系统整合单晶片(system on integrated chip,SoIC)技术,如图 6所示,其基于 TSV、micro bump 和混合键合等技术,可实现 I/O 密度大于 10 000/mm 2 的封装。SoIC将处理器、内存和传感器等几种不同类型的芯片堆叠在一起,使封装模组体积更小 、功能更强大,同时实现了低延时 ,低能耗的目的,可以说是真正意义上的 3D 堆栈技术 ,预计会在 2022 年实现规模化量产。

目前,TSMC 在晶圆级 3D IC 技术中已经拥有强大的 3D 封装技术组合 ,如 CoWoS,InFO-R,COW 和WoW 等。从 2020 开始,TSMC 采用新的“3D Fabric”框架推广这些技术,这是其 3D封装技术的新品牌计划,该技术是将小芯片、高带宽内存和专用IP捆绑在一起,构成异构封装。

1.2.2 Samsung的高性能封装技术

相较于 TSMC 的 12 寸晶圆级 InFO 封装技术 ,Samsung 主要在面板级扇出型封装(fan-out panel-level packaging,FO-PLP)上发力,进一步缩减封装成本,且在其高端产品Galaxy Watch的应用处理器上应用。目前,Samsung使用510 mm × 415 mm尺寸的面板制造FOPLP,且已经开发出高达800 mm × 600 mm规格的面板。

在 FO-PLP 的开发上 ,随着面板面积的增大 ,产品翘曲变得严重,对光刻工艺带来较大的挑战,直接影响高密度 L/S 为 2 μm /2 μm 的 RDL 的开发。除上述问题外,随着 L/S 的减小 ,Ti 残留和 Ti undercut 等工艺问题,也有待解决。

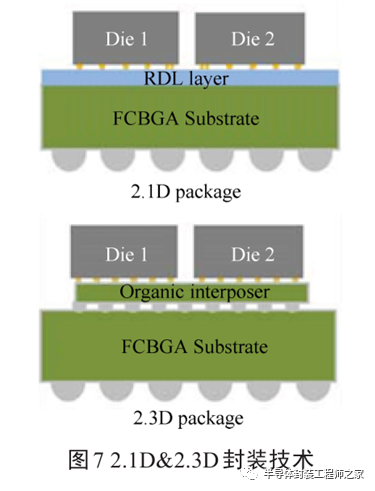

在 2.5D 封装方面 ,Samsung 除采用 Si interposer外 ,通 过 在 基 板 表 面 插 入 高 密 度 RDL 和 有 机interposer,开发出相对廉价的2.1D和2.3D封装,应用在部分低端产品上,如图 7 所示。此举避免了开发Si interposer 的高昂费用,同时,可直接在 OSAT 厂的光刻设备上实现。

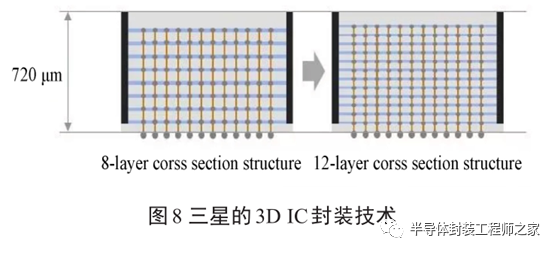

Samsung 在 3D IC 上与 TSMC 走相同的道路 ,通过 TSV 孔将相同的内存芯片垂直互连,如图 8 所示。三星的这项技术被认为是大规模生产高性能芯片所面临的最具挑战性的封装技术之一,其需要极高的精度才能确保上万个TSV孔的三维垂直互连。

1.2.3 Intel的高性能封装技术

与 OSAT、晶圆代工不同 ,Intel 作为 IDM 模式的代表,在先进封装领域,拥有独有的技术专利。

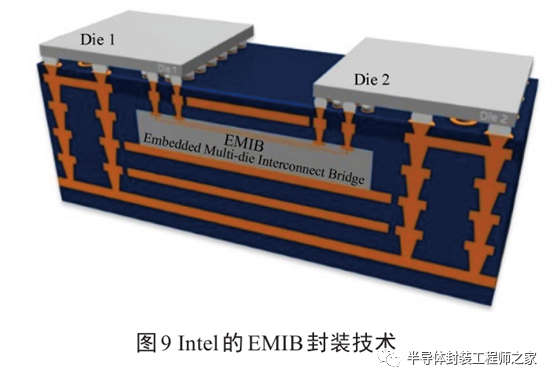

2014 年,英特尔提出嵌入式多芯片互连桥接(embeddedmulti-die interconnect bridge,EMIB)封装技术 ,是 2.5D interposer 封装技术的低成本替代方案,如图 9所示。EMIB 技术与典型的 2.5D 封装采用硅中介层不同,通过在基板中嵌入一小块硅芯片,实现两个芯片的高密度互连,起到“桥梁”的作用。其对芯片尺寸大小没有限制,从而在理论上保证了异质芯片的集成。由于没有 TSV,EMIB技术也属于基板类封装,因此,被划分为基于二维平面延伸的先进封装技术。

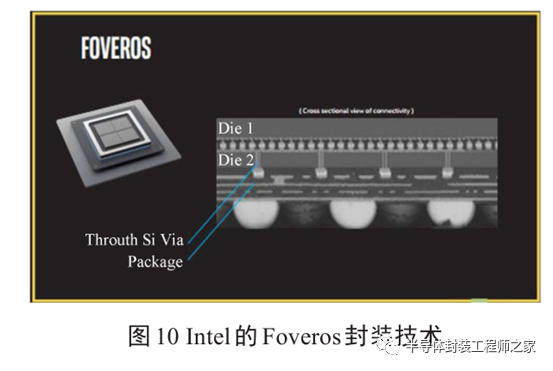

2018 年 12 月,英特尔首次展示了逻辑计算芯片高密度3D堆叠封装技术Foveros,其被称作三维面对面异构集成芯片堆叠技术,如图 10 所示。Foveros采用 3D 芯片堆叠的系统级封装(SiP),来实现逻辑对逻 辑(logic-on-logic)的 芯 片 异 质 集 成 。 首 款Foveros 3D 堆叠设计的主板芯片 LakeField,它集成了 10 nm Ice Lake 处理器以及 22 nm 核心,具备完整的PC功能,同时,其体积只有几枚美分硬币大小。

2 高性能封装的技术特点与国内现状

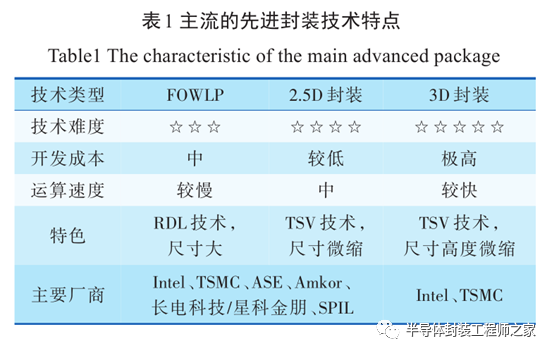

随着集成电路应用多元化,智能手机、物联网、汽车电子、高性能计算、5G、人工智能等新兴领域,对先进封装提出更高要求,封装技术发生着日新月异的变化,推动产业向着系统集成、高速、高频、三维、超细节距互连方向发展,Fan out、2.5D 和 3D 封装等先进技术受到更多的青睐。如表1所示,对比了这3种封装方式的特点。

近年来,国内领先企业在先进封装领域取得较大突破,先进封装的产业化能力基本形成 ,但在 2.5D/3D IC等高性能封装方面,中国大陆封装企业与国际先进水平仍有一定差距。海外并购让中国大陆封测企业快速获得了技术、市场,弥补了一些结构性的缺陷,极大地推动了其向上发展。但是,近期海外审核趋严,使国际投资并购受到阻碍、可选并购标的减少,中国未来通过并购取得先进封装技术与市占率的可能性减小,自主研发和国内整合将成为主流。

在自主研发方面 ,由于高性能封装采用高密度RDL、micro bump 和混合键合等先进工艺制程,涉及晶圆代工所用技术类型与设备等资源,封测企业在技术、资金受限情况下,可能选择与晶圆代工厂进行技术合作,或是以技术授权等方式,再搭配自身庞大的产能基础进行接单量产,共同扩大市场。目前,国内晶圆代工厂和封测企业进行合作的方向主要是晶圆级封装及低密度集成,在高密度集成方面的研发,仍有较长的路要走。

在国内三强封测企业中,长电通过收购星科金朋,获得 eWLB 的专利使用权,成为全球最大的晶圆级扇出型封装(FO-WLP)供应商之一,以此为基础,逐步进入 UHD FO 的领域。华天科技开发出 Si 基Fan out 封装技术,以此为基础,拓展其在 3D 封装方面的应用,但处理芯片和 HBM 需要较大的 Si基面积,由此造成的工艺问题尚待解决。

同时,在Si基上如何制作高密度 RDL 和微凸点 ,也需要进一步开发。通富微电子股份有限公司也较早地开始了 Fan out、2.5D 和 3D 封装等高端技术方面的研发,并积极和华为、AMD 等优质客户进行合作,开展 UHD FO、超薄存储芯片 2.5D TSV interposer 及 3D 堆叠集成封装技术研究,并建立生产线实现规模化量产。

在国家“十三五”和即将到来的“十四五”规划,以及 02 专项的大力支持下,国内封测企业积极地填补中国大陆在高性能封装的技术空白,提升关键工艺设备及关键工艺材料国产化的比重,打破半导体存储器市场在先进封装技术方面的垄断。

3 结论与展望

摩尔定律的趋缓使得高性能封装技术成为当下半导体技术发展的新方向主之一。国际头部 OSAT厂、晶圆代工厂和 IDM 热衷于在 Fan out、2.5D 和 3D封装技术上布局相关专利,开发新产品和实现规模化生产,不断夯实其在该领域的竞争优势。在高性能封装上,需要使用的高密度RDL、micro bump、TSV和混合键合等工艺技术,将处理芯片和 HBM 进行异构或异质集成,满足对高密度 I/O 的封测要求,最大限度地提升了芯片的性能。

审核编辑:刘清

-

晶圆代工厂涉足封装,会给OSAT带来威胁吗?2016-12-29 9436

-

如何采用不同封装技术构建高性能GaN设备2019-03-11 5544

-

硬盘改装电沙轮#技术分享 #DIY #制作过程 #高性能实用工具 #实用好物学习硬声知识 2022-09-13

-

#硬声创作季 家里的音箱坏了,便制作了一个高性能的移动音箱Mr_haohao 2022-10-20

-

电源旁路和总线技术在高性能电路中的应用2009-08-20 2542

-

简单介绍IC的高性能封装2010-01-28 4813

-

高性能DAC与ADC转换技术2013-06-08 2776

-

微电子封装技术2013-12-24 6490

-

PQFN封装技术提高性能2018-09-12 3228

-

浅析高性能PCB设计2018-09-14 1991

-

高性能功率半导体封装在汽车通孔的应用2019-05-13 1725

-

PrimeCell高性能矩阵(PL301)技术概述2023-08-22 709

-

高性能封装推动IC设计理念创新2023-05-26 1507

-

半导体组装和测试(OSAT)市场增长5.1%2023-10-17 2137

-

SK海力士与Amkor共同推动HBM与2.5D封装技术的融合应用2024-07-17 2149

全部0条评论

快来发表一下你的评论吧 !