PCB设计的电源处理与平面分割

电子说

描述

a) 小电源优先在信号层铺铜,其次通过满足载流的走线连接;

b) 12V、5V 电源如果是开关电源的输入电源,优先在信号层处理掉(表层、内层信号层),如果一定要在平面层分割,不要用作重要信号线的参考平面;这样可以有效减小此类“高”压对信号的影响;

c) 如果分割出的电源平面用作信号的参考平面,电源平面优先作为用电模块的信号参考平面;如果有多个电源,优先参考电压低的电源;例如 DDR3,使用的是 1.5V 电源,则 1.5V 电源平面可以用作 DDR3 模块的信号参考平面,但尽量不要参考 3.3V电源或者其他电源;(通常 DDR3 数据参考地平面,地址控制信号参考电源平面)

d) 电源平面和地平面紧相邻,如果电源平面相邻的是信号层,尽量在信号层多补一些GND 铜,并打 GND 过孔;

e) 分割线宽度要合理;分割线宽度和两个电源的电压差有关,一般推荐:模数之间分割宽度:25mil;数字之间分割宽度 15mil,局部可以更小一些;分割线宽度也可以根据板上空间情况灵活调整,原则上越大越好;

f) 机壳地分割隔离宽度优先 2mm,局部根据情况调整,一般要求不小于 1mm;其他信号远离机壳地,包括信号线、过孔、铺铜等;

g) 如果电源/地平面有分割,注意相邻信号层信号线不要跨分割,尽量避免分割开的参考平面上有高速信号的跨越。

h) 分割的电源过孔避开隔离带,隔离带避铜,会导致此类电源过孔没有连接;

i) 模拟区域的电源,为了减小电源对信号的影响,一般不推荐大面积铺电源网络铜,一般是在信号层处理掉,电源铺铜或者走线满足载流即可,其他区域尽量多铺地铜和打地过孔;

j) 高压电源和低压电源要分区,间距越大越好;避免高压干扰低压电源和信号;

k) 常见的爬电避让间距:

i. 电压<24V 时,表层盖阻焊、间距≥0.13mm;表层不盖阻焊、间距≥0.64mm

ii. 24V≤电压<48V 时、初级侧间距≥0.5mm,次级侧间距≥0.2mm;

iii. 48V≤电压<100V 时,间距≥1mm

iv. 100V≤电压<200V 时,间距≥1.5mm

v. 200V≤电压<400V 时,间距≥2.5mm

vi. 400V≤电压<600V 时,间距≥3.2mm

vii. 电压≥600V 时,间距≥5mm

l)确认电源、地能承载足够的电流。过孔数量是否满足承载要求

(估算方法:外层铜厚1oz时1A/mm线宽,内层0.5A/mm线宽)

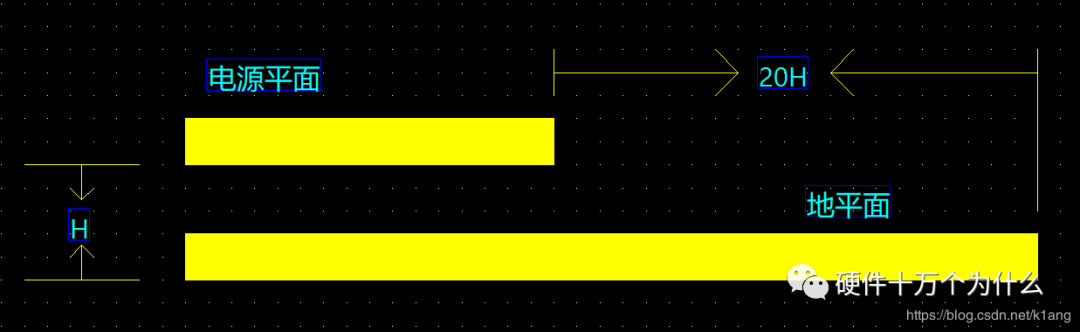

m)为降低平面的边缘辐射效应,在电源层与地层间要尽量满足20H原则。

(条件允许的话,电源层的缩进得越多越好)。

“20H原则”是指要确保电源平面边缘比地平面(0V参考面)边缘至少缩进相当于两个平面之间间距的20倍,其中H就是指电源平面与地平面之间的距离,如下图。

为什么需要20H原则?

在高速PCB中,通常电源平面和地平面间相互耦合RF能量成为边缘磁通泄露情况,而且RF能量(RF电流)会沿着PCB边缘辐射出去,为了减少这种耦合效应,所有的电源平面物理尺寸都要比最近邻的地平面尺寸小20H。

n)如果存在地分割,检查避免分割的地是否不构成环路?

o)相邻层不同的电源平面是否避免了交叠放置?

p)保护地、GND的隔离是否大于4mm?

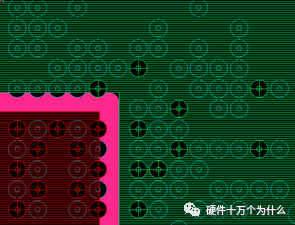

q)靠近带连接器面板处是否布10~20mm的保护地,并用双排交错孔将各层相连?

r)电源走线有效宽度检查:正负片铜是否有打断(BGA、过孔密集、以及过孔密集处是否有高速总线),需重点关注0.8mmBGA。

审核编辑:汤梓红

-

PCB设计信号线跨分割会有什么影响2024-01-03 1969

-

PCB设计中“跨分割”问题,合格的工程师应该这样处理2023-04-28 2277

-

PCB设计中跨分割问题的处理方法2023-03-09 4071

-

PCB地平面分割设计2022-12-23 9344

-

PCB设计中跨分割的处理2022-02-12 5848

-

PCB设计电源平面处理要点2022-01-06 759

-

介绍在PCB设计过程中电源平面处理应该考虑的基本要素2021-12-28 1318

-

PCB信号跨分割线怎么处理?2020-09-02 7856

-

PCB设计的电源平面处理基本要素是什么?2019-09-11 1944

-

PCB设计电源平面应该怎样考虑哪些因素2019-08-23 1907

-

几个小技巧帮你处理电源平面2019-08-06 2205

-

PCB设计电源平面处理要点分析2019-07-25 3465

-

PCB设计电源平面处理要点,你都了解吗?2019-07-15 1414

-

PCB设计中电源平面处理应该考虑的基本要素2018-11-07 5911

全部0条评论

快来发表一下你的评论吧 !