RISC-V拿什么挑战ARM?

处理器/DSP

描述

目前RISC-V和ARM的主要差距体现在上下游产业生态和规模化应用上,这是摆在RISC-V阵营的玩家们面前最大的挑战和难题。

我们指挥电脑工作,不能简单的和电脑说:“嘿,帮我运行个程序。”因为计算机只能理解0和1组成的指令(机器语言),难道人类要想操作电脑就需要输入成千上万的0和1吗?稍微了解编程的朋友知道,使用编程语言让电脑输出“hello,world”只需要一行简单代码:

printf (“hello,world ”); //c语言描述

print(hello,world) #Python语音描述

这就比只有0和1的命令简单明了的多。事实上当计算机运行这行代码时,CPU收到的依旧是只有0和1的命令串,这中间的变化,就是指令集(ISA)与编程语言(汇编+高级)共同帮我们翻译的,指令集则是最接近机器语言的“翻译官”。简单的说,指令集就是一串串二进制机器语言的合集,用来描述这些二进制指令的语言叫做汇编语言,后来又出现了许多编译器和高级语言来帮助程序员更方便的编程。本文将要讲到的RISC-V与ARM都是指令集的一种。

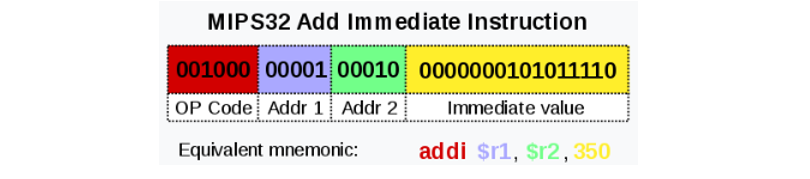

Add Immediate指令(二进制机器语言)

图源 | 维基百科

要想设计一个处理器,第一步就需要确定这这颗处理器使用的指令集是什么。指令集决定了这颗芯片在工作时具体的计算方式,芯片上数量众多又复杂晶体管其实就是将指令集用电路固定下来。

总而言之,指令集对芯片来说十分重要,它能直接决定芯片的电路布局方式,是每一种新型的CPU在设计时就规定的一系列与硬件电路相配合的指令系统。而指令集的先进与否,也关系到CPU的性能发挥,它也是CPU性能体现的一个重要标志。

目前指令集也分为两类,精简指令集和复杂指令集,但它们的区别并不是二进制命令的长短。

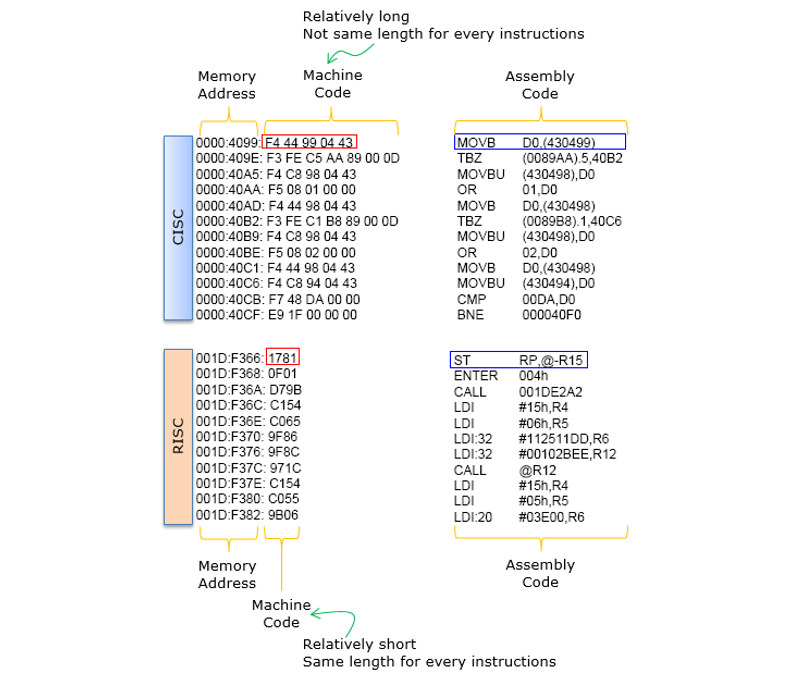

复杂指令集VS精简指令集

指令集刚诞生时较为繁琐,人们通过优化将部分指令打包在一起,再把一些原来由软件实现的、常用的功能改用硬件的指令系统实现,以此来提高计算机的执行速度,这种指令集称为复杂指令集(Complex Instruction Set Computer,CISC)。在复杂指令集中,存储器读取、存储和计算操作往往全部集中于单一指令中。复杂指令集的特点是指令数目多而复杂,每条指令字长并不相等,电脑必须加以判读,并为此付出额外性能。

20世纪80年代,为了解决计算机性能不足的问题,人们找到了另一种优化指令集的方法。芯片设计师选择仅保留一些功能简单,执行快速的简单命令,将复杂程序用用一段程序来实现,这种指令集就被称为精简指令集(Reduced Instruction Set Computer,RISC)。RISC属于等长指令集,CPU在执行指令的时候速度较快且性能稳定。与复杂指令集相比,精简指令集更容易实现诸如程序调用和返回,循环等指令,指令并行执行程度更好,编译器的效率更高。

RISC与CISC指令的区别

图源 | Tech Journeyman

既然RISC优势这么明显,那是不是RISC必然会替代所有CISC指令集了呢?

并没有,与CISC相比,RISC指令集也有自身不足。虽然RISC指令较为简单,但其本身拥有的指令较少,在完成某些任务的时候需要执行更多指令,这也使得RISC在编译时代码长度要显著长与CISC,因此也需要占用更多内存,编译难度也会增加。

业内有专家曾分析RISC的缺点:“执行同样的功能,一个RISC程序比一个CISC程序长30%。同时,RISC对编译器要求较高,优化编译器是一项极其复杂且技术要求很高的工作,它必须由RISC机制造单位自身编制,因为没有RISC详细原始资料不可能产生编译程序的目标代码。因此这会让第三方公司增加额外的软件配套费用。”

RISC与CISC,本质上并无优劣之分,只有适用场景的不同。例如属于复杂指令集的x86架构,让英特尔与AMD处理器产品在CPU领域保持着绝对优势。因为桌面端或服务器端处理器相比移动端能够较少考虑功耗与续航问题,因此它们的性能足够强悍,不会被CISC的特性拖累,反而可以更高效的执行复杂任务。但移动端计算机(手机、平板电脑等)的处理器在设计时,除了要考虑性能外,功耗与散热同样重要,这就给了RISC指令集发展空间,因此在移动端市场爆发时期,属于RISC指令集的ARM架构脱颖而出,目前占据了最多移动端市场,我们熟悉的高通骁龙系列与三星Exynos系列芯片均使用了ARM公司的IP核心。

RISC-V与ARM的诞生

ARM芯片的诞生十分有戏剧性。

1981年,刚成立3年的Acorn公司(橡果电脑有限公司)获得了英国广播公司生产电脑的订单。但那时处理器正处于8位与16位的更替时期,Acorn没有符合需求的芯片,于是它们转头向摩托罗拉寻求帮助 。摩托罗拉虽然提供了16位芯片产品,但由于芯片中断响应时间过长,最终没有通过评估。

Acorn决定向英特尔寻求帮助,希望对方提供一些80286处理器的设计资料和样品,但是却遭到回绝。Acorn一气之下决定自己制造芯片,经过多年的艰苦奋斗,两位来自剑桥大学的科学家最终完成了自己的芯片设计,并将它命名为Acorn RISC Machine,也就是ARM芯片,RISC就是前文提到的精简指令集。1990年11月27日,Acorn公司正式改组为ARM计算机公司。

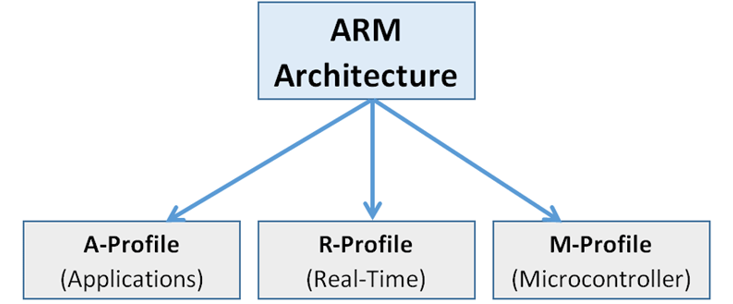

经过多年的发展,如今的ARM早已不再是面对英特尔时“吃瘪”的小公司。当前ARM的Cortex核心已经得到市场的广泛认可,小到儿童手表、智能手机,大到数字电视、智能汽车、CT机,基于ARM架构的芯片已经覆盖先当多电气设备。ARM在移动端俨然已获得当年英特尔在处理器领域的地位。

ARM处理器架构分类

ARM处理器架构分类

图源 | Circuit Digest

屠龙者终成“恶龙”,那RISC-V这位 “勇士”又该怎么挑战ARM呢?我们先来认识一下RISC-V,并对比一下它们有什么区别。

RISC-V是加州大学伯克利分校 RISC ISA 设计的第五版。罗马数字“V”表示“变体”和“向量”,表示它支持一系列计算机体系结构研究。2010年,当时加州大学伯克利分校计算机系教授Krste Asanović 博士想要制定一个像Linux 一样的开源计算机系统规范。

在获得了David Patterson 博士的帮助后,它们于1990 年代开始RISC 芯片的设计工作,最终形成了 RISC-V。后来,RISC-V 基金会成立,旨在维护、宣传和管理RISC-IV IP,并协助厂商相互合作。此后由于美国对先进芯片的出口限制,RISC-V基金会从美国加利福尼亚州转移到瑞士工作。目前,它在 50 个国家和地区拥有约 1,000 多个会员(公司),其中包括华为、阿里巴巴、谷歌、英伟达 和 IBM 等重量级企业。

RISC-V VS ARM

RISC-V与ARM一样,都是属于RISC精简指令集,目前网上已经有很多媒体分析过这两种指令集开源与封闭、免费和收费的区别,今天我们一起看看它们在架构上有什么异同。

从内存交互方式看,RISC-V与ARM都使用加载-存储体系结构,即只有在存和取数据时可以访问存储器(内存),运算型指令操作均在CPU内完成,最终的计算结果也将写回内存中。但两种指令集的字节顺序(Endianness)不同,字节顺序是字节在存储在内存中或通过数字链接传输时被安排成更大数值的顺序,可根据高位优先与低位优先分成两种:大端模式(高位优先,Big-endian)或小端模式(低位优先,Little-endian)。

ARM处理器默认是小端模式,但也支持大端模式,而RISC-V仅支持小端模式,两种模式没有优劣之分,仅在数据处理时有不同的优点。

从架构复杂程度看,RISC-V本身非常简单,基础指令集则只有40多条,加上其他的模块化扩展指令总共几十条指令,其规范文档仅有145页,而“特权架构文档”的篇幅也仅为91页。ARM由于是一种封闭的指令集架构,所有厂商在采用ARM IP核心后,不能基于原有设计自行更改芯片,企业只能调整自身需求来迎合ARM核心。经过多年的发展,ARM指令集变得极其复杂和繁琐,相应的架构文档有上千页。这也变相导致了ARM处理器的研发门槛要远高于RISC-V。

从定制化方面看,RISC-V没有针对任何功能、架构或目标进行过度优化,因此它能适用于几乎所有计算场景。ARM针对智能手机的优化程度要高于对笔记本电脑、台式机和服务器的优化程度。正因如此,ARM芯片在移动端领域有着无可撼动的统治力。

总结

从以上内容可以看出,RISC-V与ARM虽然同为RISC精简指令集,但在指令集特性上各有不同。除了开源与免费,简单和低开发门槛也是RISC-V挑战ARM的杀手锏。

而目前RISC-V和ARM的主要差距体现在上下游产业生态和规模化应用上,这是摆在RISC-V阵营的玩家们面前最大的挑战和难题。

审核编辑:刘清

-

RISC-V有哪些优缺点?是坚持ARM方向还是投入risc-V的怀抱?2024-04-28 2276

-

RISC-V的MCU与ARM对比2024-05-27 1879

-

浅析RISC-V领先ARM的优势2024-06-27 1344

-

rIsc-v的缺的是什么?2024-07-29 1208

-

Arm与RISC-V架构的优劣势比较2025-02-01 1764

-

浅谈RISC-V2018-09-11 9802

-

RISC-V PC计划,X86和Arm迎来新挑战?2020-11-26 2203

-

ARM与RISC-V架构的区别是什么?2021-04-25 6521

-

两大架构RISC-V 和 ARM 的各种关系2023-06-21 1294

-

谈一谈ARM上市与RISC-V2023-09-30 1412

-

RISC-V发展迅猛 ARM有点坐不住了2020-02-27 5113

-

未来ARM和RISC-V如何共存2022-09-05 2418

-

ISA ARM 对比 RISC-V2024-09-10 2994

-

RISC-V 与 ARM 架构的区别 RISC-V与机器学习的关系2024-12-11 5233

-

RISC-V和ARM有何区别?2025-06-24 2230

全部0条评论

快来发表一下你的评论吧 !