CMOS平面互补场效应晶体管工艺流程

场效应管

描述

平面互补场效应晶体管工艺流程

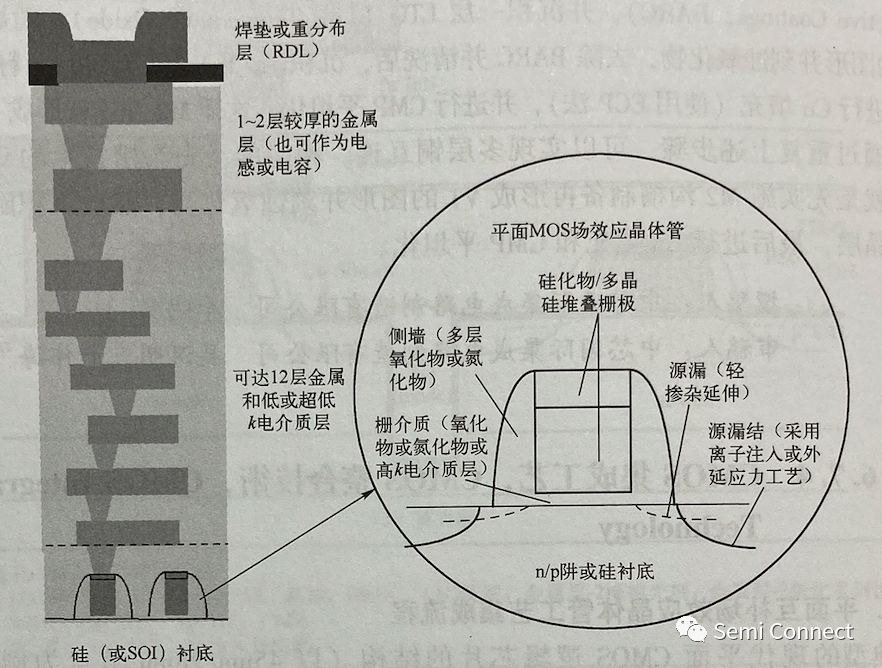

典型的现代平面CMOS 逻辑芯片的结构(以 45nm/28nm 节点为例)如图所示。

典型的衬底是p型硅或绝缘体上硅(SOI),其直径为 200mm 或300mm;在多层铜互连中,最上面两层金属较厚(常被用于制造电感或电容),顶层的铝层用于制造封装用的键合焊盘。局部放大图显示了 MOS 场效应晶体管的多晶硅和硅化物栅叠层、高K栅介质、轻掺杂(LDD) 或源漏扩展区、外延生长应变硅源漏等细节。

CMOS 场效应晶体管(28nm 节点)的特征包括钴或镍硅化物多晶硅栅叠层、氮氧化硅或高k材料(氧化铪)栅介质、多层(Oxide-Nitride-Oxide, ONO)侧墙、轻掺杂(LDD) 或源漏扩展结 (S/D Extension)和镍硅化物 S/D 深结。

内部核心逻辑电路的场效应晶体管的典型工作电压为 0.9~1.1V,沟道长度为 30~40nm,栅介质等效氧化硅厚度为 1.5~2nm, S/D 扩展结厚度为 15~20nm。I/0 电路(连接外围芯片的接口)场效应晶体管的典型工作电压是 1.5V、1.8V 和2.5V,相应的沟道长度为 100~200nm,栅介质厚度为3~6nm,S/D 扩展结厚度为 25~30nm。

核心逻辑电路较小的工作电压是为了减小操作功耗。在 45nm/28nm CMOS节点都采用了沟道工程,通过沿场效应晶体管沟道方向施加应力来增强迁移率(如针对 n-MOS 沟道中电子施加张应力和针对p-MOS 沟道中空穴施加压应力)。 28nm CMOS 节点都采用了 SiGe 应变硅外延 S/D (用于p-MOS)和应力记忆技术(用于n-MOS)。

在28nm/20nm 及以下的节点还采用了新的模块技术,如新的高k介质和金属栅叠层,双应力 SiC 或 Si :P 外延与应力记忆技术(用于n-MOS 源漏)。在16nm/ 14nm/10nm/7nm 及以下的更先进节点,都采用子非平面沟道器件 FinFET。 现代平面 CMOS 场效应晶体管和金属互连的制造工艺流程如图所示。

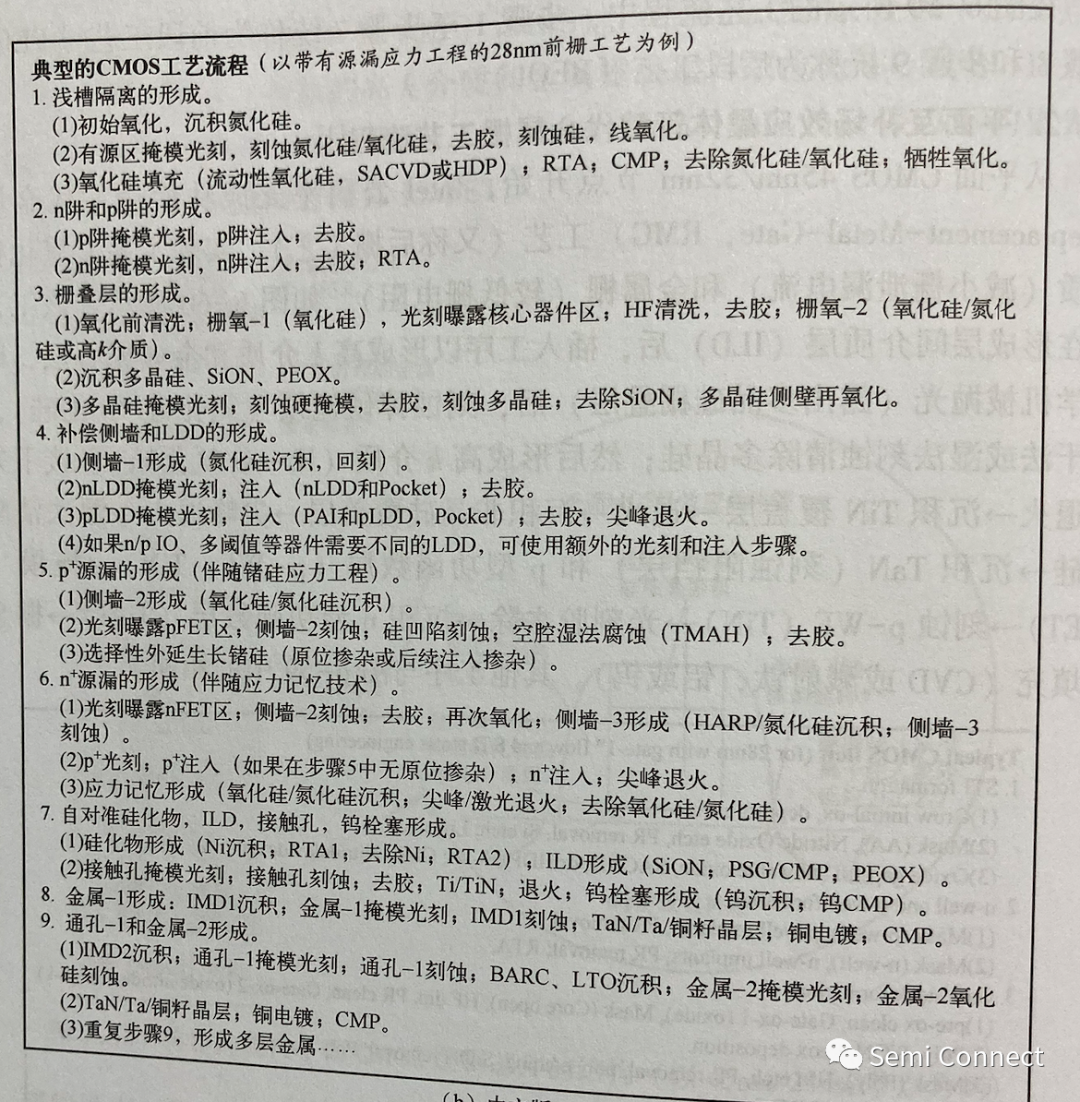

以平面 CMOS 28nm 节点为例,其制造工艺流程如下所述。

(1)形成浅槽隔离 STI,然后形成n阱区城(用于 pMos)和p阱区域(用于nMOS),分别对阱区域进行选择性注入掺杂。

(2)生长n-MOS 和 p-MOS 栅氧化层,形成多晶栅叠层和图形化,再氧化以保护多晶栅叠层的边缘,然后形成补偿侧墙来调整 n/p MOS LDD 的位置。

(3)形成锗硅(SiGe)外延p-MOS 的源漏;再形成n-MOS 的源漏,并进行应力记忆技术和源漏注入掺杂。

(4) 形成镍硅化物,沉积层间介质层 (ILD)后,通过图形化,刻蚀和钨栓塞(W-Plug)填充形成接触孔。至此,n-MOS 和 p-MOS 晶体管己经形成。

(5) 通过单镶嵌技术形成第一层铜 M1,其他的互连通过双镶嵌技术来实现。通过重复双镶嵌技术实现多层互连。最顶层的两个金属层和铝层用于制造无源器件和键合焊盘。

在图2所示的工艺流程中,步骤 1至步骤7统称为前段工艺(FEOL),步骤8和步骤9统称为后段工艺 (BEOL)。

审核编辑:刘清

-

鳍式场效应晶体管制造工艺流程2025-02-17 3706

-

互补场效应晶体管的结构和作用2025-01-24 5154

-

互补场效应晶体管点火和只用一个场效应晶体管点火与PWM的区别?2024-05-21 541

-

场效应晶体管工作原理2023-05-16 2441

-

MOSFET和鳍式场效应晶体管的不同器件配置及其演变2023-02-24 13757

-

场效应晶体管的选用经验分享2021-05-13 1980

-

如何进行场效应晶体管的分类和使用2020-07-02 2132

-

场效应晶体管的分类及作用2019-05-08 4288

-

场效应晶体管在电路中的特别应用,你未必全都清楚2019-04-16 3533

-

如何判断场效应晶体管方向,学会这几步轻松搞定2019-03-29 3902

-

隧穿场效应晶体管是什么_隧穿场效应晶体管的介绍2018-10-19 4825

-

功率场效应晶体管(MOSFET)原理2012-08-20 5481

-

场效应晶体管的分类及使用2010-01-13 993

-

什么是场效应晶体管2009-05-24 7706

全部0条评论

快来发表一下你的评论吧 !