WCH RISC-V-CH307V(优点熟悉版)

描述

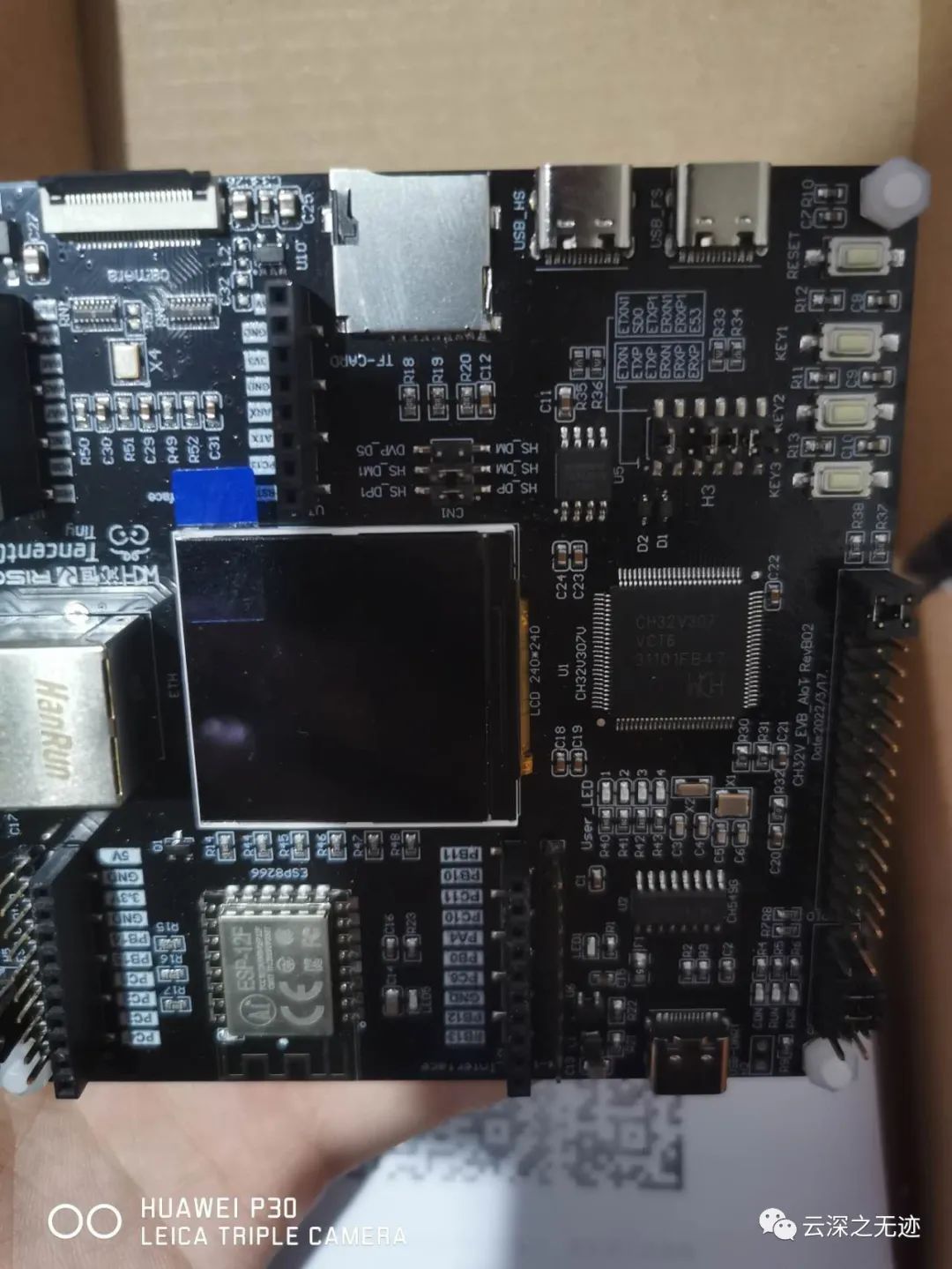

拿到了WCH的一块板子:

方方正正的盒子,展会上面还看到他家的这个芯片来着

堆料很足的

就是这样

emmmm,看过一些RISC-V的书,也经常看它的新闻,ARM一家独大的场面,是所有人都不愿意看到的局面。所以大家都押注这个开源的东西,以前淘宝看见卖四五十块钱的板子,我后来想这么多板子了,就没有买。这次终于拿到一个板子,略微深入的探索一下。

不过我可以说,10年前是51的天下,五年前是ARM的天下,但是我说不准后5年的局面,可能是RISC-V,ARM平分天下的格局吗?有可能的,所以我这里也在赌一个未来,现在学是投资未来。

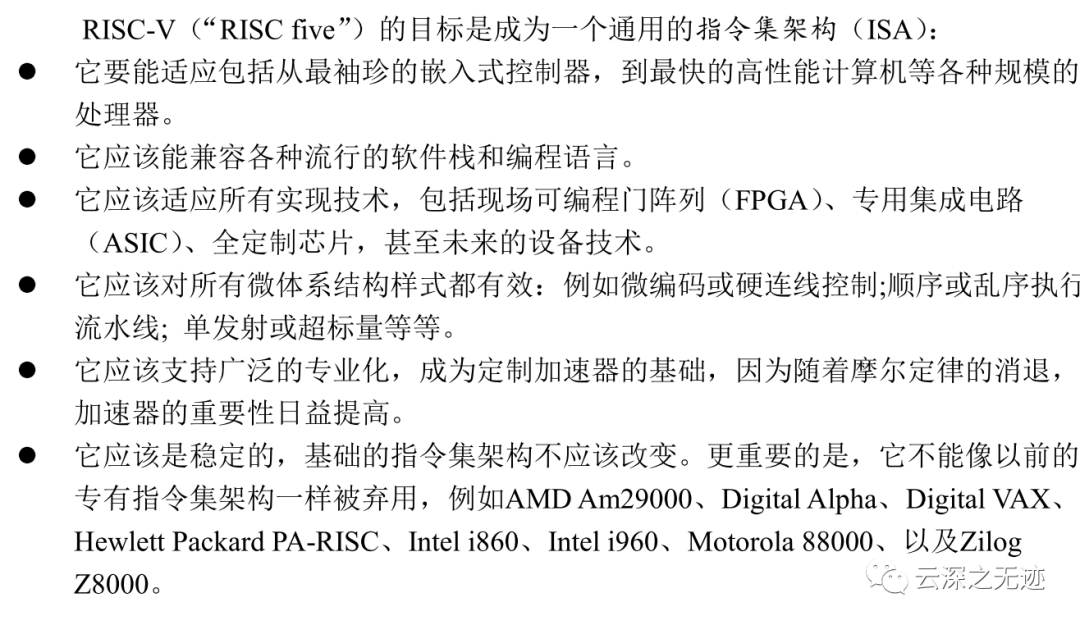

嗯,上面的内容摘自:

这个是小册子,想看可以找我

首先RISC-V是一种开源的架构,也是年轻具有活力的CPU设计,在Intel,51,ARM,PowerC的前辈加持下,它就像被基因工具改造的孩童一般。出生就有了无限可能。

害,学就对了。

Logo

就单看这几个赞助的就知道了

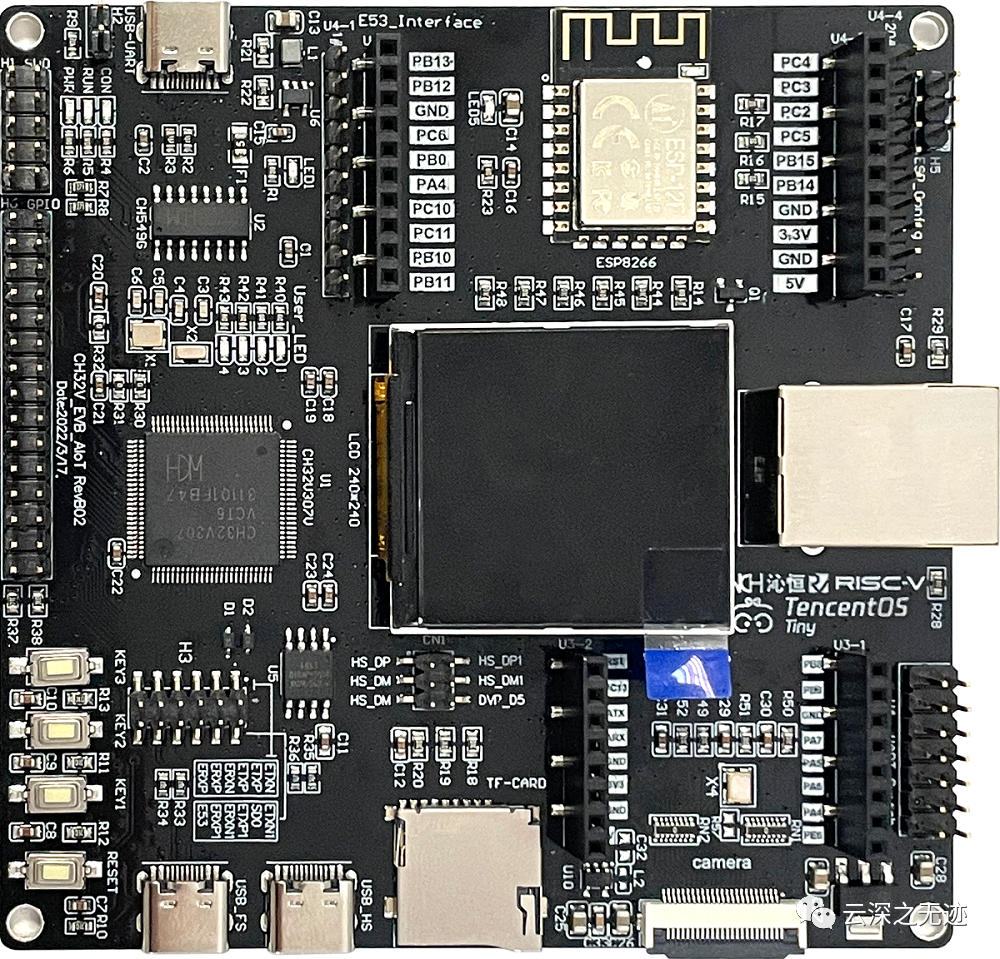

全家福

学有余力推荐这个,1600+页,很攒劲儿,搞懂去中科院没啥难度吧~

继续聊板子,具体的外设就不看了,不重要,直接去数据手册看。

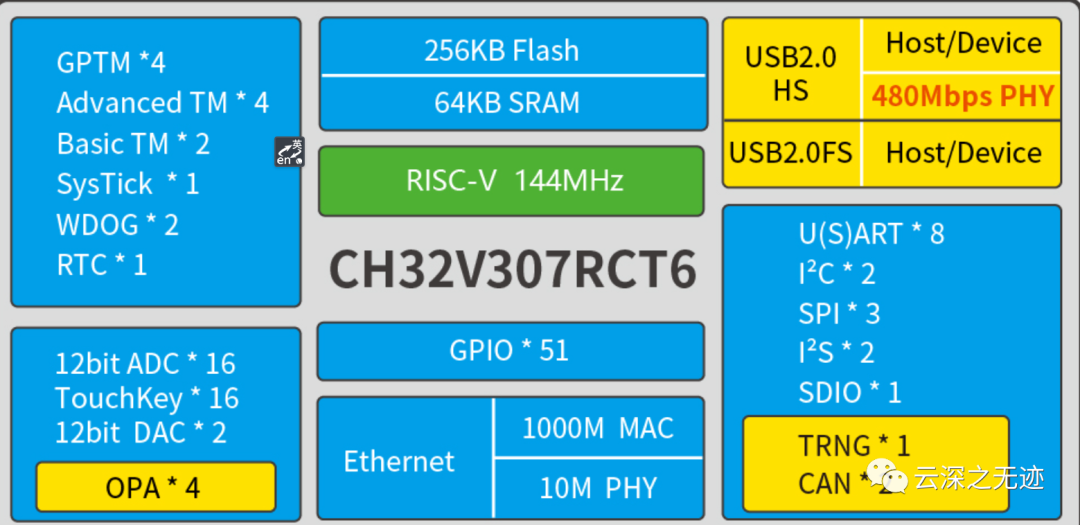

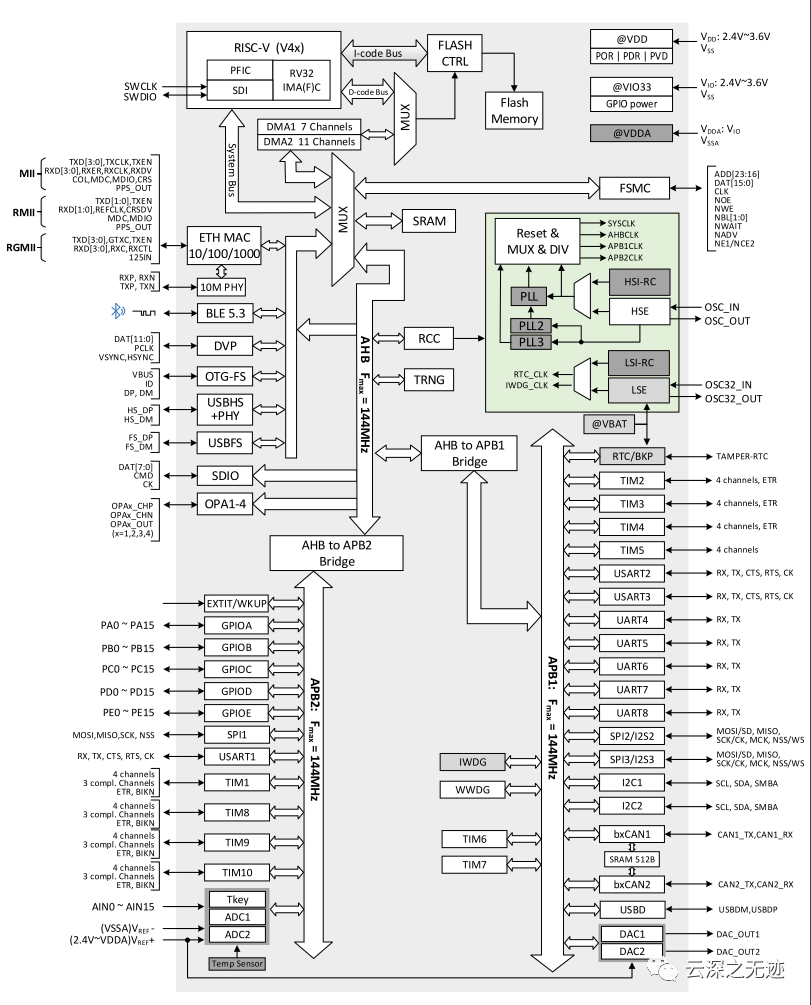

CH32V305/7系列是基于32位RISC-V设计的互联型微控制器,配备了硬件堆栈区、快速中断入口,在标准RISC-V基础上大大提高了中断响应速度。加入单精度浮点指令集,扩充堆栈区,具有更高的运算性能。扩展串口UART数量到8组,电机定时器到4组。提供USB2.0高速接口(480Mbps)并内置了PHY收发器,以太网MAC升级到千兆并集成了10M-PHY模块。

怎么说呢,该有的都有,而且CH32,难免让人有点感觉是致敬STM32

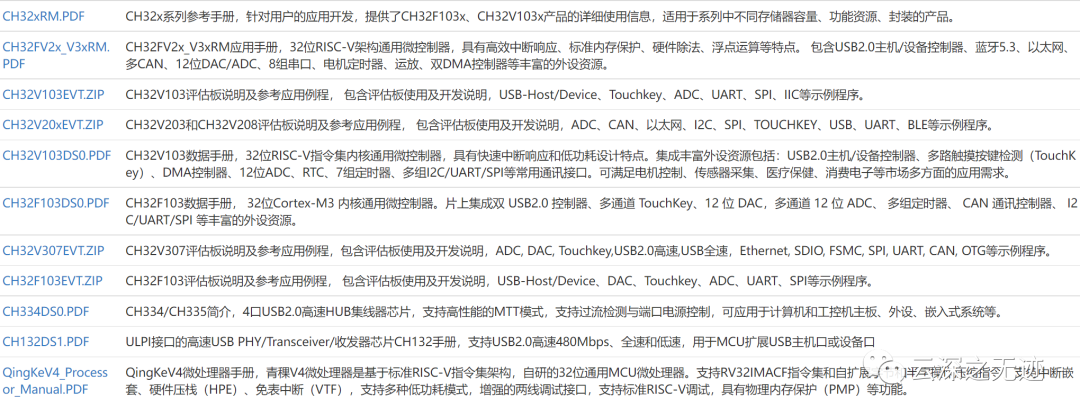

优点是全中文,资料较为齐全

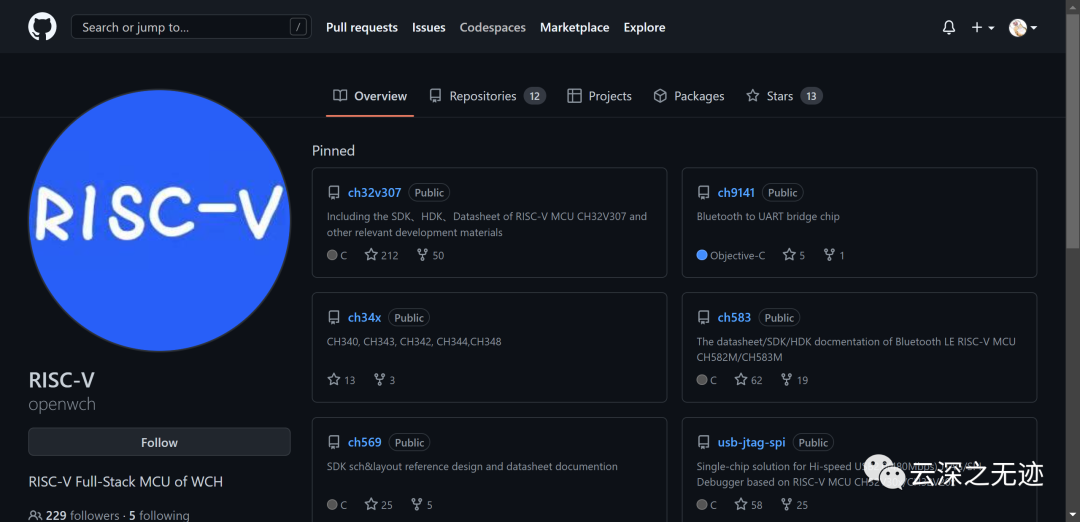

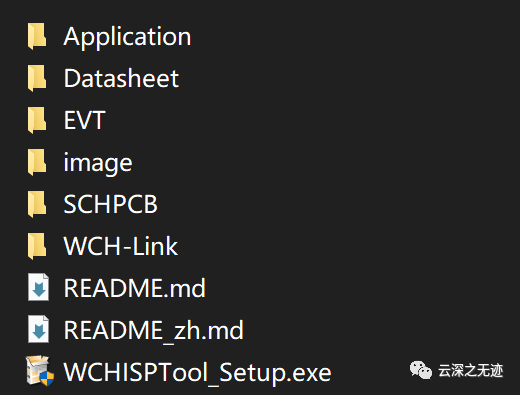

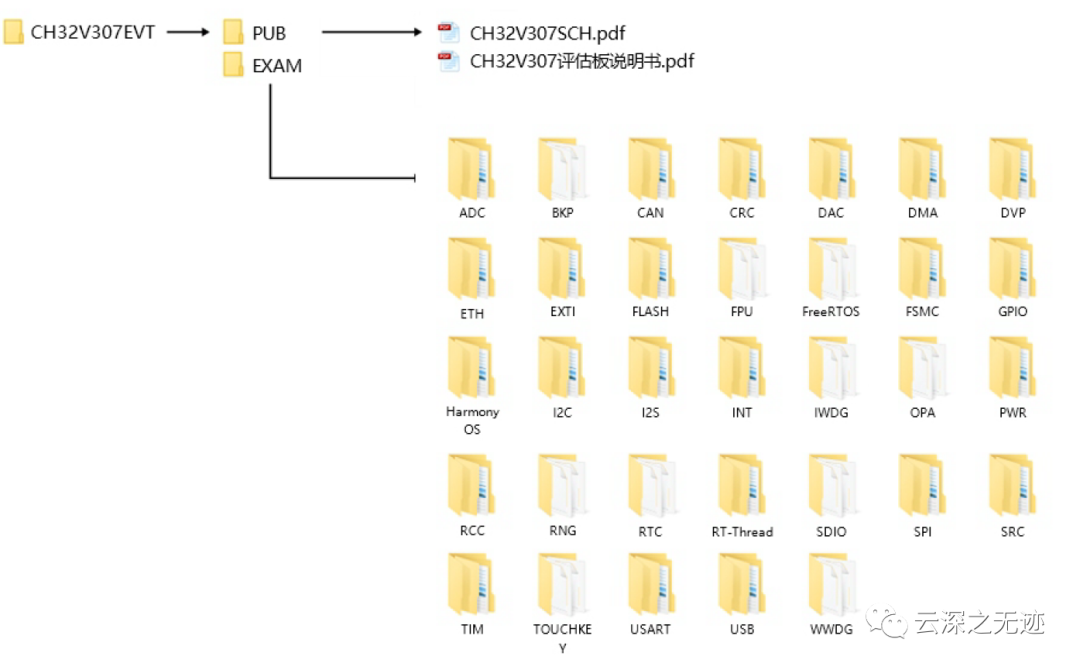

都可以在Gituhb上面找到,官网也行

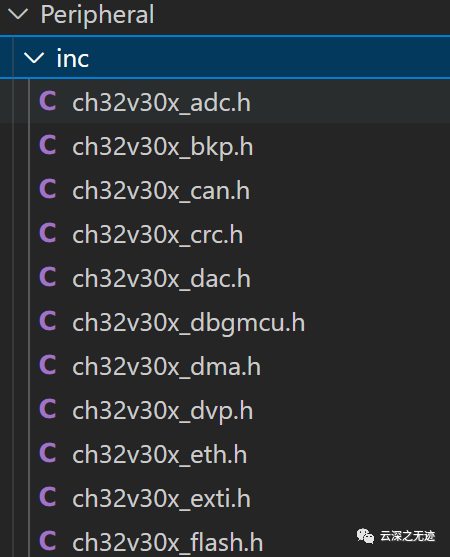

资料齐全

代码一会儿说

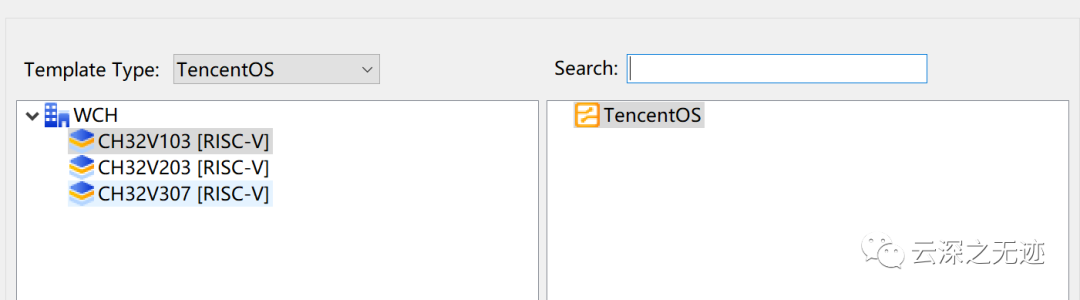

自带的IDE,还可以选择RTOS

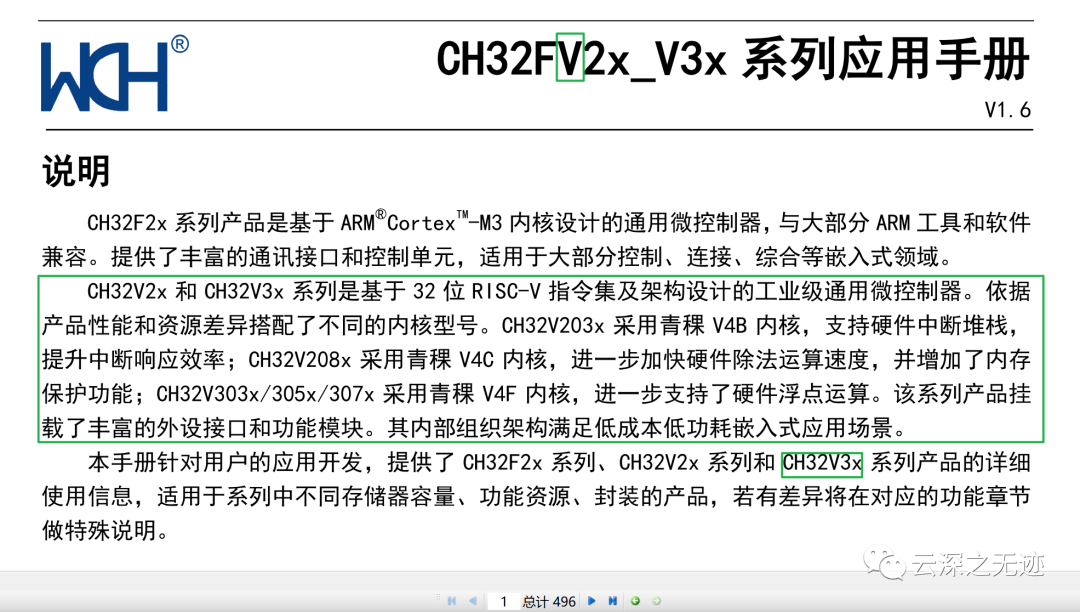

但是寄存器这些是ARM和RISC-V混合在一起一个文件的

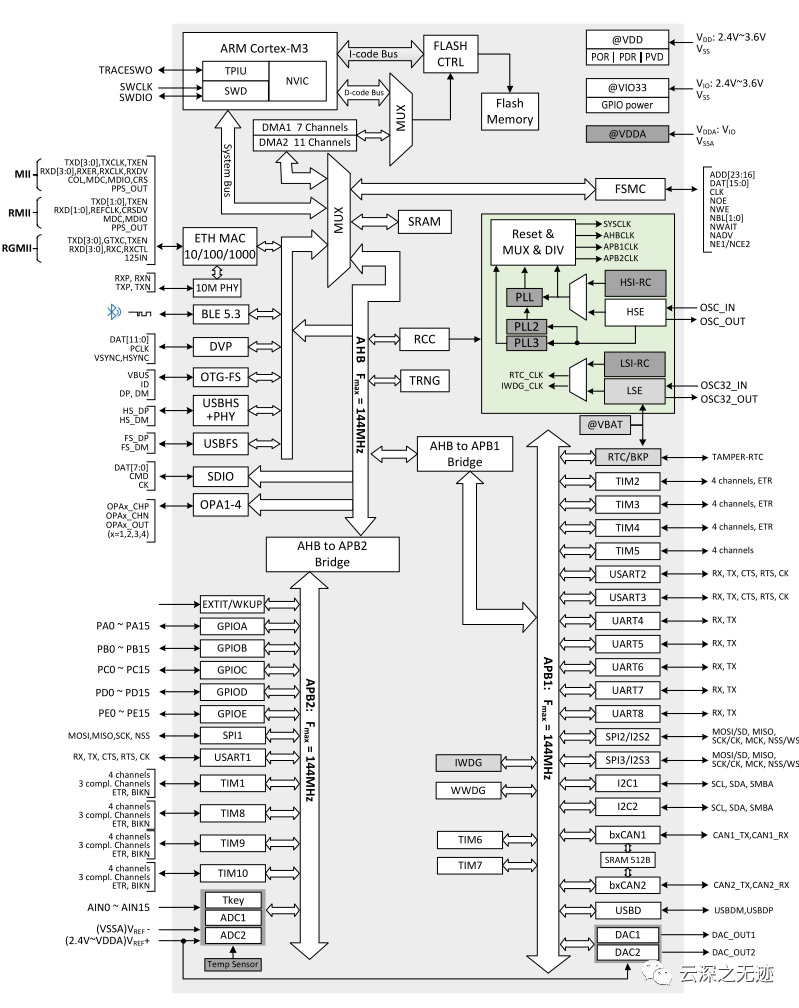

ARM的架构

WOC,一模一样的

系统中设有:Flash 访问预取机制用以加快代码执行速度;通用 DMA 控制器用以减轻 CPU 负担、提高效率;时钟树分级管理用以降低了外设总的运行功耗,同时还兼有数据保护机制,时钟安全系统保护机制等措施来增加系统稳定性。 l 指令总线(I-Code)将内核和 FLASH 指令接口相连,预取指在此总线上完成。 l 数据总线(D-Code)将内核和 FLASH 数据接口相连,用于常量加载和调试。 l 系统总线将内核和总线矩阵相连,用于协调内核、DMA、SRAM 和外设的访问。 l DMA 总线负责 DMA 的 AHB 主控接口与总线矩阵相连,该总线访问对象是 FLASH 数据、SRAM 和外设。 l 总线矩阵负责的是系统总线、数据总线、DMA 总线、SRAM 和 AHB/APB 桥之间的访问协调。 l AHB/APB 桥,为 AHB 总线和两个 APB 总线提供同步连接。不同的外设挂在不同的 APB 总线下,可以按实际需求配置不同总线时钟,优化性能。

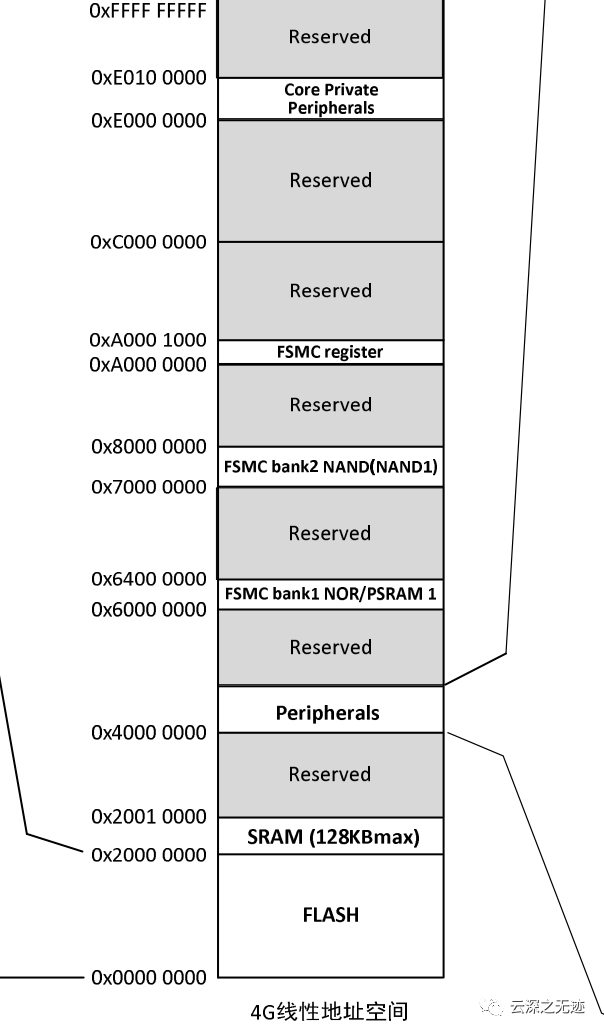

ARM的和RISC—V的储存空间,它们都在一个 4GB 的线性空间寻址。系统存储以小端格式存放数据,即低字节存放在低地址,高字节存放在高地址。 Emmmm,看STM32的感觉,一模一样的好吧。。。总之看下来:

架构中将内核、仲裁单元、DMA 模块、SRAM 存储等部分通过多组总线实现交互。设计中集成通用 DMA 控制器以减轻 CPU 负担、提高访问效率,应用多级时钟管理机制降低了外设的运行功耗,同时兼有数据保护机制,时钟自动切换保护等措施增加了系统稳定性。

这个定时器和STM32很一样

单纯的说数据手册没有意思,看看代码吧~

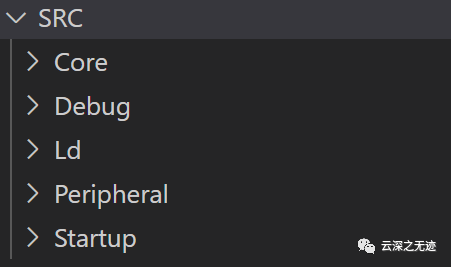

这个RISC-V的代码没有STM32库那么多

主要要操作的外设都放好了,直接调用

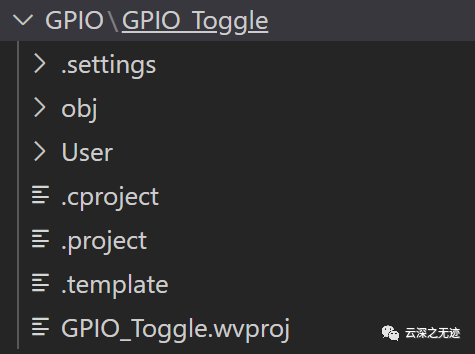

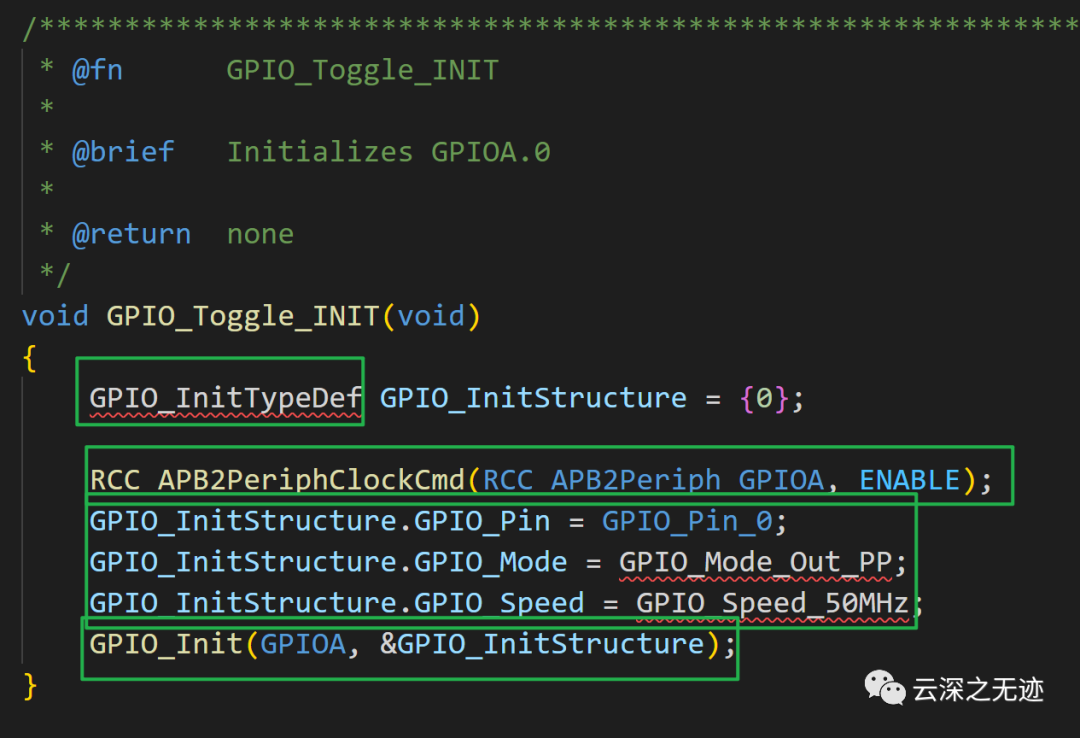

我简单的看一个GPIO

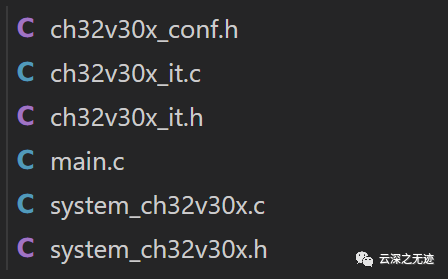

里面文件很少

PA0输出

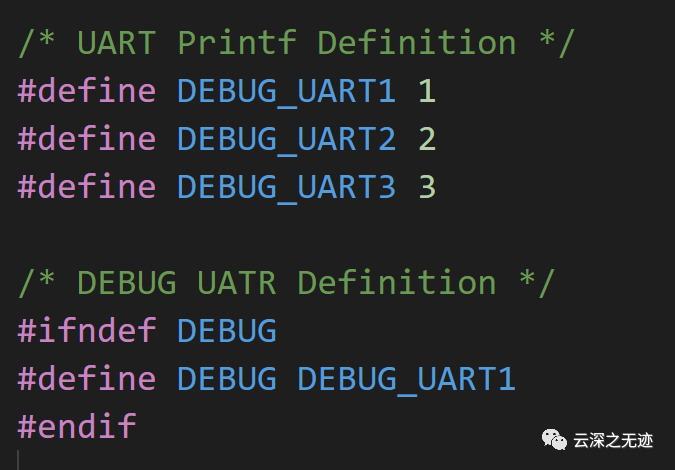

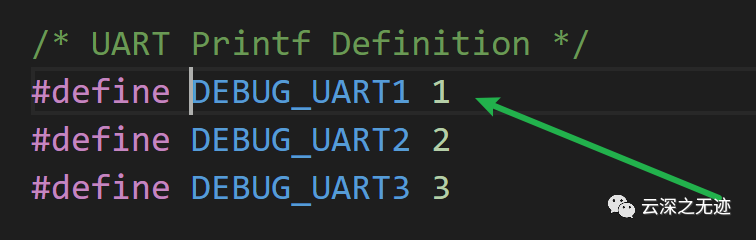

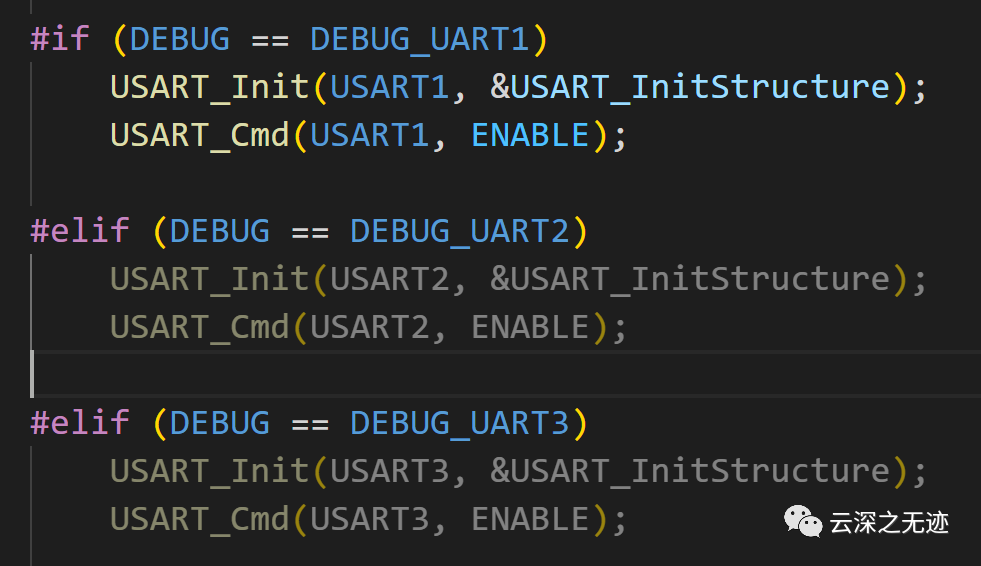

片子有3个串口,可以这样的自定义

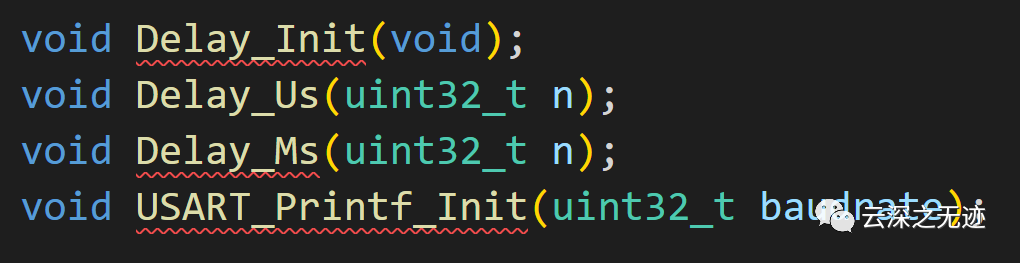

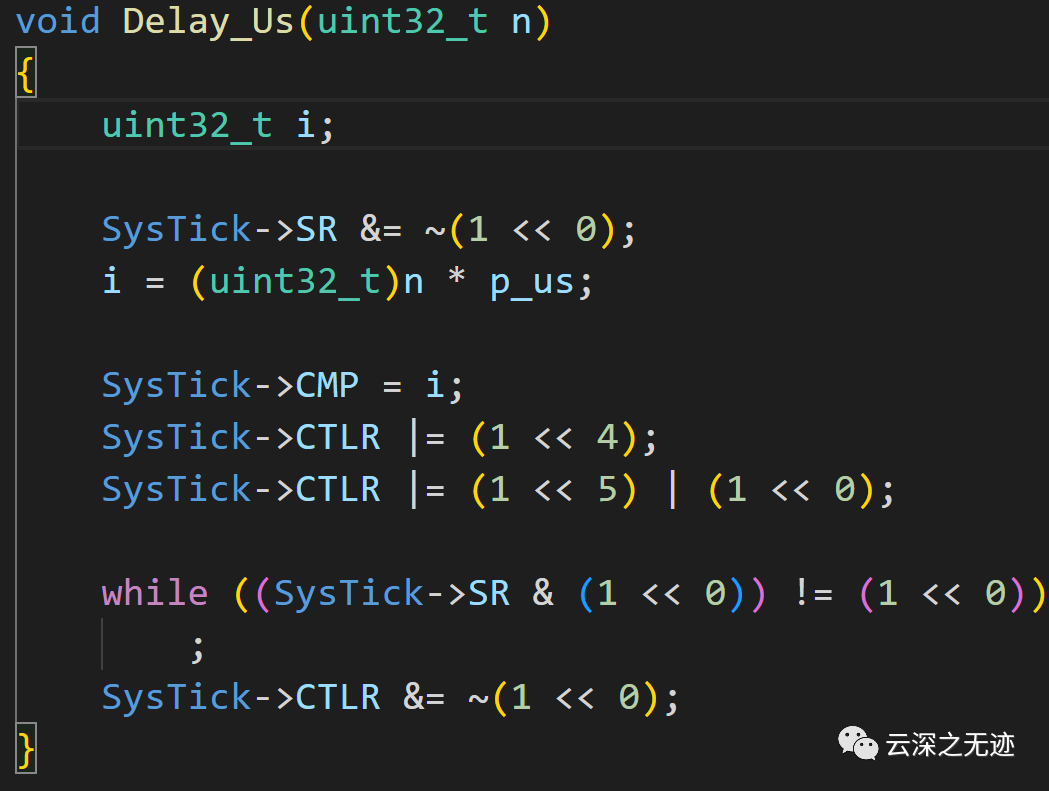

内部是三个关于延时的函数

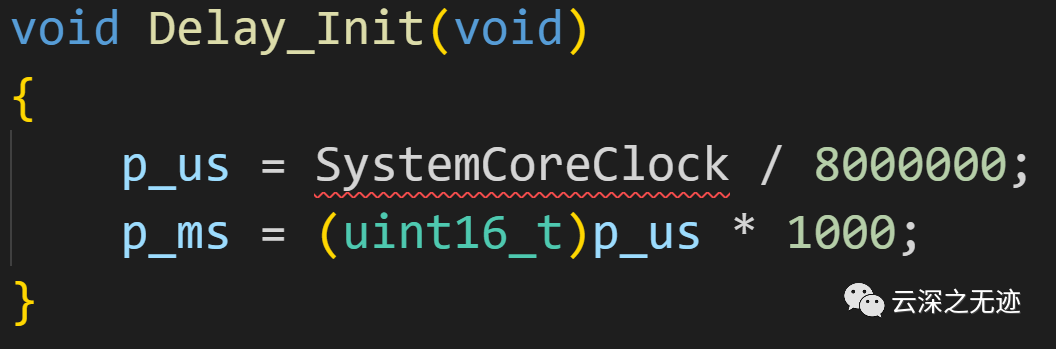

延时的初始化

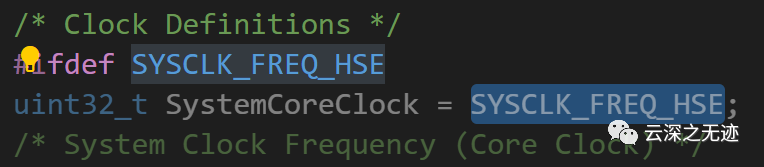

时钟源是HSE,晶振来的

然后这个是时钟核心频率

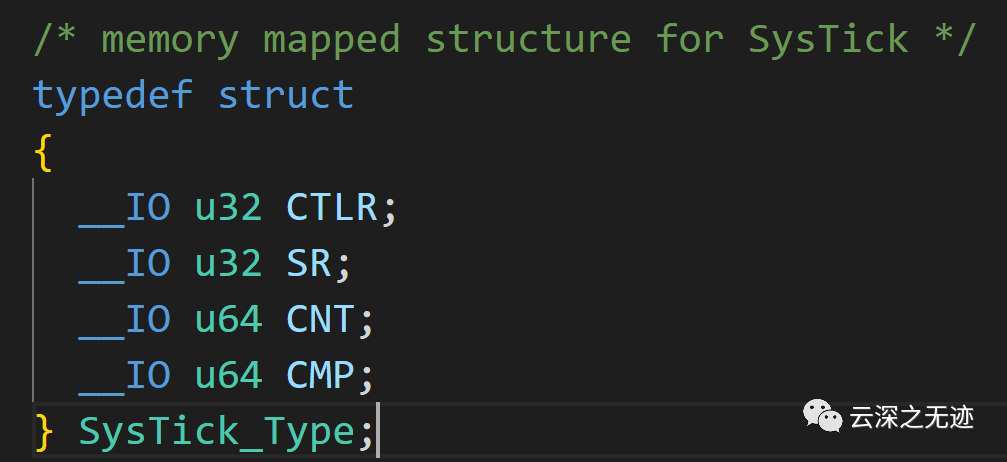

将这个位置的地址强转,这个是RISC-V内核的地址转换

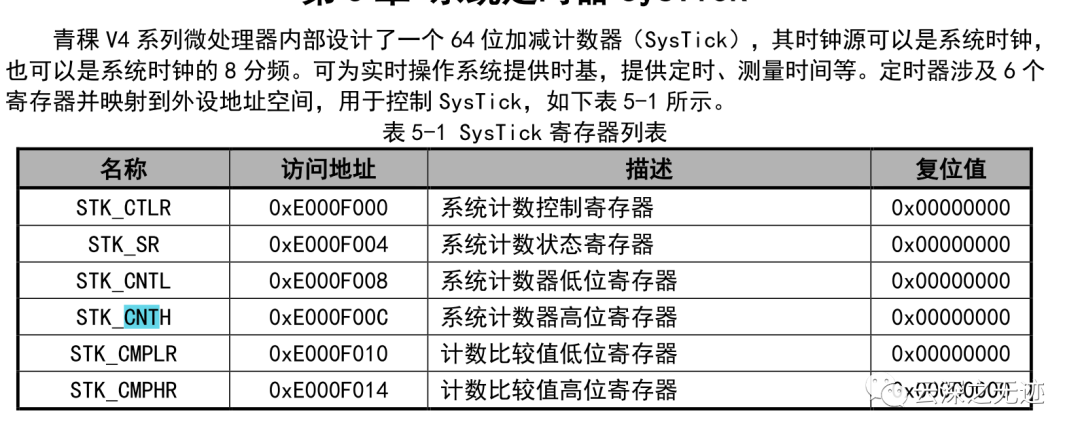

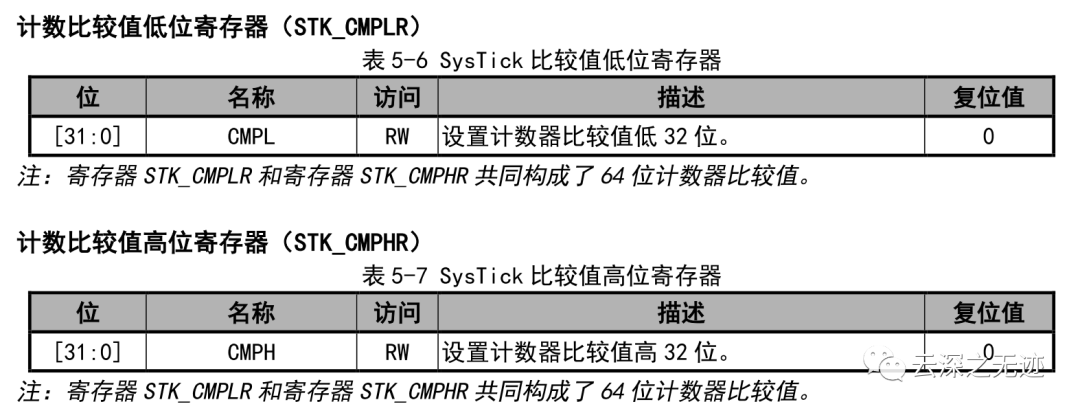

哦,原来是计数器

要不是平时老看数据手册,估计现在就晕了

这个就是上面计数器的封装了

这个之后研究吧,就是使用的计时器实现的延时函数

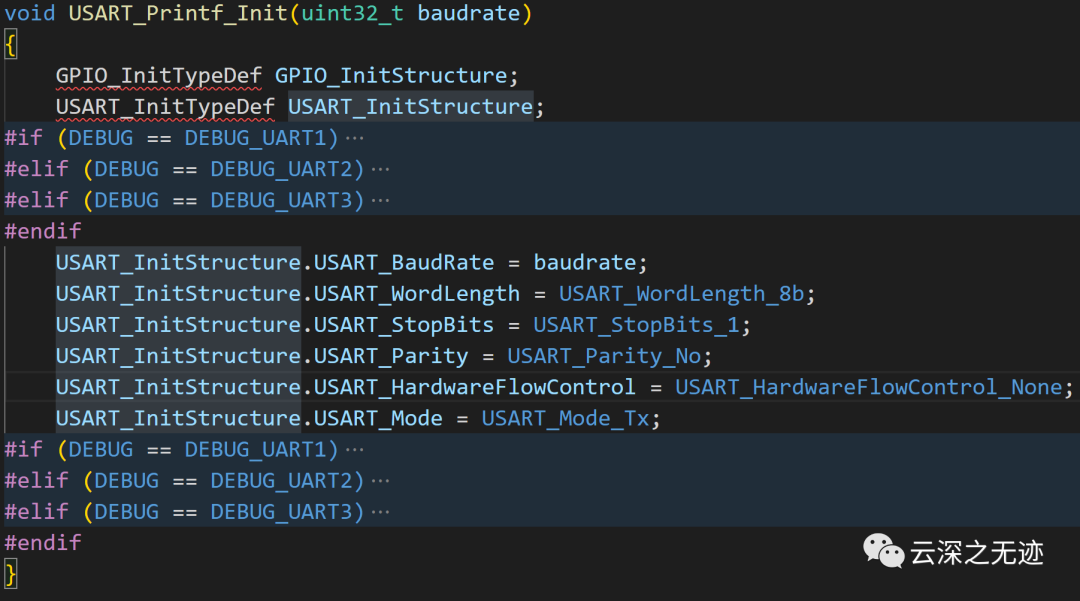

串口打印的函数

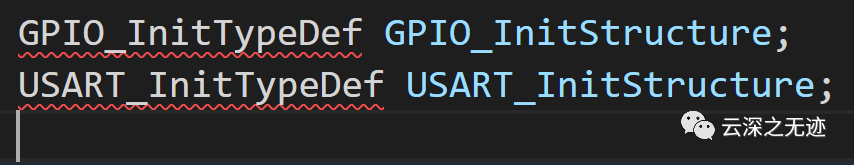

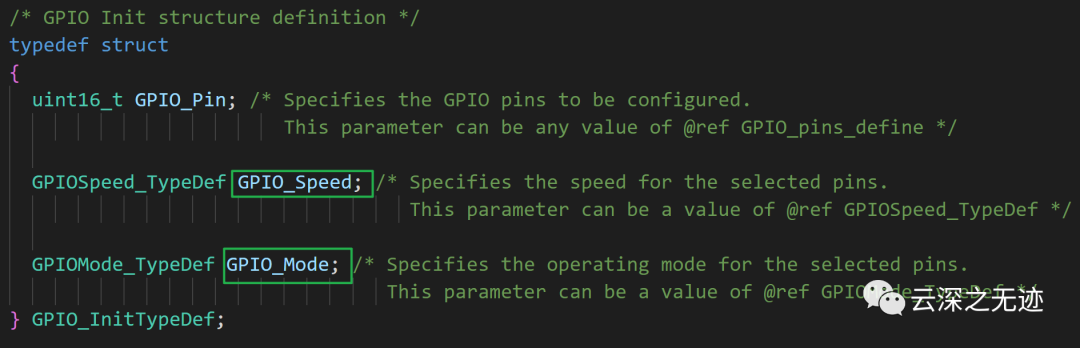

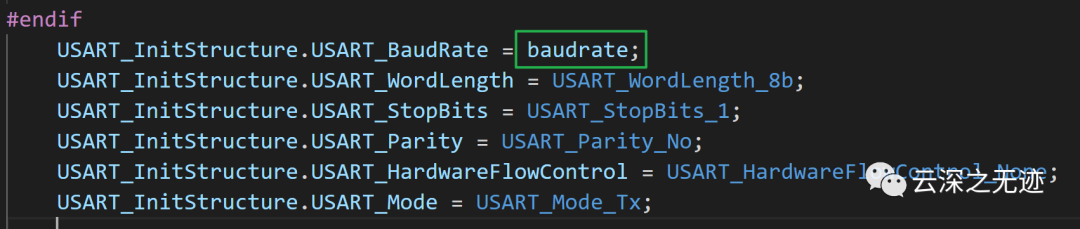

直接GPIO和串口外设,和STM32一模一样

不过比STM32少点

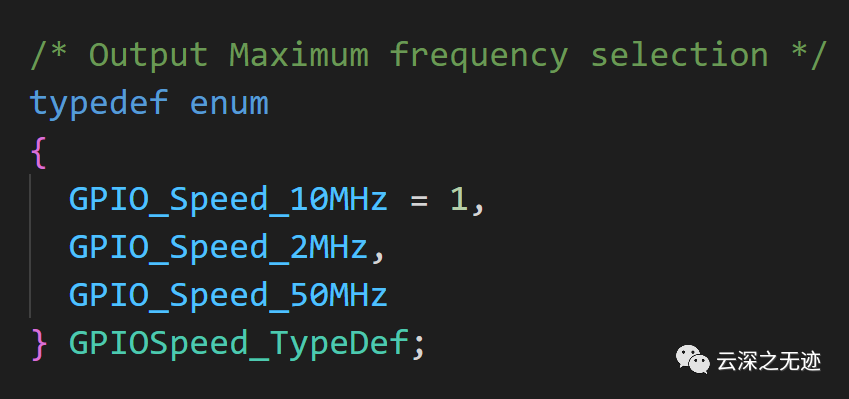

速度

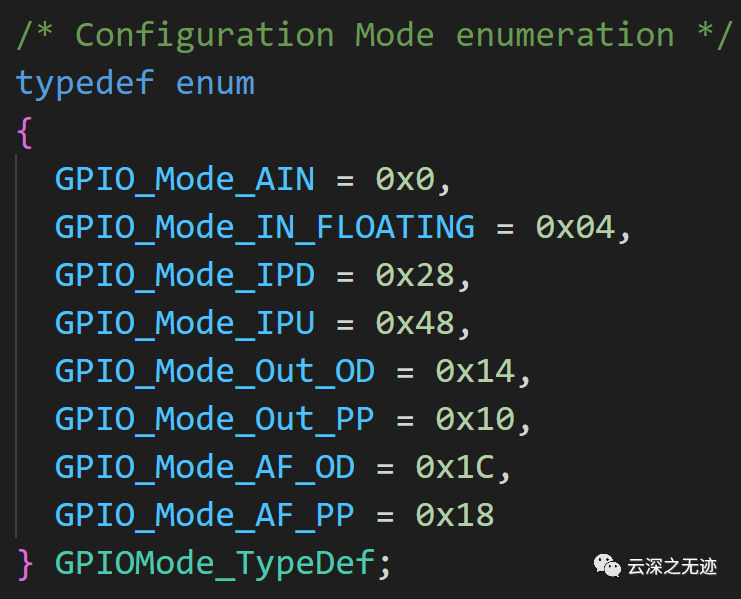

引脚模式

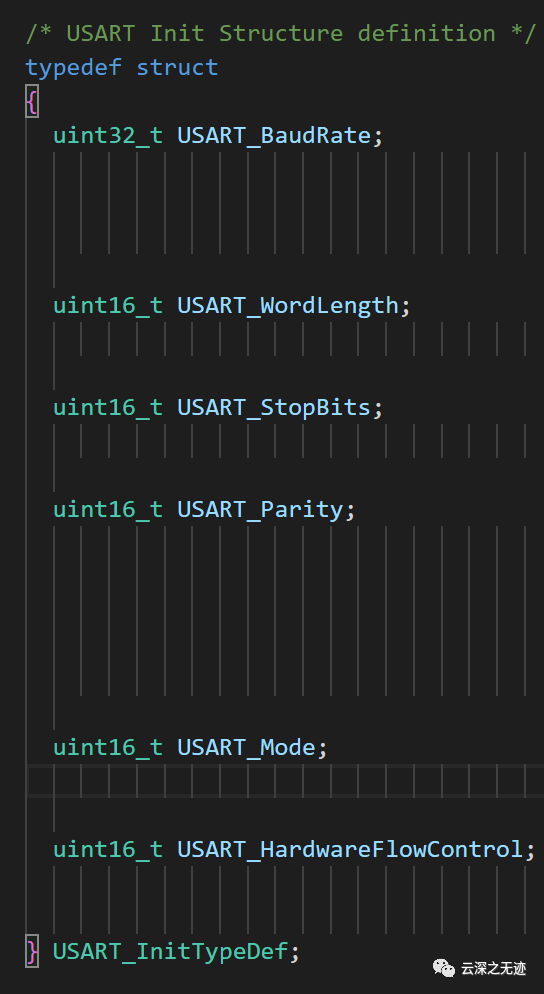

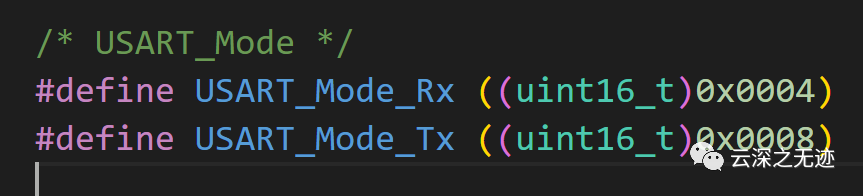

这个是串口的功能,最后一个是流控

这里有三个串口,提前放好

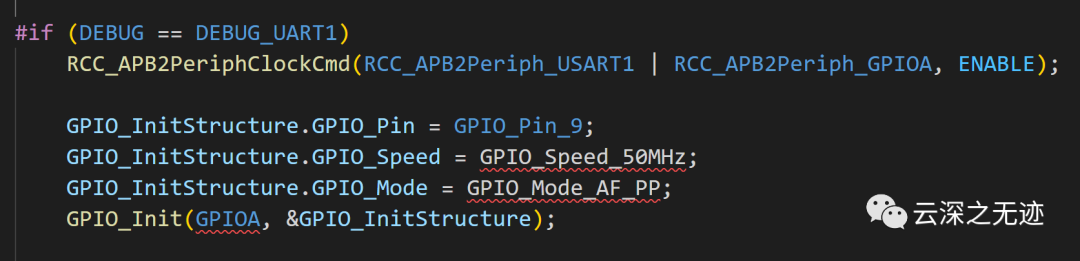

这里是判断要用第一个串口

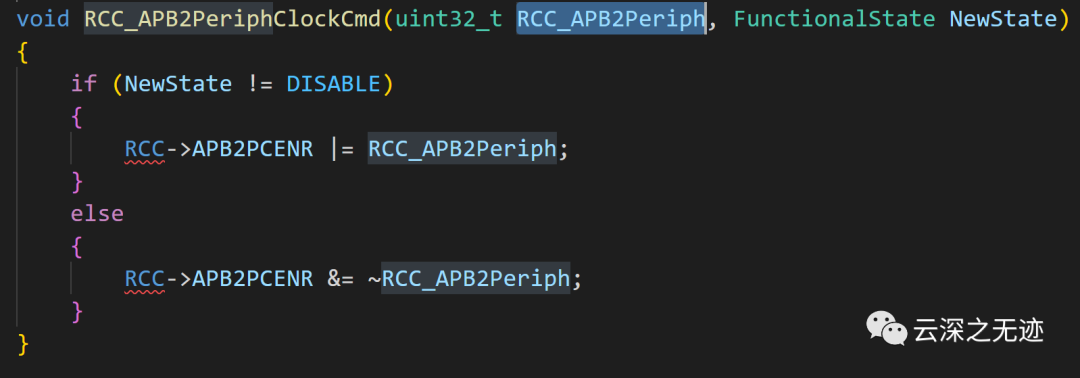

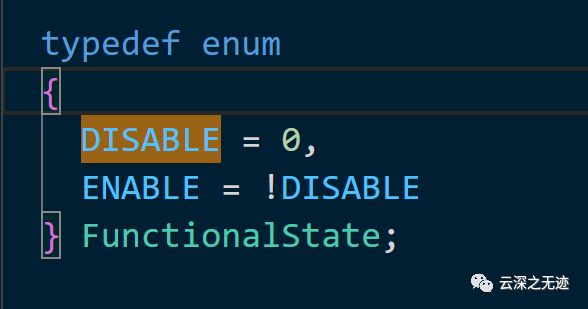

开启的是APB的时钟:Enables or disables the High Speed APB (APB2) peripheral clock.

是不是很眼熟

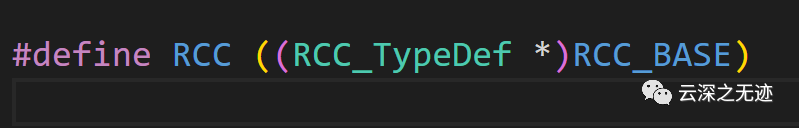

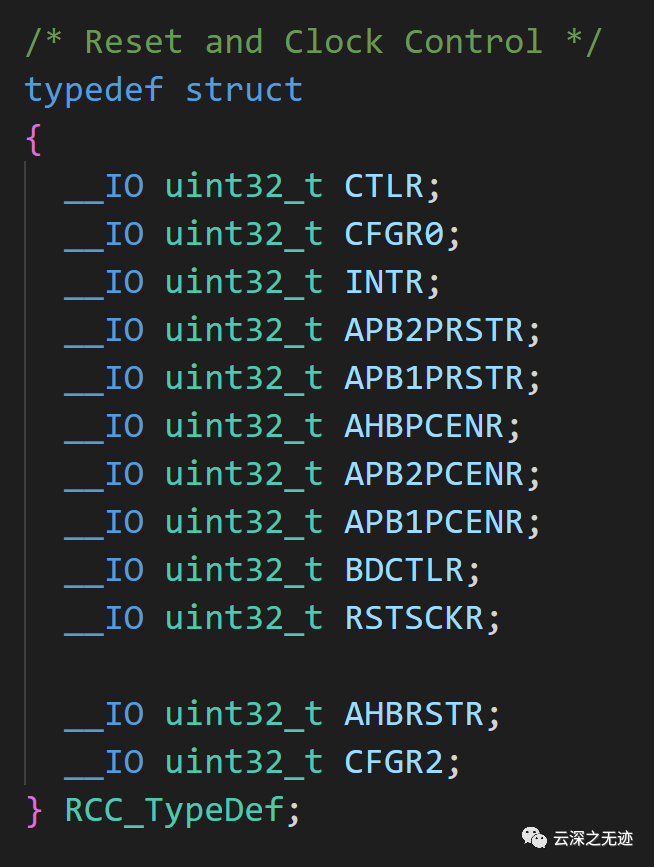

RCC的封装,一模一样的

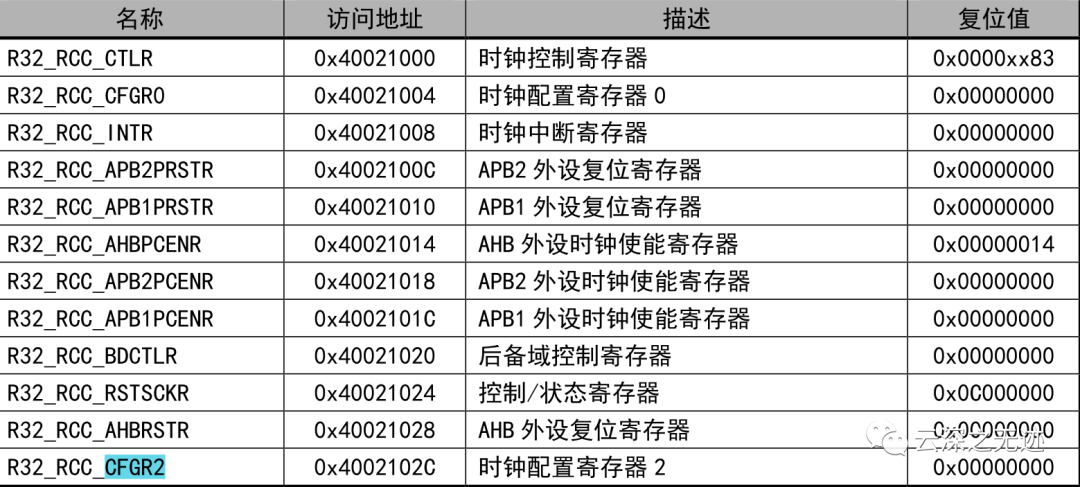

时钟控制器

都有的

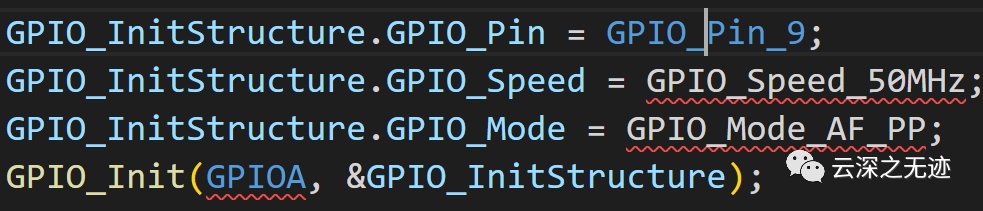

IO脚

上膛,一模一样

串口的初始化

最后的模式是发送

很简单的

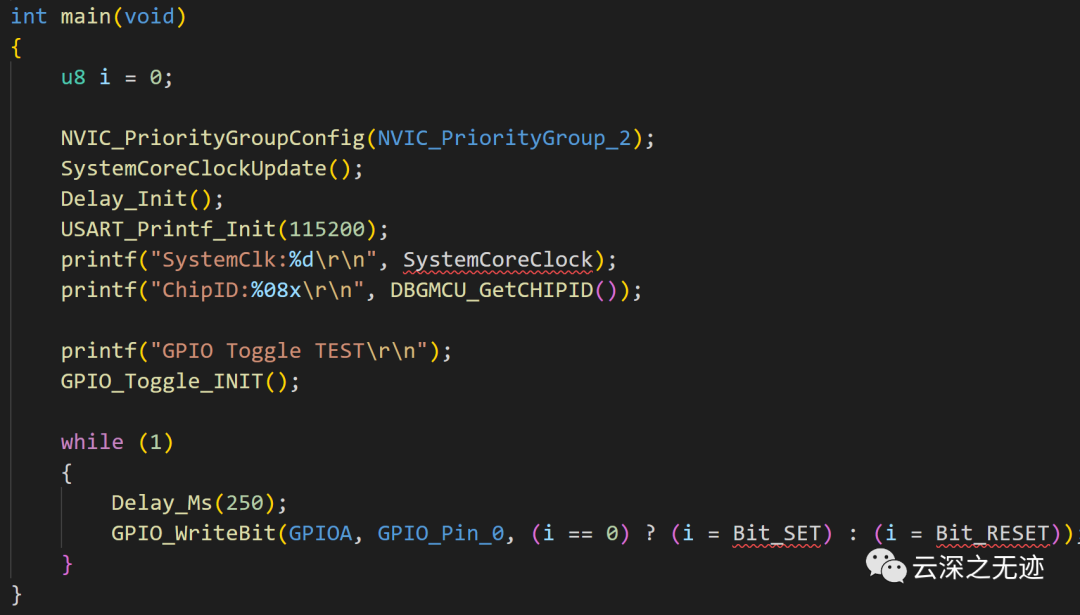

GPIO翻转,初始化结构体,开启时钟,把GPIO的参数装载,然后开启。

这个主函数明天写,实在太胃疼了,要睡觉了

审核编辑 :李倩

-

ch32优势 ch32v307可以做什么?2023-08-22 2932

-

ch32v307和stm32的区别2023-08-16 3708

-

【沁恒RISC-V体验】CH32V307EVT开发板初探2023-06-18 1555

-

RISC-V IDE MRS使用笔记(九):使用WCH-LinkW实现无线下载、调试2023-06-06 1577

-

基于RISC-V内核单片机移植RTOS实时操作系统(一)2023-01-31 4147

-

【沁恒微CH32V307评估板试用体验】重制一个WCH-Link调试器2022-07-17 9092

-

CH32V307是否实现了RISC-V手册中的mtime?2022-05-24 991

-

CH32V307通过WCH-LINK烧录后为什么无法运行?2022-05-16 1475

-

CH32V307黑色板子通过单独的wch-link下载程序失败如何解决?2022-05-13 4101

-

创建基于CH32V103R开发板时无法选择WCH-LINK怎么解决2022-04-28 4246

-

【名单已公布】【RISC-V专题】沁恒微CH32V307评估板免费试用2022-04-14 3587

-

CH32V307EVT 应用例程2022-03-31 1444

全部0条评论

快来发表一下你的评论吧 !