MAX9877音频子系统IC中的关断电流最小化

描述

介绍

在任何典型应用中,连接到的设备 I2C总线期望 SDA 和 SCL 线路在逻辑高电平状态下空闲。MAX9877音频子系统IC就是根据这一预期而设计的,因此,它依赖于SDA和SCL的逻辑高电平,以实现最小的关断电源电流。本文介绍了三种方法,当MAX9877处于关断状态时,SDA和SCL可能设置为逻辑低电平。

方法 1 — 附加弱上拉

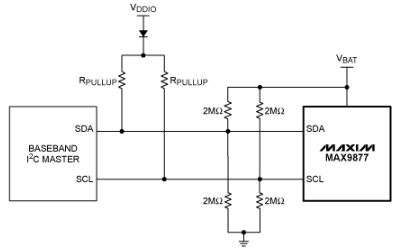

第一种方法为每个SDA和SCL使用额外的弱分压器,以在正常上拉电阻未激活时设置线路上的电压。图1显示了该方法的原理图。

图1.弱分压器用于设置SDA和SCL线路上的电压,而隔离二极管可防止上拉电压被迫接地时的电流消耗。

SDA和SCL上的一对2MΩ电阻将电池电压分压,使SDA和SCL的电压不超过I的最大额定值2C 主控。对于4.2V至3.2V的电池电压,SDA和SCL上的电压设定在2.1V至1.6V之间,足以超过MAX9877的输入高压。

二极管防止禁用的V迪奥如果电源的输出被迫接地,则不会消耗电流。如果电源在禁用时具有高阻抗输出,则可以省略二极管。

此方法还假定 I 的输出2C主站和总线上的所有其他器件在关断时均为高阻抗。这个假设可能不正确的一个原因是,如果 I2C 主站的电源已被移除,输出通过集成的 ESD 保护被箝位至现在的 0V 电源电压。通常不是这种情况,但如果是,则必须使用方法 2 或 3 来允许将 SDA 和 SCL 拉高。

方法 2 - 电平转换器

如果在系统接口关断时不能信任总线上的其他器件是高阻抗器件,则可以使用单个n沟道增强型MOSFET将每条总线线与系统的其余部分隔离开来。然后可以增加额外的上拉电阻,将MAX9877总线侧的逻辑电平设置为高电平。

图 2 显示了如何实现此方法。V迪奥又是系统的 I2C 上拉电压。所有四个电阻器都应根据 I2C 系统的时序要求。n沟道MOSFET用作双向电平转换器,允许MAX9877和基带的逻辑电平不同,而不会干扰正常工作。当 V迪奥电源被禁用,电平转换器允许MAX9877的SDA和SCL引脚保持高电平,从而最大限度地减小关断电流。

图2.增加n沟道MOSFET电平转换器可隔离系统的总线。

方法 3 — 高边电源开关

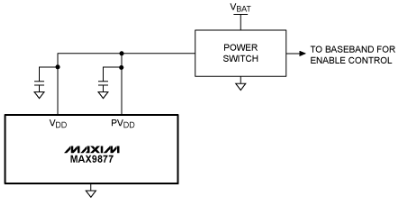

最小化MAX9877关断电流的最终方案是将高边开关与MAX9877电源串联。这允许电源在需要时与电池完全断开,并将MAX9877的关断电流降至1μA以下。

图3所示为如何将高边开关连接至MAX9877。MAX9877具有两个电源引脚(VDD和光伏DD),必须始终保持在0.3V以内。单个电源开关用于将电源保持在相同的电压,并最大限度地减少组件数量。

图3.与MAX9877电源串联的高边电源开关完全消除了所有关断电流。

审核编辑:郭婷

-

最小化启动期间的输出纹波2024-08-26 440

-

关于窗口最小化的实现2024-04-16 5771

-

MAX9877AERP+T - (Maxim Integrated) - 线性 - 放大器 - 音频2023-07-24 100

-

最小化热插拔控制器中的短路电流脉冲2023-03-17 1734

-

运算放大器应用中的噪声最小化2021-05-20 959

-

AN101-最小化线性调节器输出中的开关调节器残留2021-05-16 1152

-

如何使FPGA设计中的功耗最小化?2021-05-08 1352

-

基于应用毫微功耗运算放大器实现系统功耗最小化2019-07-18 1493

-

电流感应基础知识 以毫微功率预算实现系统功耗最小化2018-05-29 7414

-

LabVIEW最小化的使用2017-03-21 5845

-

MAX8906 电源管理,RTC和智能手机应用的音频子系统芯片2011-04-09 5014

-

磁通量最小化的概念2009-05-15 1222

-

MAX9877 pdf datasheet(单声道音频子系统2008-08-04 1424

全部0条评论

快来发表一下你的评论吧 !