I/O单元的结构说明 简单介绍几种数字I/O单元

描述

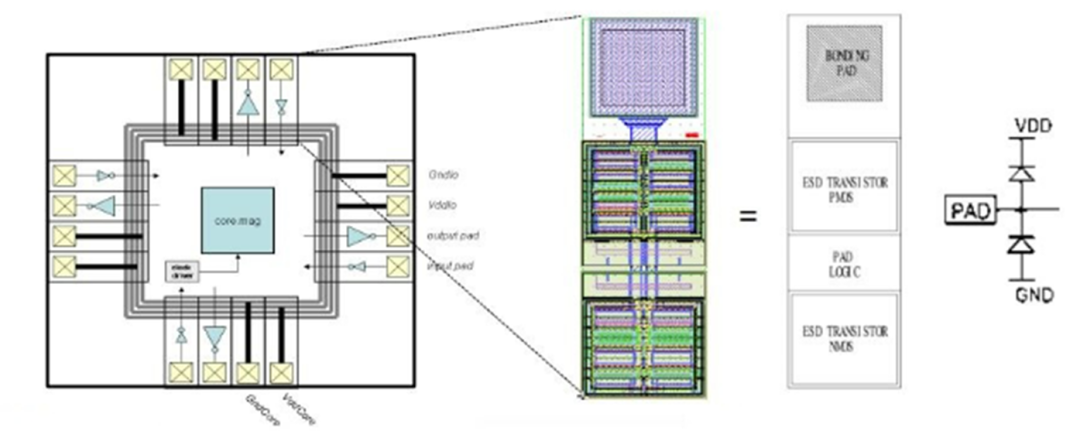

一、I/O 单元的结构:

• I/O PAD 包括压焊块,电路,电源线和地线。

• 压焊块 PAD 用于金线连接芯片与封装管座,通常为几十微米的矩形; 因此,为了防止金线短路, 要求 PAD 之间要有最小距离,具体数值取决于封装形式 。

• 大部分 I/O PAD 都是以标准单元的结构形式出现,有一套 I/O 库,和 std cell 一样,通常具有等高不等宽的形状。

(有的地方 PAD 是指单独的压焊块,有的地方 PAD 是指整个 I/O 单元; 需注意区分,一般用 Bounding PAD 指前者,PAD 指后者)

1.1 一套基本的 I/O 库提供以下几种 I/O PAD

1.给 pad 供电的 pad,例如:PAD_VDD,PAD_VSS;

2.给 core 供电的 pad,例如:VDD,VSS(如果存在多个 VDD domain,还有 AVDD,AVSS 之类的 pad);

3.模拟信号的 pad,例如 ANIN(analog 的 pad 一般就是一块铁片,有的 vendor 推荐用户可以自己基于要求自己再加上一定的 ESD 保护电路);

4.数字信号的 pad,一般有 input 和 output 的区别,里面还有包括 level shifter,buffers 之类的数字电路。

1.2 I/O 单元中的电路:

从功能上来讲 ,电路部分的作用有几方面:ESD 保护,level shifter,施密特触发器,还有提供电源环路等;

对外:提供驱动; 外界的电容相对来说很大,例如一个示波器的探头电容是 10Pf,仅仅靠芯片内部电路是无法驱动的;

对内:提供内外的隔离和输入保护功能; 最主要的就是 ESD 保护;

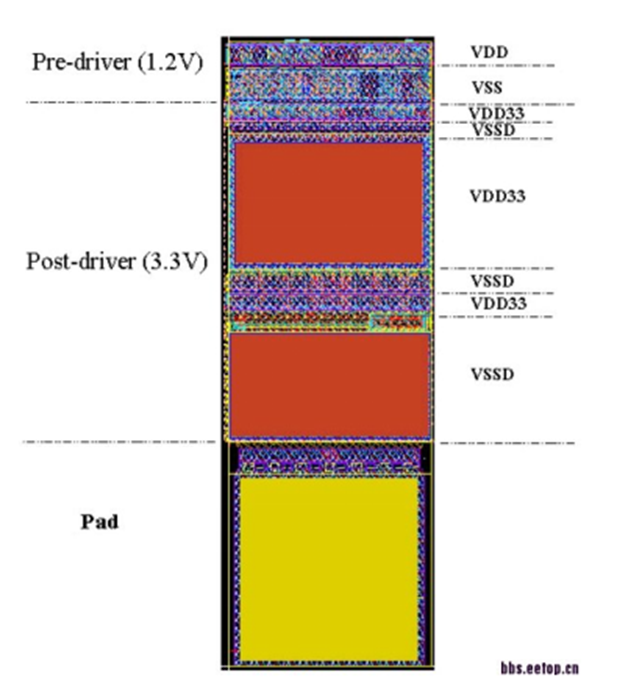

电路又可分为 pre-driver 和 post-drive:

pre-driver 就是 core 电压部分,一般为低压 1.0V,一般叫 VDD/VSS;

post-driver 为 pad 上高压部分,即 3.3V,提供大的驱动能力和 ESD 保护; tsmc 叫 VDDPST/VSSPST,SMIC 叫 VDDH/VSSD;

I/O 上都有两种高电压,通过 level shift 实现电压转换; 具体的电压值取决于工艺。

二、简单介绍几种数字 I/O 单元

• 输入 I/O PAD

• 输出 I/O PAD:倒相输出,倒相链输出

• 其他 I/O PAD:同相输出,三态输出 I/O PAD,开漏输出单元

• 输入输出I/O PAD

2.1 输入单元:承担对内部电路的保护

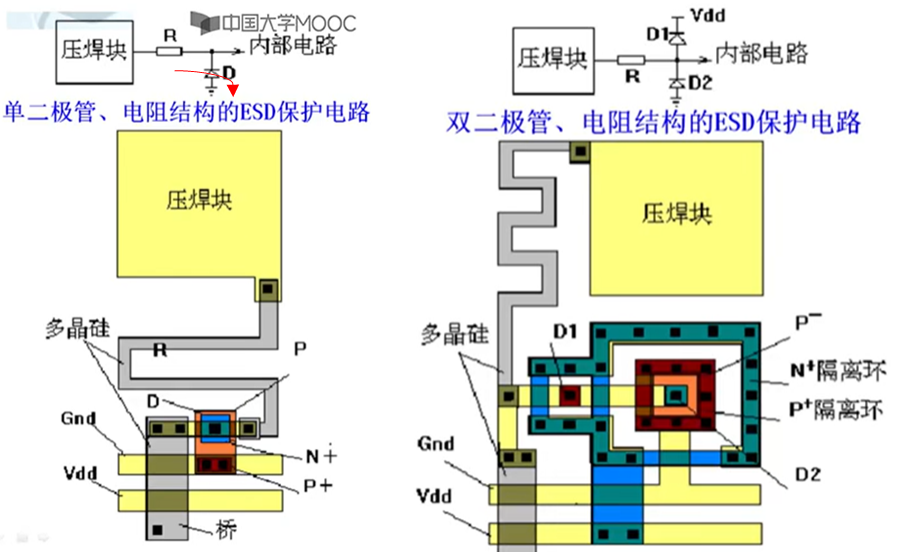

主要目的是 ESD 保护,ESD 保护的基本思想:

1.让静电通过一个低阻抗的并联通道进行放电,同时将 ESD 电压钳制在一个足够低的电平,从而避免金属互联线烧毁或者栅氧化层击穿;

2.输入保护分为单二极管、电阻结构和双二极管、电阻结构、还可以利用 PN 结的反向击穿特性; 3.正向偏置的二极管或者反向偏置的二极管都可以作为 ESD 防护器件;

2.1.2 单二极管+电阻结构的 ESD 保护电路:

瞬态高电压有可能是正的,也有可能是负的; PN结的阳极 P 区接地,阴极 N 区接内部电路;

如果此时一个来了一个负的高电压,通过 PN 结直接到地; 如果此时来了一个正的高电压,PN 结被反向击穿后形成泄放路径;

2.1.2 双二极管+电阻结构的 ESD 保护电路:

负的高电压通过 D2 泄放,正的高电压通过 D1 泄放。

隔离环用于防止 latch up; 关于latch up可以参考之前的一篇文章。

2.2 输出单元

输出单元的主要作用是提供一定的驱动能力; 此外,还承担一定的逻辑功能,单元具有一定的可操作性;

主要的输出单元包括:倒相输出、同相输出、三态输出、以及金属掩膜编程的输入输出单元(不同的控制信号下,既可以做输入也可以做输出单元);

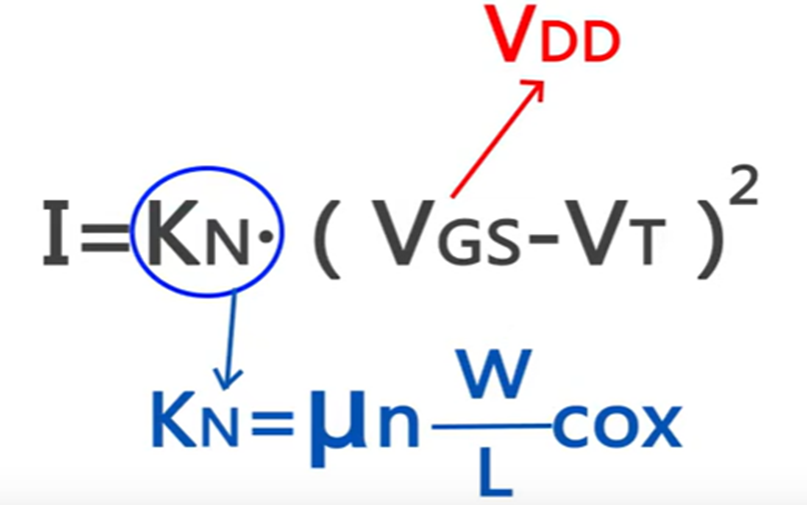

大驱动意味着对外部电路充电速度更快,也就需要大电流;MOS 管的电流方程如下图:

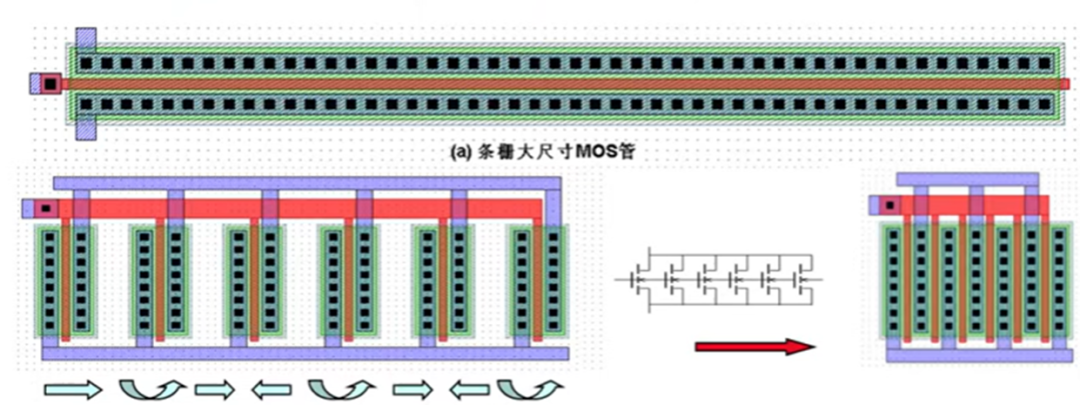

宽长比就是我们可以很方便操作的东西,大尺寸,也就是大的宽长比的 MOS 管可以提供一个大电流;

对于细长的条栅 MOS 管来说,不仅在栅下存在明显的寄生电容,同时较长的栅也会引入寄生电阻;将原来的 MOS 管拆分成多个并联的小的 MOS 管,并且使他们源漏共用,得到最终的版图;

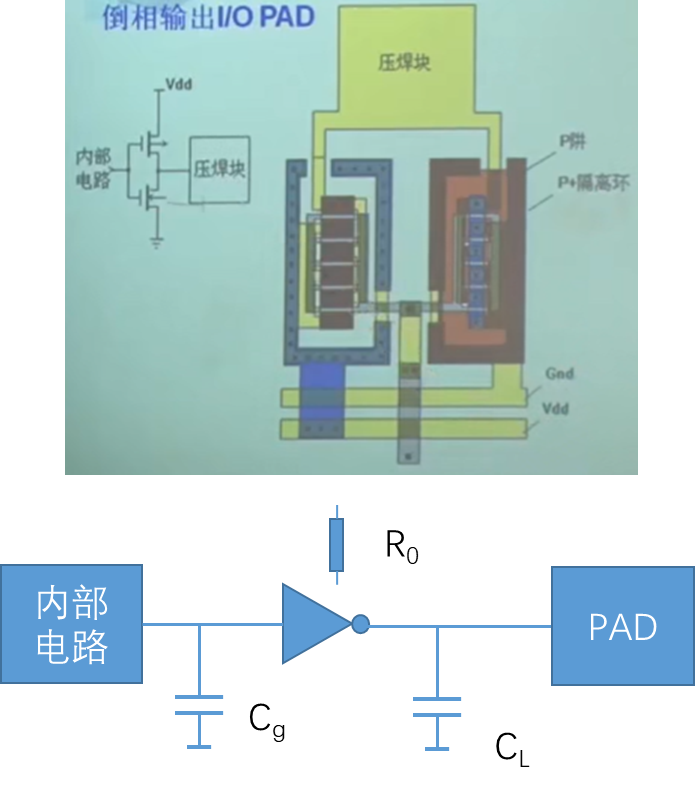

2.2.1 倒相输出的 I/O PAD

内部电路通过一级反相器驱动,连接到 PAD 上;

考虑输出单元的速度时,大尺寸电路的设计需要考虑前级驱动问题。

如果只用一级反相器带大电容负载,就需要大尺寸的反相器,那么其输入电容 Cg 很大,内部电路最后一级的负载电容就会很大;因此就算一级反相器可以驱动后面的电路,延迟也会非常大。

反相器内部电阻是 R0,外部负载电容是 CL;

R*C 称为 RC 时间常数;τ 为一个标准反相器的时间常数;令 Y=CL/C0

那么此时这个一级反相器的时间常数 ttol = R0CL = (CL/C0)R0C0 = Yτ

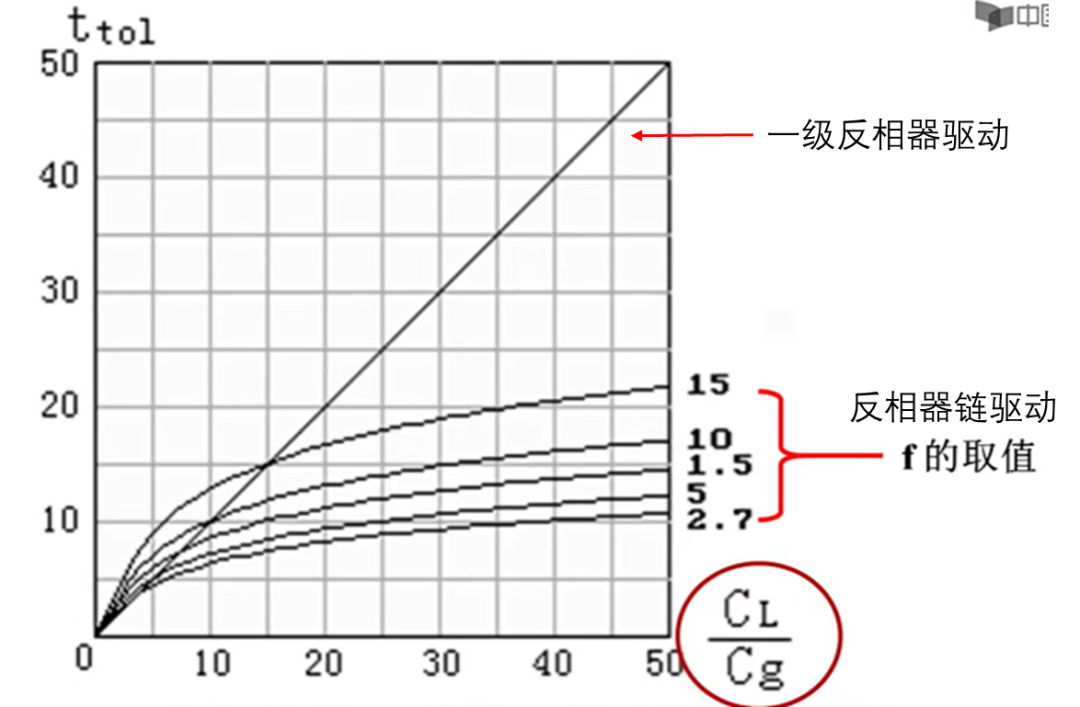

2.2.2 带大电容负载时的倒相器链驱动结构

采用 N 级倒相器链驱动,每一级都比上一级驱动能力大 f 倍:

对于倒相器链中的一级来说,下一级驱动能力大 f 倍,意味着输出电容为原来的 f 倍,电阻变为原来的 f/1;

因此,τ = R0*fCg = fτ

再看后面一级,τ = (R0/f)*(f2Cg) = fτ;

倒相器链中每一级的时间常数都是 fτ;

因此,总的倒相器链的时间常数为ttol = N*fτ (1)

由于每一级的驱动能力相比前一级放大了 N 倍,N 级就放大了 fN 倍,所以,fN = CL/Cg = Y (2)

由上述两式可得 ttol = (f/lnf)τlnY

从仿真结果可以看到,并不是任何情况下都适合采用倒相器链;并且采用倒相器链时,f 也不是越大越好;

2.3 其他 I/O PAD

2.3.1 同相输出 I/O PAD

“倒相+倒相”,或采用偶数级的倒相器链

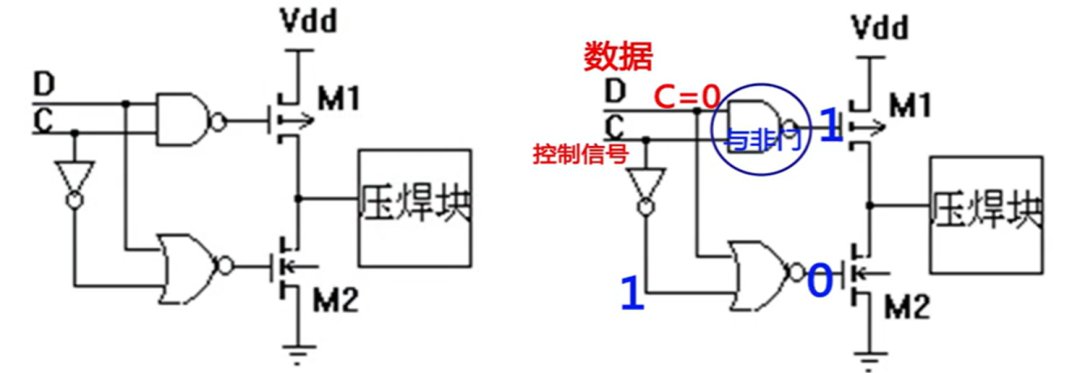

2.3.2 三态输出 I/O PAD

类似于三态门; 三态输出可用于总线上,一条总线上如果挂了 N 个门,不是每个门都可以去用这个总线的,当一个门用的时候其他门必须跟总线断开;

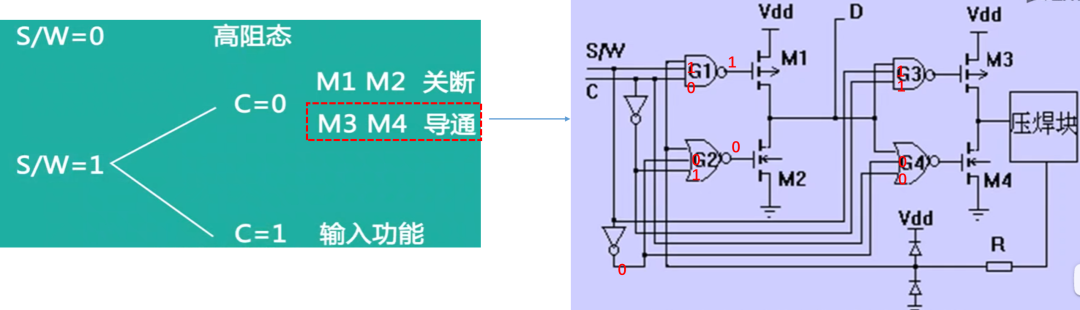

D 端是数据,C 端是控制信号;

当控制信号为 0 的时候,与非门的输出为 1;控制信号经过一个反相器,以及一个或非门后输出为 0;此时,对于 M1 这个 PMOS 和 M2 这个 NMOS 来说都不导通,因此 PAD 和内部电路完全不导通,呈现高阻态;

当控制信号 C=1 时,此时与非门、或非门作用都是一个反相器;

若 D=0,则 M1 不导通,M2 导通,此时输出 0

若 D=1,则 M1 导通,M2 不导通,此时输出 1

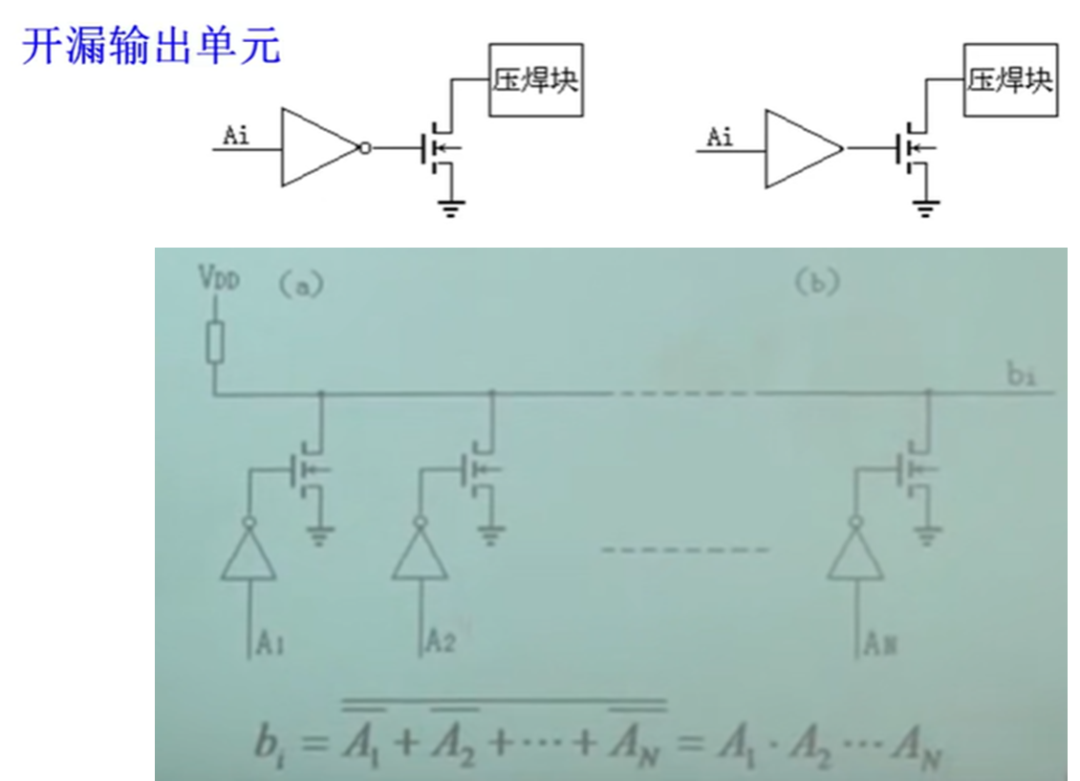

2.3.3 开漏输出单元

N 个开漏器件并联,接一个上拉网络,可以完成线与的功能;

也就是只有 A1-An 输出都为 1 的时候,该电路的输出才为 1;只要 A1-An 其中一个输出为 0,则电路输出为 0。

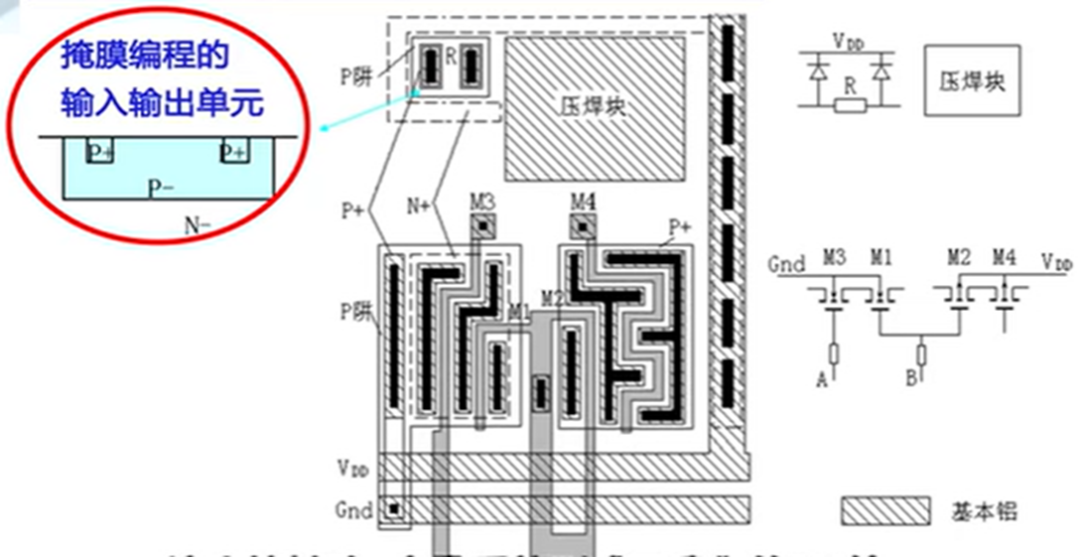

2.4 输入输出单元

可编程的输入输出单元

直接看这个单元的电路是不完整的,需要靠不同的连线使其变成输入或者输出单元;

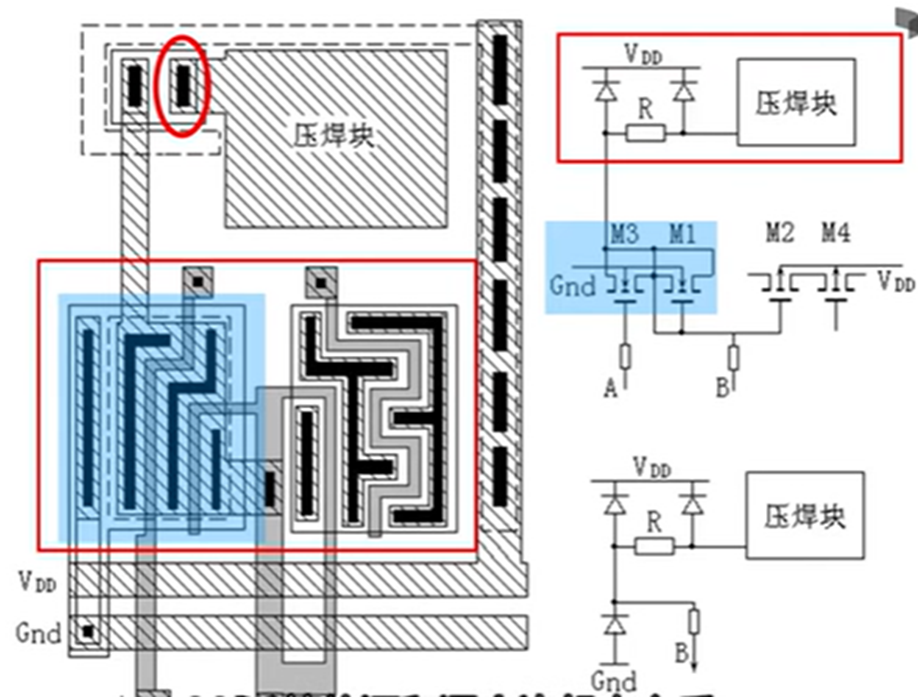

上方是属于输入电路的,二极管提供 ESD 保护,但是还并未和 PAD 连接; 下方是属于输出电路; 具体的功能取决于怎么连线;

• 二极管和 PAD 连接; M1 和 M3 的 SD 短接,相当于二极管; B 端 floating,M2 和 M4 不发挥任何作用,此时相当于一个输入单元;

• 作为输出单元时的电路图

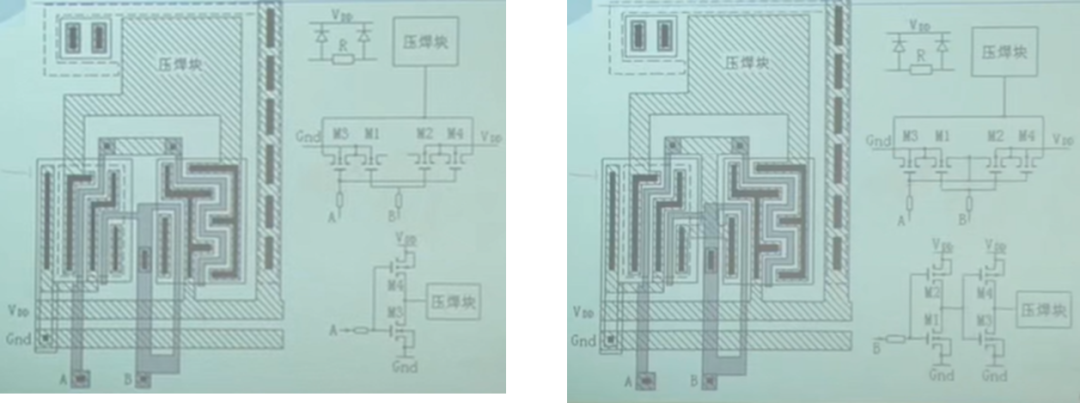

更常用的是输入输出单元是通过控制信号去切换具体的功能

S/W 和 C 作为控制端

个人觉得,框出来的地方应该写成:D=0 时,M3 截止,M4 导通,输出为 0;D=1 时,M3 导通,M4 截止,输出为 1;

三、关于I/O PAD一些其他基本概念

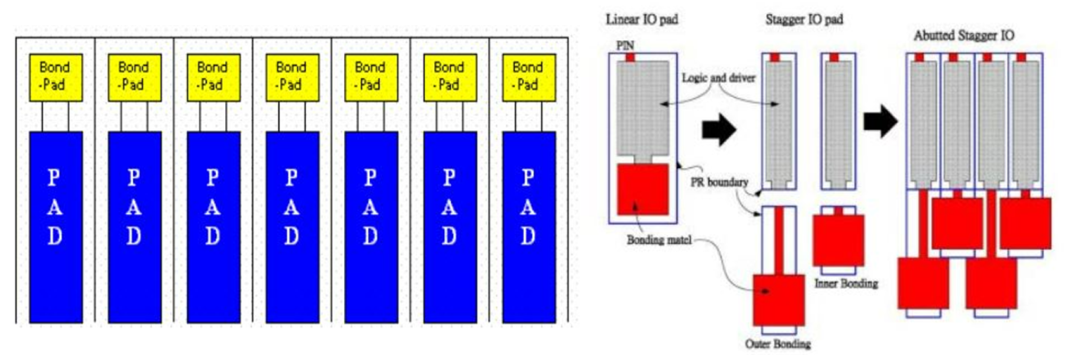

3.1 I/O PAD 的摆放方式(Inline/ Staggered):

对于面积有限,单层的 inline pad ring 放不下,可以使用 staggered 的方式,也就是下面右图里面那种交叉摆放的方式。

对于 Inline 的摆放方式,PAD 之间的最小 pitch 取决于不同的 foundary 和工艺。

对于 Staggered 的摆放方式,inner 和 outer bounding pad 相互交错,可以摆放更多的 PAD,代价是每一个 PAD 的平均高度增加了。

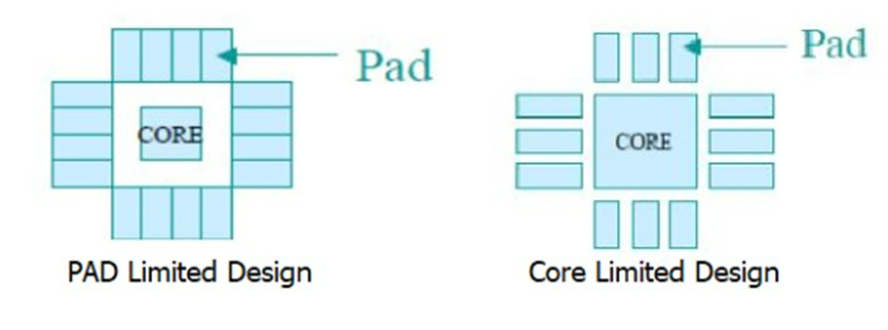

3.2 Pad Limited 和 Core Limited Design

区别在于是 PAD 还是 Core 区域限制了整个芯片的大小;

对于 Pad Limited Design,PAD 的尺寸更大,数量更多; 可以使用 Staggered 的排列方式或者 Flip Chip 的封装方式;

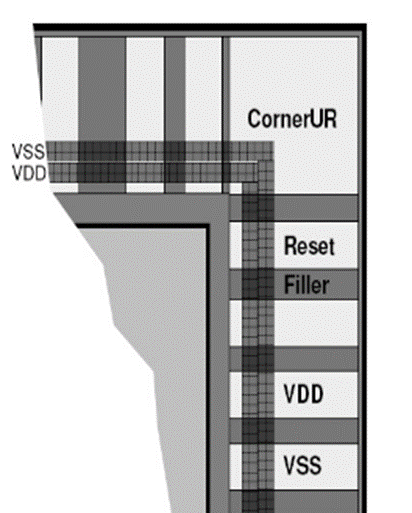

3.3 角垫和填充垫

• Corner PAD也是一种physical only cell,作用是连接芯片拐角处两边的 I/O PAD,连接衬底及衬底以上的各个层,使 I/O PAD内部的电路形成一个电源地的供电环路,同时也使得衬底连续;

• Filler PAD的作用和 Corner PAD类似,连接两个相邻的 I/O PAD的衬底以及金属层,形成一个电源地环路;

和 Corner PAD一样,Filler PAD也不是必须的,在打线和封装能够实现的情况下,可以将 I/O PAD不留空隙的相邻放置,当然要保证不会有DRC和LVS的违反。

3.4 I/O PAD 的选择

最后,关于 I/O PAD 的选择,Singal Pad 和 Power Pad 数量的计算。

-

数字I/O介绍2009-09-16 1311

-

I/O继电器内部结构原理图2010-03-02 2019

-

OP4520 FPGA处理器和I/O扩展单元助推您的项目2017-02-09 720

-

分布式智能I/O控制单元研究2018-03-02 987

-

介绍 I/O NI系统,C系列的I/O模块2018-06-14 5355

-

数字I/O模块的特点介绍2018-10-08 6316

-

Arduino Nano数字I/O板2022-07-18 829

-

NI数据采集技术之模拟I/O与数字I/O2023-08-21 773

-

XPHY I/O源同步接口应用说明2023-09-13 659

全部0条评论

快来发表一下你的评论吧 !