FMC DA子卡设计原理图资料:FMCJ465介绍

今日头条

1188人已加入

描述

| FMCJ465-2路 16bit 12.6GSPS FMC DA子卡 |

|

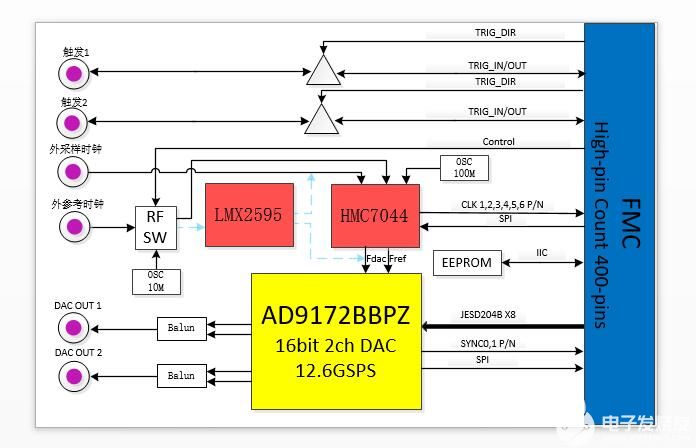

一、板卡概述: FMCJ465是一款转换速率最高为12.6GSPS 的 DAC 回放板,DAC位数16bit; 板卡基于ADI的AD9172系列DAC设计;板卡支持2路可配置的触发输出/触发输入;DAC的时钟支持内部参考时钟、外部参考时钟、外部采样时钟三种方式;并可提供一个接口同时支持外部采样和外部参考时钟的版本。 |

|

|

|

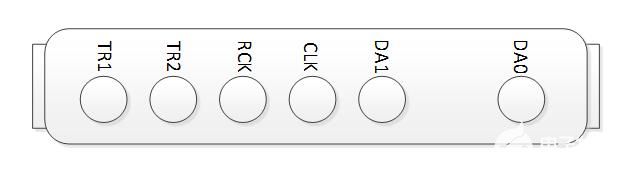

原理框图 二、主要规格: ● 6个SSMC的连接器,其中2个为模拟信号输出1(DA 0)和2(DA 1);一个为外部采样时钟输入(CLK);一个为外部参考时钟输入(RCK),2个为可由载板配置成输入或者输出的同步触发信号(TR1和TR2) ● 外部CLK也可同时兼容外采样和外参考时钟(需事先提出需求) ● 适应范围:完全符合Vita57.1规范,包括结构件,子卡尺寸,面板连接器,正反面器件的限高等,大大提供了子卡的通用性和适配性 ● 多种散热方式:风冷或导冷 ● AC耦合输入 ● 内外部时钟可灵活选择 ● HPC高引脚数连接器 ● 工作温度:商业级0℃~+70℃ ,工业级-40℃~+85℃ 三、板卡性能: 模拟输出 ● 输出耦合方式:交流耦合; ● 输出路数:2路; ● 输出频率:10MHz ~ 6000MHz; ● 满量程输出电流:16~26mA(RSET=5KΩ),可编程; ● 输出阻抗:50 Ohm; ● 连接器:SSMC; 数模转换器 DAC ● 单芯片方案; ● 分辨率:16bit; ● 最大更新率:12.6GS/s ● DAC输入兼容JESD204B子类1 时钟 ● 支持内参考或外部参考:10MHz,功率0~6dBm ● 支持外部采样时钟最高:12.6 GHz; 功率0~6dBm ● 输入阻抗:50 Ohm; ● 耦合方式:交流耦合; 触发 ● 外部触发输入:3.3V LVCMOS或LVTTL; ● 触发输出:3.3V LVCMOS或LVTTL; ● 最大频率:200MHz; ● 连接器:SSMC; FMC 接口 HPC: ASP-134488-01; ● DP_C2M(0-7),LVDS 1.0V ● LA(00-33),LVDS或者LVCMOS或者LVTTL ● CLK(GBTCLK0,1;CLK0),LVDS 1.8V或2.5V 功耗 ● +12V: <0.6 A; ● +3.3V: <0.1A; ● Vadj:<0.2A; 四、其他支持: ● 提供Verilog bit文件 ● JESD204B Core 五、前面板 |

|

六、应用(QT7227): ● 软件无线电 ● 宽带MIMO应用 ● 数字波束成形 ● (雷达/声纳)电子战 ● 物理实验 ● 信号智能检测 ● 航空航天和测试仪器 ● 北京太速科技 |

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

DA FMC子卡学习资料:基于JESD204B的4路1Gsps AD 4路1.25Gsps DA FMC子卡 精选资料分享2021-07-27 1154

-

FMC子卡设计方案保存:FMCJ450-基于ADRV9009的双收双发射频FMC子卡2022-07-27 17609

-

FMC子卡设计原理图:FMC210-1路1Gsps AD、1路2.5Gsps DA的FMC子卡2022-07-28 2878

-

FMC-1AD2DA FMC子卡概述及功能2022-07-11 3902

-

FMC210-1路1Gsps AD、1路2.5Gsps DA的FMC子卡2023-06-25 1668

-

FMC子卡设计原理图:FMCJ450-基于ADRV9009的双收双发射频FMC子卡2023-07-05 2060

-

全功能双CameraLink SDR接口 FMC子卡QT7421介绍2023-09-11 2373

-

FMC子卡设计原理图: FMC150-两路250Msps AD、两路600Msps DA FMC子卡2024-05-29 2057

-

9129板卡设计原理图:303-两路5.6Gsps 14bit DA FMC子卡2024-10-12 1742

-

FMC 子卡设计原理图:154-基于FMC 八路SFP+万兆光纤子卡2024-10-23 1368

-

FMC子卡设计原理图:FMC181-八路125Msps 14bit 直流耦合脉冲采集AD FMC子卡2024-12-09 1132

-

FMC子卡设计原理图:FMC209-基于FMC的4路125MAD输入、2路1GDA输出子卡 中低频信号采集2024-12-30 1141

-

FMC子卡设计方案:FMC210-1路1Gsps AD、1路2.5Gsps DA的FMC子卡2025-08-07 1180

-

FMC子卡模块设计方案:FMC160-两路14位400Msps AD,两路16位400Msps DA FMC子卡模块2025-10-21 509

-

中频信号采集卡 FMC子卡设计原理图:FMC145-四路16位125Msps AD FMC子卡模块2026-03-12 202

全部0条评论

快来发表一下你的评论吧 !