高速信号扩频时钟测试

测试测量实验

描述

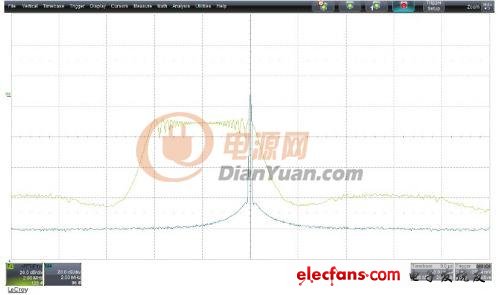

本文就将SSC的基本概念、SSC的测试测量方法做一介绍。 关键词: 力科 SSC 扩频时钟 EMI 眼图 一、SSC(扩频时钟)的概念 如下图1所示为一信号在是否具有SSC前后的频谱对比。图中蓝色曲线为没有SSC时候的频谱,浅色的为具有SSC时的频谱。从图中可见,未加SSC时,信号的能量非常集中,且幅度很大;而加了SSC后,信号能量被分散到一个频带范围以内,信号能量的整体幅度也有明显降低,这样信号的EMI辐射发射就将会得到非常有效的抑制。这就是通过使用SSC扩频时钟的方法抑制EMI辐射的基本原理。

使用SSC的方法能在多大程度上抑制EMI辐射和调制后信号能量在多宽频率范围内变化有关,频率变化范围越大,EMI抑制量越大。但这两者需要一个权衡,因为频率变化范围太大会使系统的时序设计带来困难。在Intel的Pentium4处理器中建议此频率变化范围要小于时钟频率的0.8%,如对于100MHZ的时钟,如果按照+/-8%来调制的话,频率的变化范围就是99.2MHZ-100.8MHZ。而对于100MHZ参考时钟的系统工作到100.8MHZ,可能会

图1 SSC扩频时钟的图示

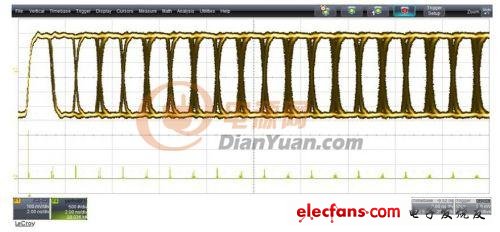

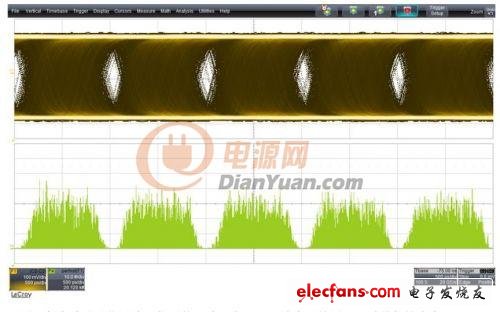

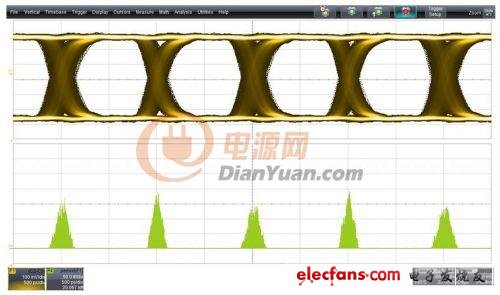

导致处理器超出额定工作频率,带来其它系统工作问题。因此在实际系统工作中一般都采用负向调制(downspeading)以保证时序上的最小周期要求,因此图1中的具有SSC的信号能量变化范围主要集中在信号载频的左侧。当前高速串行数据中比较常用的SSC频率为30KHZ、变调深度为0.5%。为了保证SSC处在规定的工作范围以内,对SSC的测试是非常重要的。 二、SSC(扩频时钟)对信号的影响 SSC会导致信号的频率产生波动。如果以信号的某一个边沿为参考基准,无限的累加波形数据,则应可以观察到因频率的变化而导致的波形边沿位置的变化。如下图2所示的上侧波形为一串行数据的模拟余辉显示,从余辉图中可见,信号边沿随着时间的变化呈现不同程度的变化。图2所示的下侧波形为对上侧模拟余辉波形做水平余辉直方图的结果(F4=Phistogram(F1)),通过直方图的方法将频率的变化反应到纵轴上,可以进一步更加明显的看出信号边沿的变化情况

图2 频率波动对信号边沿位置的影响(有SSC)

图3 频率波动对信号边沿位置的影响(无SSC)

图4频率波动对信号边沿位置的影响(有SSC)放大后的图示(时基起始点为-75ns)

图5频率波动对信号边沿位置的影响(无SSC)放大后的图示(时基起始点为-75ns) 从上图所示,带有SSC的余辉直方图逐渐呈现三角形的变化,而没有SSC时则理论上应趋于高斯分布。 三、SSC(扩频时钟)的测量 力科示波器中集成了两种常用的方法用于测量SSC。

一种是利用力科示波器中的抖动追踪(track)功能可以很方便的观察和分析信号中的SSC的频率、调制深度等参数,如下图6所示,F1为1Gbps的信号波形,F2为对F1波形频率的追踪,F3是对F2波形的滤波;另外一种是直接利用力科示波器中的SSCTrack函数分析功能,如下图6中的F5是直接用力科示波器中的函数SSCTrack功能进行SSC波形追踪的结果,此功能和对频率进行追踪的功能很类似,相当于将频率追踪、滤波的功能集成到一起,因此F5的运算对象是数据波形F1,且该功能还将信号的频率1GHZ作为一个基准,因而测量得到最大频率和最小频率分别为467.8KHZ和-4.5058MHZ(用第一种的Track功能测得的值为1.000039GHZ和995.351MHZ),调频宽度为4.9736MHZ(变调深度为0.49736%)。SSC扩频时钟的频率约为30.39KHZ。

图6 SSC扩频时钟的测试 F2和F3的参数设置:

图7 F2对F1的频率进行追踪设置

图8 F3对F2进行抽点和滤波设置(滤波之前先对波形进行抽点运算,可提高速度和更为平滑的进行滤波)

图9 F5对F1进行SSCTrack的设置

由于SSC波形的频率比较低,约为30KHZ(周期约为33.3us),因此对采集多大的数据量进行分析有一定的要求,如测试中一屏幕采集5个SSC波形周期的话,则总的采集时间长度约为200us,如果设置示波器采样率为20GS/S,那么则需要采集至少4M(200us/50ps)的数据量。 上述提到的Track功能是指某一参数(如本例中的频率)的变化范围表示在纵轴上,由于这一参数是随着时间的变化而变化的,因此通过Track图可以观察到参数随着时间的变化情况,具体可参见力科相关的介绍文档。如下图10所示对时钟周期的追踪示意图:

图10 时钟周期参数的追踪(Track)图 四、带有SSC(扩频时钟)的串行数据的眼图测量 SSC的使用会影响到串行数据眼图的测量效果,因此在进行信号眼图测量验证时需要选择合适的锁相环。如使用一阶的FC Golden PLL测量带有SSC的SATA眼图结果如图11左图所示,眼图触碰到了信号模板,这是由于一阶PLL不能跟踪SSC带来的频率变化。采用二阶PLL测量出的眼图结果如图11右图所示,这使得在有SSC时能测量出有意义的眼图结果。 有些芯片不能关闭SSC功能,那么这时候采用二阶PLL的方式仍然能判断出信号的质量。所以在有SSC时要注意串行数据眼图的PLL设置。

图11 带SSC的SATA信号带分别使用一阶和二阶PLL设置时的眼图测试

五、小结

本文简要介绍了SSC扩频时钟的基本概念以及如何使用力科示波器进行信号的扩频时钟的测试。由于当今电路系统中的信号速率越来越高,因此EMI问题也越来越普遍,因此在最新的一些高速串行数据规范中,如USB3.0、PCIE3.0等都特别强调了SSC的测试。力科示波器中的余辉直方图(Phistogram)和参数追踪(track)以及SSCTrack等函数功能可以很方便的帮助用户观察和分析信号的SSC。

-

如何实现高速时钟信号的差分布线2009-04-15 3706

-

时钟信号测试有回沟怎么办?测试点位置与芯片DIE分析2020-11-26 11540

-

SSC扩频时钟概述和主要参数2023-11-22 10343

-

扩频时钟技术分享:SSC技术是什么、SSC对测试高速总线信号的影响2025-01-06 9233

-

怎么设计基于FPGA的跳扩频信号发送系统?2019-08-23 1529

-

时钟信号回沟与测试点位置有关吗2020-11-25 2552

-

测试中遇到的25MHz时钟信号回沟问题汇总2017-09-19 24562

-

时钟扩频改善车载电子电磁兼容性能2017-11-09 950

-

高速信号与高频信号的区别2022-09-14 6129

-

AN4850_STM32扩频时钟生成原理、性能与实现2022-11-21 965

-

利用扩频时钟来降低EMI2023-02-14 570

-

高速信号集成电路测试方法2023-06-02 3770

-

一个25MHZ时钟信号的单调性问题测试分析2023-06-13 3899

-

高速信号眼图测试的基本原理2024-02-01 3028

-

高速信号测试知识分享2024-11-08 1943

全部0条评论

快来发表一下你的评论吧 !