时钟/数据/地址线上的串联电阻电路解析

电源/新能源

描述

我们在看原理图时,经常看到串一些小电阻,如22欧姆,但有时也不是一定要串。

同样的应用中,有的串电阻,有的不串。这是什么原因?如果是高速信号线上串小电阻,那就应该是终端阻抗匹配。

简单的例子:一个串口通讯的提示信号,当接上串口时,因为瞬间的插拔产生了一个很窄的电压脉冲,如果这个脉冲直接打到GPIO口,很可能打坏芯片,但是串了一个小电阻,很容易把能力给消耗掉。如果脉冲是5mA 5.1V,那么过了30ohm后就是5v左右了。

高速信号线中才考虑使用这样的电阻。在低频情况下,一般是直接连接。这个电阻一般有有两个作用,第一是阻抗匹配。

因为信号源的阻抗很低,跟信号线之间阻抗不匹配,串上一个电阻后,可改善匹配情况,以减少反射。第二是可以减少信号边沿的陡峭程度,从而减少高频噪声以及过冲等。因为串联电阻,和信号线的分布电容以及负载的输入电容会形成一个RC等效滤波电路,这样就会降低信号边沿的陡峭程度。

学过高速信号理论的都应该知道,如果高速传输信号的边沿很陡峭,其中就会含有大量的高频成分,将会造成辐射干扰,另外,也容易产生过冲。

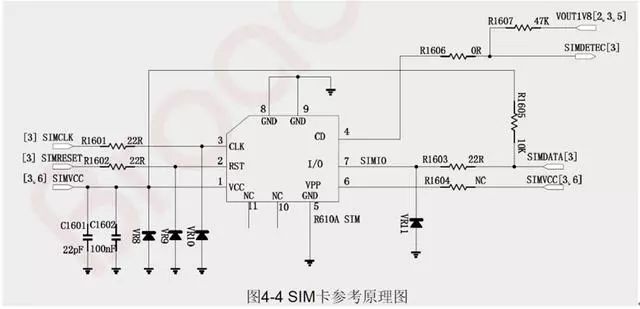

在SIM卡电路中,其实不加这个电阻也是不会影响SIM卡正常工作的。这个电阻主要是因为终端入网需要做SIM卡接口测试。SIM卡接口测试最容易出的问题就是CLK信号线上面过冲偏大。

增加小电阻可以消弱过冲。其实不一定要33R,换成47R,100R也都OK的。SIM卡的CLK频率不会太高,一般不用串电阻来防止对外辐射影响其他信号,所以SIM卡CLK信号在LAYOUT时也没有要求四面包地处理。

另外串联小电阻可以增强ESD防护作用,TVS一般是利用瞬间导通释放静电来防护的,在TVS后面加小电阻可以起到“堵”的作用,当静电够猛的时候,有时候TVS还不能起到防护作用,而串联的小电阻像是一面墙,将静电堵住。

敏感信号线上面采用TVS加串联小电阻的方式做ESD防护效果还不错,深受各工程师喜爱。

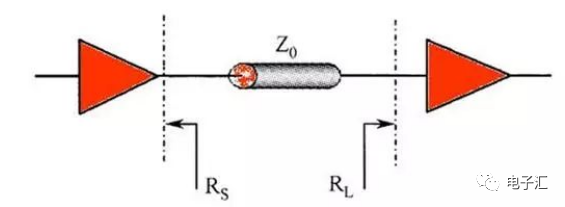

信号源内阻与所接传输线的特性阻抗大小相等且相位相同,或传输线的特性阻抗与所接负载阻抗的大小相等且相位相同,分别称为传输线的输入端或输出端处于阻抗匹配状态,简称为阻抗匹配。

否则,便称为阻抗失配。阻抗匹配impedance matching)是指信号源或者传输线跟负载之间的一种合适的搭配方式,主要用于传输线上,以此来达到所有高频信号无损耗传递至负载的目的。

先从直流电压源驱动一个负载入手。任何实际的电压源,都是有等效内阻的,所以我们可以把一个实际电压源,等效成一个理想的电压源跟一个电阻r串联的模型。

假设负载电阻为R,电源电动势为U,内阻为r,那么我们可以计算出流经电阻R的电流为:I=U/(R+r),可以看出,负载电阻R越小,则输出电流越大。

负载R上的电压为:Uo=IR=U/[1+(r/R)]。

可以看出,负载电阻R越大,则输出电压Uo越高。最后再来计算一下电阻R消耗的功率为:

P = I2×R=[U/(R+r)]2×R = U2×R/(R2+2×R×r+r2)

= U2×R/[(R-r)2+4×R×r]

= U2/{[(R-r)2/R]+4×r}

对于一个给定的信号源,其内阻r是固定的,而负载电阻R则是可选择的。

我们可以看到式中[(R-r)2/R],当R=r时,[(R-r)2/R]可取得最小值0,这时负载电阻R上可获得最大的输出功率Pmax=U2/(4×r)。

即,当负载电阻跟信号源内阻相等时,负载可获得最大的输出功率,这就是我们常说的阻抗匹配。

当交流电路中含有容性或感性阻抗时,结论有所改变,就是需要信号源与负载阻抗的的实部相等,虚部互为相反数,这叫做共扼匹配。

在低频电路中,我们一般不考虑传输线的匹配问题,只考虑信号源跟负载之间的情况,因为低频信号的波长相对于传输线来说很长,传输线可以看成是“短线”,反射可以不考虑(可以这么理解:因为线短,即使反射回来,跟原信号还是一样的)。

从以上分析我们可以得出结论:如果我们需要输出电流大,则选择小的负载R;如果我们需要输出电压大,则选择大的负载R;如果我们需要输出功率最大,则选择跟信号源内阻匹配的电阻R。

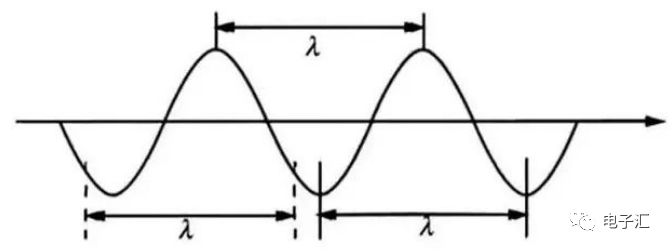

在高频电路中,我们还需要考虑反射的问题。当信号的频率很高时,则信号的波长就很短,当波长短得跟传输线长度可以比拟时,反射信号就会叠加在原信号上,从而会改变原信号的形状。

如果传输线的特征阻抗跟负载阻抗不相等(即不匹配)时,那么在负载端就会产生反射。为什么阻抗不匹配时会产生反射以及特征阻抗的求解方法,牵涉到二阶偏微分方程的求解,在这里我们不细说了,有兴趣的可参考电磁场与电磁波方面书籍中的传输线理论。

在这里需要强调一点的是,特性阻抗跟我们通常理解的电阻不是一个概念,它与传输线的长度无关,也不能通过使用欧姆表来测量。

为了不产生反射,负载阻抗跟传输线的特征阻抗应该相等,这就是传输线的阻抗匹配。如果阻抗不匹配会有什么不良后果呢?

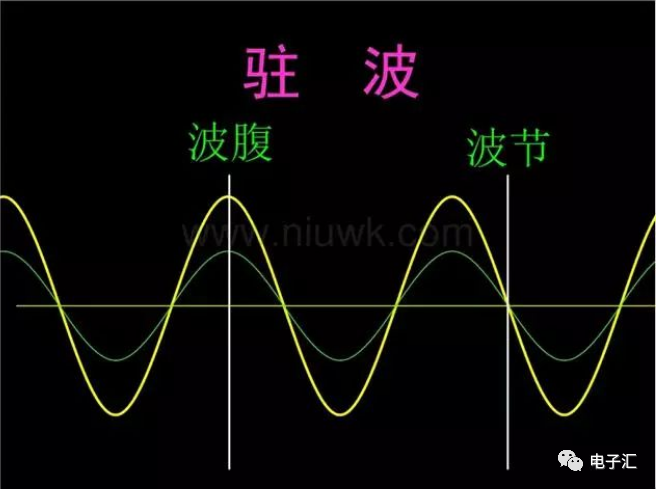

如果不匹配,则会形成反射,造成能量不能完全传递过去,导致功耗增加、效率降低;会在传输线上形成驻波(频率相同、传输方向相反的两种波。

简单点说,就是有些地方信号强,有些地方信号弱),从而导致传输线的有效功率容量降低;功率发射不出去,甚至会损坏发射设备。

如果是电路板上的高速信号线与负载阻抗不匹配时,会产生震荡,辐射干扰,EMC等等。

当阻抗不匹配时,有哪些办法让它匹配呢?第一,我们可以考虑使用串联/并联电容或电感的办法,这也是在射频调试时常用手段。第二,可以考虑使用串联/并联电阻的办法。

一些驱动器的阻抗比较低,可以串联一个合适的电阻来跟传输线匹配,例如高速信号线,有时会串联一个几十欧姆到二三十欧姆的电阻。而一些接收器的输入阻抗则比较高,可以使用并联电阻的方法,来跟传输线匹配。

例如,485总线接收器,常在数据线终端并联120欧的匹配电阻。

为了帮助大家理解阻抗不匹配时的反射问题,举两个例子:假设你在练习拳击—打沙包。如果是一个重量合适的、硬度合适的沙包,你打上去会感觉很舒服。但是,如果哪一天我把沙包做了手脚,例如,里面换成了铁沙,你还是用以前的力打上去,你的手可能就会受不了了。

这就是负载过重的情况,会产生很大的反弹力。相反,如果我把里面换成了很轻很轻的东西,你一出拳,则可能会扑空,手也可能会受不了——这就是负载过轻的情况。

浅谈四层板和22欧电阻

选用四层板不仅是电源和地的问题,高速数字电路对走线的阻抗有要求,二层板不好控制阻抗,22欧电阻一般加在驱动器端,也是起阻抗匹配作用的。布线时要优先布数据、地址线,和需要保证的高速线。

在高频的时候,PCB板上的走线都要看成传输线,传输线是有其特征阻抗的,学过传输线理论的都应该知道,当传输线上某处出现阻抗突变(不匹配)时,信号通过就会发生反射,反射对原信号造成干扰,严重时就会影响电路的正常工作。

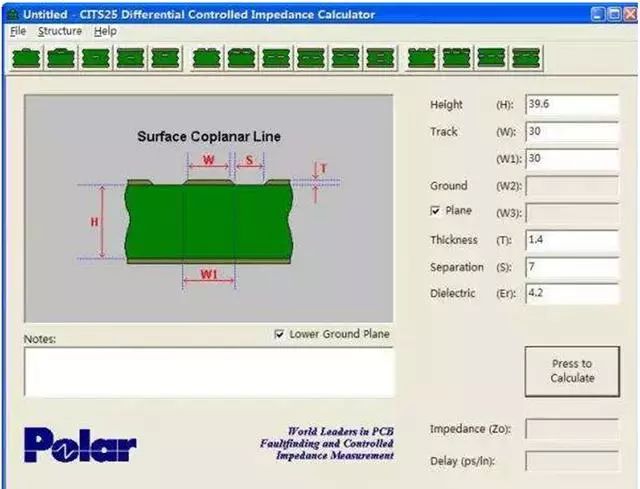

采用四层板时,通常外层走信号线,中间两层分别为电源和地平面,这样一方面隔离了两个信号层,更重要的是外层的走线与它们所靠近的平面形成称为“微带”(microstrip) 的传输线,它的阻抗比较固定,而且可以计算,而对于两层板就比较难以做到这样效果。

传输线阻抗主要与走线的宽度、阻抗线到参考平面的距离、敷铜的厚度以及介电材料的特性有关,有许多现成的公式和工具可供计算。

22欧电阻通常串连放在驱动的一端(其实不一定22欧,从几欧到五、六十欧都有,视具体电路而定) ,其作用是与发送器的输出阻抗串连后与走线的阻抗匹配,使反射回来(假设解收端阻抗没有匹配) 的信号不会再次反射回去(吸收掉),这样接收端的信号就不会受到影响接收端也可以作匹配。

这里所说的高频,不一定是时钟频率很高的电路,是不是高频不止看频率,更重要是看信号的上升下降时间通常可以用上升(或下降) 时间估计电路的频率。

一般取上升时间倒数的一半,比如如果上升时间是1ns,那么它的倒数是1000MHz,也就是说在设计电路是要按500MHz的频带来考虑有时候要故意减慢边缘时间,许多高速IC其驱动器的输出斜率都是可调的。

编辑:黄飞

-

地址线/时钟线/数据线上串联的小电阻,到底有什么作用?2024-06-06 3714

-

串联电路和并联电路的区别 串联电路中电流电压电阻的关系2024-02-01 12011

-

电阻串联电路的特点是什么2021-05-01 40641

-

关于时钟线/数据线/地址线上串联电阻及其作用资料下载2021-04-13 1384

-

关于时钟线数据线地址线上串联电阻及其作用介绍2019-06-03 2186

-

时钟线数据线地址线上串联的小电阻有什么作用?2019-05-31 1809

-

关于时钟线数据线地址线上串联电阻其作用的资料整理2019-05-30 2463

-

时钟线数据线地址线为什么串联电阻2019-05-29 2156

-

高速电路数据线上串联电阻作用详解2018-10-12 5462

-

串联谐振电路的应用详情解析2017-11-23 39053

-

高速信号线中时钟线/数据线/地址线上串联电阻等资料整理2015-01-21 4522

-

时钟线/数据线/地址线上串联电阻的作用2011-11-02 8390

-

什么是电阻的串联电路?2008-10-04 4363

全部0条评论

快来发表一下你的评论吧 !