带相机芯片的串行器的应用

描述

Maxim串行器可以连接和控制相机IC。本文介绍如何将相机的原始 RGB 或 YUV 输出转换为适合与标准显示器一起使用的 RGB 数据。

介绍

Maxim串行器可以连接和控制相机IC。这些器件包括MAX9257,具有半双工UART/I²C控制通道,以及MAX9259和MAX9263,均具有全双工同步控制通道。MAX9263还支持高带宽数字内容保护(HDCP)。本应用笔记介绍了如何将相机的原始RGB或YUV输出转换为适合与标准显示器配合使用的RGB数据。

相机输出格式

相机芯片,如豪威OV10630,可以通过串行器连接。OV10630的接口引脚包括像素时钟、PCLK、线路有效、HREF、帧同步、VSYNC和并行数据位D[9:0]。数据位稳定在时钟的上升沿。

YUV 和原始 RGB 格式的说明

CMOS相机传感器由数百万个光敏单元组成。每个细胞本身对所有波长的光做出反应。光学滤光片涂层用于使特定传感器仅对红色、绿色或蓝色波长的光做出反应。相邻的细胞通常涂有拜耳排列的颜色,其中两倍的细胞涂有绿色,而不是红色或蓝色。这模仿了人眼的生理学。从左到右和从上到下获取传感器单元输出,原始 RGB 数据按蓝色、绿色...蓝色,绿色(第一行末尾),绿色,红色,...绿色、红色(第二行末尾)等,如图 1 所示。

图1.原始 RGB 数据字节序列。

通过插值相邻像元的所需颜色,可以生成与传感器像元密度相同的 RGB 数据。或者,这可以通过使用相邻单元格的颜色来实现,符合某些规则。为每个像素位置形成 RGB 集的一个这样的规则是在同一行上使用一对相邻的单元格,以及绿色旁边的下一行(或上一行)中的单元格。插值的RGB数据被排序为...,红色(i-1),绿色(i-1),蓝色(i-1),红色(i),绿色(i),蓝色(i),红色(i+1),绿色(i+1),蓝色(i+1),...如图2所示。每个像素都需要一组RGB数据来驱动彩色显示器,同时保持相机传感器的最大可能分辨率。这种插值RGB数据的亮度分辨率接近传感器单元的亮度分辨率,而色度分辨率较差。感知分辨率可以与传感器单元一样高,因为人眼对每个像素的强度比对像素的颜色分量更敏感。

图2.RGB 数据字节序列。

但是,这种插值RGB数据的数据速率是其三倍。为了降低数据速率,特别是传输速率,可以使用YUV色彩空间(将模拟彩色电视信号放入模拟黑白电视的频段中)。在下面的等式中,亮度用Y表示,蓝色和亮度之间的色差为U,红色和亮度之间的色差为V,

其中典型的颜色权重值为 WR= 0.299, WB= 0.114,WG= 1 - WR- WB= 0.587,归一化值为 U.MAX和 V.MAX= 0.615。

对于带有拜耳图案颜色滤光片的相机传感器,相邻像素的U或V数据大致相同,具体取决于线索引i和像素索引j(如果使用相邻颜色的规则)。使用此准则,可以根据以下表达式直接从原始 RGB 数据生成 YUV 数据。

对于偶数线索引 i 和偶数像素索引 j。

对于偶数线索引 i 和奇数像素索引 j。

对于奇数线索引 i 和偶数像素索引 j。

对于奇数线索引 i 和奇数像素索引 j。

对于偶数线索引 i 和偶数像素索引 j。

对于偶数线索引 i 和奇数像素索引 j。

对于奇数线索引 i 和偶数像素索引 j。

对于奇数线索引 i 和奇数像素索引 j。

对于偶数线索引 i 和偶数像素索引 j。

对于偶数线索引 i 和奇数像素索引 j。

对于奇数线索引 i 和偶数像素索引 j。

对于奇数线索引 i 和奇数像素索引 j。

为了降低数据速率,使用偶数像素索引 U 数据和奇数像素索引 V 数据,以及偶数和奇数像素索引 Y 数据。这种数据速率降低的YUV数据按如图3所示的顺序传输。换句话说,Y1/ 60和 V1是像素 1 的数据;Y2/ 62和 V1是像素 2 等的数据。

图3.YUV422 数据字节序列。

422 表示 Y:U:V 的采样比。采用4:x:x标准是因为最早的颜色NTSC标准,该标准使用4:1:1的色度子采样,因此图像的彩色分辨率仅为亮度的四分之一。如今,只有处理未压缩信号的高端设备才使用4:4:4的色度子采样,亮度和颜色信息具有相同的分辨率。

序列化程序输入格式

Maxim串行器的并行接口设计用于24位RGB数据。具体而言,MAX9259具有像素时钟位(PCLK)和29个数据位,可用于24 RGB位以及水平同步、垂直同步和3个控制位。除数据并行接口外,DRS和BWS引脚需要分别设置为高或低,以便选择数据速率和总线宽度。

美信串行器/解串器

MAX9257和MAX9258串行器/解串器(SerDes)对具有多达18个并行输入/输出位,适合发送YUV数据,而MAX9259/MAX9260芯片组具有28个并行输入/输出位,适用于传输RGB数据。另一对SerDes,MAX9263/MAX9264,具有28位,具有额外的HDCP功能。此外,MAX9265和MAX9268是一对28位SerDes,具有摄像头链路,而不是并行输入/输出接口。所有28位Maxim串行器和解串器具有相同的并行-串行数据映射,可互换使用。例如,MAX9259串行器可与MAX9268解串器配合使用,以发送RGB数据(借助FPGA)。该数据通过串行链路从CMOS相机发送到相机链接接口的显示设备。

序列化程序的映射

为了匹配MAX9268解串器的相机链路输出接口,应根据以下信号图映射并行RGB位。图4所示为MAX9268中间并行位与其相机链路输出之间的映射。图 5 显示了相机链路的 RGB 内容位映射。表1给出了MAX9259串行器的相应内容映射。

图4.MAX9268内部并行至输出映射。

图5.相机链接内容映射。

| DIN0 | DIN1 | DIN2 | DIN3 | DIN4 | DIN5 | DIN6 | DIN7 | DIN8 | DIN9 |

| R0 | R1 | R2 | R3 | R4 | R5 | G0 | G1 | G2 | G3 |

| DIN10 | DIN11 | DIN12 | DIN13 | DIN14 | DIN15 | DIN16 | DIN17 | DIN18 | DIN19 |

| G4 | G5 | B0 | B1 | B2 | B3 | B4 | B5 | HREF | VSYNC |

| DIN20 | DIN21 | DIN22 | DIN23 | DIN24 | DIN25 | DIN26 | DIN27 | DIN28 | |

| R6 | R7 | G6 | G7 | B6 | B7 |

颜色转换:YUV 到 RGB

FPGA芯片可以将来自相机的数据速率降低的YUV数据转换为MAX9259串行器的RGB数据。当在 8 位定点数学运算中实现时,这种颜色空间转换的公式可以用以下表达式来描述。n 是 D 的偶数n和 En在 2德·和 3RD方程。

Cn = Yn - 16

Dn = Dn + 1 = Un - 128

En = En + 1 = Vn + 1 - 128

Rn = clip((298 × Cn + 409 × En + 128) >> 8)

Gn = clip((298 × Cn - 100 × Dn - 208 × En + 128) >> 8)

Bn = clip((298 × Cn × 516 × Dn + 128) >> 8)

其中>> 8 表示“将位向右移动八次”,剪辑表示“仅获取最后 8 位”。

FPGA 解决方案

输入缓冲

输入缓冲电路由一个计数器、三个寄存器和一些组合逻辑组成,用于以输入时钟速率的一半将单字节时钟输入转换为三字节时钟输出。组合逻辑用于分别为每个 Y、U 和 V 字节启用相应的寄存器。

图6.输入缓冲电路。

时钟开关

FPGA输出像素时钟是相机像素时钟速率的一半,驱动串行器像素时钟输入。但是,相机在初始化之前不会输出像素时钟。解决方案是在FPGA内部实现2:1时钟多路复用器(mux)和时钟信号检波器。多路复用器由时钟信号检测器控制。多路复用器的上电默认时钟输入来自相机的时钟振荡器,这使得SerDes芯片组提供控制通道来初始化相机。时钟信号检波器对垂直同步信号脉冲进行计数。经过几次垂直同步脉冲后,多路复用器切换到相机像素时钟的半速率。使用像OV10630这样的高清摄像头传感器,一个垂直同步脉冲的每个周期包含超过100k像素的时钟。几个垂直同步脉冲的时间足以稳定相机的内部锁相环(PLL)。计数垂直同步比计算像素时钟效率高得多,并为实现节省了FPGA逻辑元件。

中间缓冲

转换表达式不描述硬件电路实现的延迟。要从 YUV 输入生成 RGB 数据,需要两到三次乘法和三到四次加法。虽然FPGA逻辑元件(门)只产生几纳秒的延迟,但载波、加法器和乘法器移位输入的传播会导致广泛的延迟和延迟扩展。为了最小化延迟,每个常数乘法器由两个移位输入的加法器近似,代表常数的 2 个非零最高有效位 (MSB)。在大约100MHz的输入YUV字节速率下,延迟扩展可能会跨越相邻像素的时序边界,从而导致视频噪声。在每个乘法器之后放置中间寄存器以消除延迟扩展。

前面提到的YUV到RGB色彩空间转换已经在Actel® ProASIC3 A3PN125Z FPGA器件中实现。图 7 显示了该 FPGA 实现方案的示意图。

| 更详细的图像。(PDF, 172kB) | 更详细的图像。(PDF, 180kB) |

图7.YUV 至 RGB 转换器的 FPGA 实现。

应用电路

相机芯片可以由其供应商在子PCB上提供。图8显示了相机子模块的功能框图。输入为电源、PWR 和晶体时钟 (XCLK)。输出信号为并行数据位(D0.D9)、I²C总线(SDA、SCL)、视频同步(HREF、VSYNC)和像素时钟(PCLK)。

图8.摄像头模块功能框图。

图9显示了FPGA和串行器芯片的原理图,以完成应用电路。该电路通过由两对双绞线组成的串行电缆供电,一对用于串行信号,另一根用于电源。串行器和FPGA器件使用单独的LDO电源IC。旁路电容器用于摄像头模块,该模块具有自己的LDO电源芯片,以进一步减少潜在的干扰。阻尼电阻用于FPGA和串行器器件之间的数据链路。

更详细的图像 (PDF, 1.6MB)

图 9a. 应用电路的 FPGA 部分。

更详细的图像 (PDF, 1.6MB)

图 9b.应用电路的串行器部分。

MAX9259还能够直接连接到摄像头传感器,如OV10630,以构建更小的摄像头。色彩空间转换FPGA可以在解串器之后使用。由于该应用需要摄像头链路输出,可由MAX9268直接驱动,因此色彩空间转换FPGA位于摄像头传感器和串行器(MAX9259)之间。

视频捕获示例

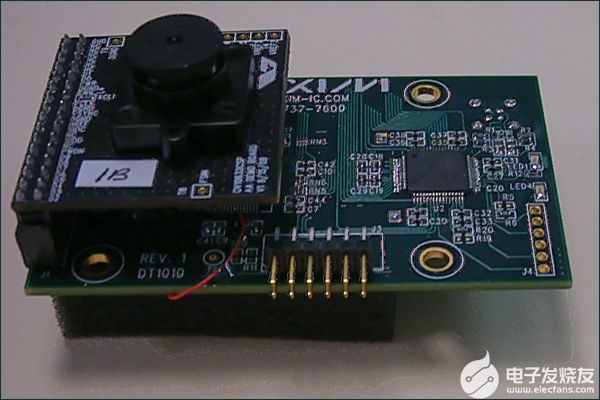

图10显示了相机应用电路的实现方式,也是使用这些相机应用电路捕获的。

图 10.相机应用电路的实现。

总结和未来方向

本应用笔记介绍了将Maxim相机串行器IC与FPGA结合使用的典型方法。应用原理图和FPGA代码可作为原样设计参考。RAW RGB至24位RGB FPGA转换器的实现将在本应用笔记的未来更新中提供。

审核编辑:郭婷

-

求串行总线舵机芯片设计,价钱面议。微信***2017-02-14 2366

-

求串行总线舵机芯片仿制2017-02-17 3250

-

带传感器的无刷电机BLDC低功耗单片机芯片EN8P2712—深圳单片机开发方案公司英锐恩2018-12-04 2104

-

请问哪一个小封装的单片机芯片带ADC,DAC,UART?2023-06-25 993

-

单片机芯片生产工艺对单片机芯片良率的影响2020-07-05 3376

-

单片机芯片的基本组成_单片机芯片的选择2020-08-27 6881

-

什么是手机芯片 2021年手机芯片性能排行榜网2021-12-08 14460

-

手机芯片的作用2021-12-20 16966

-

手机芯片的主要作用是什么2022-02-05 32191

-

收音机芯片资料2022-02-10 3030

-

带linkit ONE的Grove串行相机2022-12-26 485

-

工业相机芯片选型浅析2023-02-24 3845

-

带Spresense的AI相机2023-06-09 650

-

工业相机芯片开窗的不同模式对比2023-11-13 5711

-

0.01 – 4.0 GHz 7 位数字衰减器,带串行和并行驱动器 skyworksinc2025-05-26 97

全部0条评论

快来发表一下你的评论吧 !