信号发生器电路(Quartus/Verilog/CRD500)

描述

因近期芯片价格太高,配套CRD500开发板售完后暂未生产,现阶段无法购买该开发板。后续根据芯片供货情况再安排开发板生产。需选购开发板的朋友请关注该公众号及米恩工作室的淘宝官网。

1 运行平台 硬件:CRD500数字信号处理板 系统:win7/64(推荐);win7/32;win10/64 软件:Quartus13.1/ModelSimSE 10.1c/Verilog HDL/Matlab2014a

2 主要功能及性能指标

2.1 主要功能

1)可产生ASK、FSK、PSK、单频信号、三角波、锯齿波、方波 2)载波频率、调制参数等波形参数可设置 3)可通过串口设置信号参数

2.2 主要性能指标

1)系统时钟:50MHz

2)串口协议:9600bps波特率、1位起始位、8位数据位、1位停止位、无校验位

3)载波频率范围:1MHz~4.75MHz可变,步进250kHz

4) 基带信号码速率范围:100kHz~475kHz,步进25kHz

5)三角波频率范围: 6kHz~98kHz,共16种频率可设置

6) 锯齿波频率范围: 12kHz~195kHz,共16种频率可设置

7)方波频率范围:50kHz~237.5kHz,步进12.5kHz

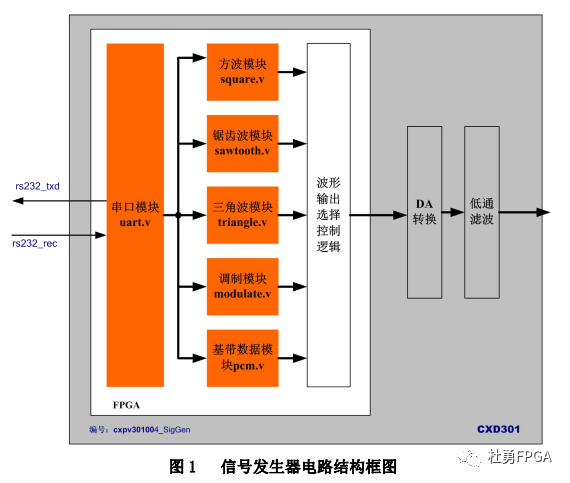

3 程序结构框图说明

信号发生器电路程序主要串口通信模块(uart.v)、方波模块(square.v)、锯齿波模块(sawtooth.v)、三角波模块(triangle.v)、基带数据模块(pcm.v)和调制模块(modulate.v)组成。

uart.v模块完成与计算机之间的串口通信,接收串口发出的指令,并将接收到的指令回送至计算机,验证指令传输的正确性。串口接收的指令送至各信号波形产生模块,产生相应参数的信号波形。

方波模块(square.v)、锯齿波模块(sawtooth.v)、三角波模块(triangle.v)分别根据指令参数产生方波、锯齿波和三角波信号。基带数据模块产生8比特循环的基带数据11111010,并将基带数据送至调制模块modulate.v。modulate.v模块产生正弦波、ASK、PSK和FSK信号。波形输出选择控制逻辑根据串口指令输出对应的波形信号,经信号处理板上的DA转换及滤波电路后,形成模拟波形输出。

4 资料清单

1)FPGA工程源程序(提供网盘链接)

2)开发工具(提供网盘链接):QuartusII 13.1/

ModelSimSE 10.1c/Verilog HDL/Matlab2014a/串口调试助手

安装方法请关注B站UP主:杜勇FPGA 观看“FPGA环境安装”合集

3)工程代码讲解视频(杜勇老师主讲,mp4格式,可在线观看)

主要包括功能说明、FPGA代码讲解、ModelSim仿真过程、板载测试方法等完整的设计测试流程。

(试看)程序功能视频

(试看)系统测试视频 FPGA程序设计视频及FPGA工程源程序(付费后可见)

审核编辑 :李倩

-

信号发生器是干什么用的 信号发生器和示波器怎么连接2024-01-30 4854

-

函数信号发生器的原理是什么?如何用函数信号发生器产生共模信号?2023-11-20 3370

-

简单的信号发生器电路2023-06-08 866

-

什么是信号发生器 信号发生器类型总结2022-08-02 6191

-

使用Verilog硬件描述语言实现简易函数发生器的设计说明2020-09-27 2232

-

iBoard教程之(dds信号发生器)任意波发生器硬件电路分析2017-10-29 1478

-

脉冲信号发生器原理2017-10-26 23611

-

信号发生器原理_DDS芯片及应用_DDS信号发生器设计2015-06-23 8156

-

电路设计宝典:信号发生器设计锦集2014-08-26 33859

-

基于AD9857的信号发生器的设计2010-12-28 1031

-

信号发生器仿真电路2010-04-20 2932

-

信号发生器2009-09-24 937

-

忙音信号发生器电路2009-03-29 502

-

实用的多种波形信号发生器电路2007-06-13 1672

全部0条评论

快来发表一下你的评论吧 !