多轨供电系统中的监控和排序

描述

今天的电子系统可能有许多不同的电源轨。在采用模拟电路以及微处理器、DSP、ASIC 和 FPGA 的系统中尤其如此。为实现可靠、可重复的操作,需要控制每个电源电压的开关时序、上升和下降速率、应用顺序和幅度。给定的电源系统设计可能包括电源排序、电源跟踪以及电源电压/电流监测和控制。现有的电源管理IC可用于执行上电和断电的排序、跟踪和监控功能。

排序和跟踪设备可以监视和控制多个轨道;其功能可能包括设置导通时间和电压斜坡速率、欠压和过压故障检测、裕量调节(在标称电压值范围内的电源调整)和有序关断。用于这些应用的IC范围从简单的纯模拟器件(带有电阻器、电容和比较器)到高度集成的状态机和可编程器件(通过I进行数字控制)。2C总线。在某些情况下,系统的稳压器和控制器可能包括关键控制功能。

采用多个开关控制器和稳压器的系统的另一个考虑因素是如何最大限度地降低它们在不同开关频率下工作时产生的系统噪声。通常需要同步稳压器的时钟。事实上,当今许多高性能开关控制器和稳压器都可以同步到外部时钟。

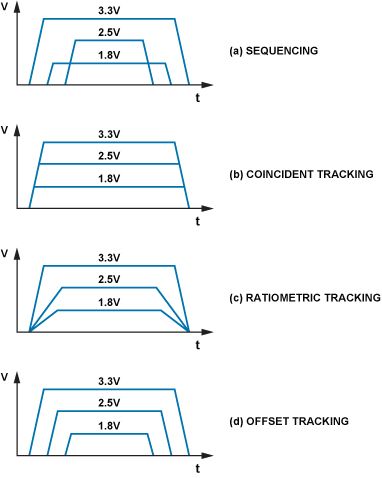

图1.电源轨控制的类型。

电源排序和跟踪

电源排序需要按特定顺序打开或关闭电源。电源序列的控制可以简单地基于既定的时间顺序,或者电源的导通时间可能取决于另一个电源达到编程阈值。电源跟踪基于这样一个事实,即电源不能(通常也不应该)提供其电压的瞬时变化;电源系统设计人员可以有利地利用这一点来控制每个电源相对于系统中其他电源的压摆率。供应跟踪分为三类:重合、比率和偏移。图 1 显示了四个图表,分别比较了排序、重合跟踪、比率跟踪和偏移跟踪。

在图1a中,三个电源的打开和关闭顺序是定时的。这里首先是3.3 V电源,后续电源的导通和关断延迟时间取决于应用的需求。这种简单的排序技术可以确保不超过有源元件的最大额定值,如果这些额定值要求按特定顺序激活电源。这方面的一个例子是,在驱动ADC的放大器上电之前,需要保证ADC的电源存在,如果不提供此电源,可能会导致ADC前端损坏。

在图1b(同步跟踪)中,所有三个电源同时导通,并以相同的速率相互跟踪,因此在施加较高电源电压之前建立最低电源电压。掉电以相反的方式完成。这是一个很好的例子,说明在较旧的FPGA或微处理器应用中如何启动电源,在辅助或I/O电源启动之前,较低的内核电压应该处于活动状态。本文稍后将展示赛灵思 Virtex-5 FPGA 的同步跟踪示例。

在图1c中,电源以不同的压摆率启动。如前所述,控制电源压摆率dV/dt的能力对于防止电路中的大去耦电容浪涌电流(充电电流)损坏非常有用。如果不加以控制,浪涌电流可能会大大超过正常工作电流。压摆率限制可以防止有源器件闩锁、电容器短路、PCB走线的潜在损坏以及直插式保险丝熔断。

在图1d中,所有电源都具有相同的压摆率,但其应用时间由预定的失调电压决定。这种类型的跟踪适用于需要限制电源电压差的设备;通常出现在混合信号元件(如DAC和ADC)的最大额定值部分。这种方法可以防止对零件造成永久性损坏。

基于 FPGA 的设计示例

使用FPGA的系统供电为处理多个电源系统的主题提供了很好的对象课程。正确控制FPGA电源可以决定可靠、可重复的设计与实验室中或更糟糕的现场可能出现的灾难性故障。大多数FPGA具有多个电源轨,通常标记为V首席运营官, V科考和 VCCINT.这些电源分别用于为 FPGA 内核、辅助电路(如时钟和 PLL)和接口逻辑供电。

这些电源轨的考虑因素可分为:

轨道的排序

轨道电压的公差要求

可能需要电源的软启动或压摆率控制。

作为说明性示例,请考虑 Xilinx Virtex-5 系列 FPGA 的电源要求,该系列提供广泛的功能,包括逻辑可编程性、信号处理和时钟管理。根据数据手册,Virtex-5 需要 V 的上电序列CCINT, V科考和 V首席运营官.这些电源相对于地的斜坡时间为200 μs(最小值至50 ms最大值)。推荐的工作条件如表1所示。

表 1.赛灵思 Virtex-5 电源轨要求

| 电压范围 | 最小/最大电压 | 当前 | 启动时间(分钟) | 启动时间(最大) | ||

| VCCINT | 1 V ± 5% | –0.5 V 至 +1.1 V | 4 安培 | 200 微秒 | 50 毫秒 | 在 V 之前打开科考/V首席运营官 |

| V科考 |

2.5 V ± 5% |

–0.5 V 至 +3.0 V |

~50毫安 |

200 微秒 |

50 毫秒 | 在 V 之前打开首席运营官 |

| V首席运营官 |

3 V ± 5% |

–0.5 V 至 +3.75 V |

<50毫安 |

200 微秒 |

50 毫秒 |

如前所述,Virtex-5需要同步电压跟踪。此外,电源必须在特定的推荐工作容差范围内,并且必须在指定的dV/dt范围内上升和下降。

但FPGA只是一个更大系统的一部分。为了详细说明此示例,假设有一个高电流 5V 主系统电源轨。为 FPGA 内核供电的 1V 电源容差为 ±5% (±50mV),需要提供高达 4A 的电流。3V 电源是容差为 ±5% 的通用逻辑电源,在本例中,需要提供 4A 电流才能为 FPGA I/O 和设计中的其他逻辑器件供电。2.5 V电源是一种模拟电源,必须提供100 mA的低噪声电流。

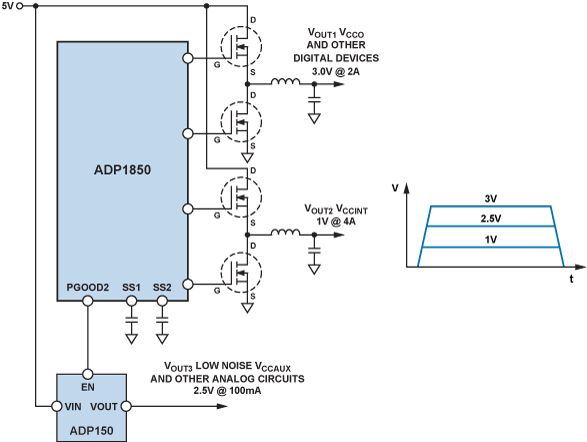

此应用的一个良好解决方案是采用双通道降压控制器ADP1850,用于1 V和3 V大电流电源。ADP1850的特性包括软启动控制、同步跟踪以及从电源与主电源时序控制。上电斜坡速率由 SS1 和 SS2 引脚上的电容器控制。在本例中,3 V数字电源是主电源。对于2.5 V模拟电源,ADP150超低噪声低压差稳压器(LDO)是绝佳选择;它可以从ADP1850的PGOOD2信号进行排序。系统简化图示,显示了一般时序控制流程,如图2所示(有关完整详情,请参见ADP1850数据手册)。

图2.用于 Virtex-5 的电源系统。

上面的例子说明了排序和跟踪的常见用法;它可以扩展到当今的许多多电源系统,包括基于微处理器的系统以及涉及混合信号技术的ADC和DAC系统。

模拟电压和电流监控 (ADM1191)

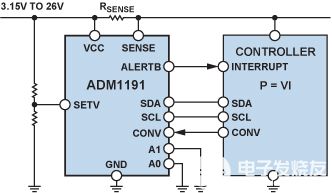

对于需要精确监控多个系统电源电流和电压的高可靠性应用,可以使用易于部署的模拟监控电路。例如,测量精度为1%的数字功率监控器ADM1191包括一个用于电流和电压回读的12位ADC、一个精密电流检测放大器和一个提供过流中断的ALERTB输出。图3显示了ADM1191在具有主机控制器(如微处理器或微控制器)的应用中的应用。

图3.一个简单的电源电压和电流监视器。

ADM1191通过进行通信I2C 总线到主机控制器。通过配置其A0和A1引脚的逻辑输入电平,同一系统中总共可以寻址16个器件。本地控制器可以通过将测量的电压和电流相乘来计算电源轨上的功耗。ALERTB 信号通过中断控制器快速通知过流情况,即快速警告故障情况,以帮助保护系统免受损坏。

结合测序和监测

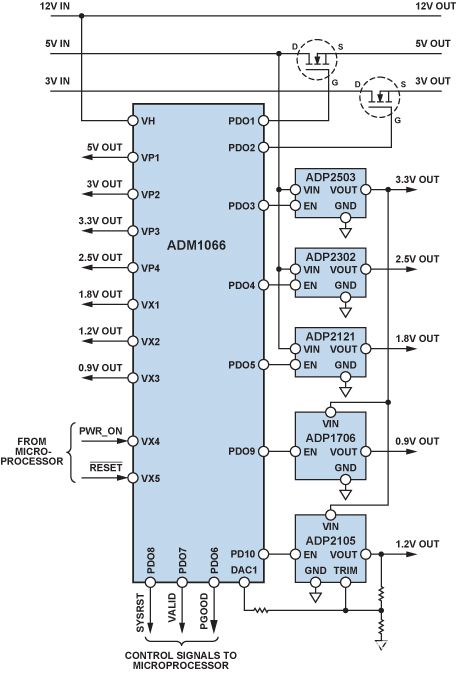

大型固定系统,甚至一些高性能插件卡,都有许多需要控制和监控的电源轨。图4显示的是一个具有8个电源轨的复杂电源系统。该系统的核心是ADM1066,这是一款灵活的高度集成的超级时序控制器,可提供完整的功率控制。功能包括排序、监控、裕量调节和可编程性。ADM106x系列中的其他器件增加了温度监控和看门狗功能。

图4.控制 8 轨电源系统。

8 轨系统有三个主电源轨:12 V、5 V 和 3 V。其他电源轨由这些电源轨派生而成,使用开关稳压器和LDO。每个稳压器都有一个使能输入,由ADM1066的10个可编程驱动器(PD)输出之一驱动,从而允许用户按受控顺序启动所有电源轨。ADM1066内置电荷泵,可升压6个PD输出电压,为外部N-MOSFET提供高压驱动,在需要控制更高电压电源的情况下充当电源轨开关。

ADM1066具有板载EEPROM,用于存储电源系统控制参数。ADI公司提供的实用程序可简化器件配置。这使得启动和运行的任务变得更加容易,消除了耗时的代码开发。随着系统的发展和新部件的加入,可以轻松调整供应顺序。时序参数和电压跳变点可轻松重新编程。这一有价值的功能可节省开发时间并降低可能的电路板旋转风险。

数字输出信号——PWRGD(电源良好)、VALID和SYSRST(系统恢复)——由ADM1066生成,用于在轮询时或通过中断或数字输入通知系统微控制器电源系统的状态,以便在存在故障情况时采取措施。这种快速通知可以防止电容器短路和其他危险情况造成的灾难性损坏。PWR_ON和/RESET是系统控制器到ADM1066的数字输入,完成整个系统控制环路。

ADM1066的电源裕量调节

ADM1066的片内DAC可用于在系统开发期间执行电源裕量调节,当设计人员需要调整电源电压以优化其电平或使其远离标称值时。这种裕量调节功能允许系统在电源限值范围内进行全面表征,而无需使用外部仪器。该功能通常在在线测试(ICT)期间执行,例如,当制造商希望保证被测产品在标称电源电压范围内±5%时正常工作时。从图4所示电路开始,用户可以在许多电源轨上实现裕量调节。

开环电源裕度

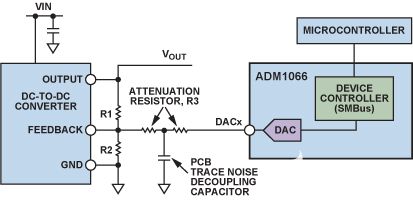

对电源进行裕量调节的最简单方法(例如DC-DC转换器或LDO)是将额外的电阻开关到电源模块的反馈节点中,以改变反馈或微调节点处的电压,从而使用DAC强制输出电压按所需量向上或向下裕量调节。使用这种衰减器(图5),可以通过更新相关DAC输出上的值,使用SMBus远程命令ADM11066为电源裕量。该过程可以使用开环技术实现,独立于系统控制回路。

图5.开环裕量。

ADM1066可以使用六个板载电压输出DAC(DAC1至DAC6)驱动到被裕量调节的功率模块的反馈引脚,从而对多达6个电源执行开环裕量调节。实现此功能的最简单电路是衰减电阻(R3),它将DACx引脚连接到DC-DC转换器的反馈节点。当DACx输出电压设置为等于反馈电压时,没有电流流入衰减电阻,DC-DC转换器输出电压不会改变。使DACx高于反馈电压迫使电流进入反馈节点,DC-DC转换器的输出必须下降以补偿这一点。为了提高DC-DC转换器输出,DACx输出电压设置为低于反馈节点电压。为了降低噪声,如图所示,串联电阻可以分成两个电阻,它们之间的节点可以通过DC-DC转换器上的电容对地去耦。

闭环电源裕度

更准确和全面的裕量计算方法在闭环系统中使用类似的电路。图4显示了1.2 V输出的示例。要裕量调节的电源轨上的电压可以通过VX2回读,以将电源轨精确地裕量到目标电压。ADM1066集成了实现此目的所需的所有电路,12位逐次逼近型ADC读取监控电压电平,6个电压输出DAC如上所述调整电源电平。这些电路可与其他智能(如微控制器)一起使用,以实现闭环裕量调节系统,该系统允许将任何DC-DC转换器或LDO电源设置为任何电压,精确到目标的±0.5%以内。

要在要测试的轨道上实现闭环裕量调节,请使用以下步骤:

禁用六个 DACx 输出。

将DACx输出电压设置为等于反馈节点上的电压。

启用 DAC。

读取连接到 VPx、VH 或 VXx 引脚之一的 DC-DC 转换器输出端的电压。

如有必要,向上或向下修改DACx输出电压以调整DC-DC转换器输出电压。否则停止;已达到目标电压。

将DAC输出电压设置为一个值,该值使电源输出改变所需的量(例如,±5%)。

重复该过程,直到达到该电源轨所需的电压。

步骤1至3确保当每个DACx输出缓冲器导通时,它对DC-DC转换器输出几乎没有直接影响。DAC输出缓冲器设计为上电时不会出现瞬态“毛刺”,方法是先上电缓冲器以跟随引脚电压。它此时不驱动引脚。正确使能输出缓冲器后,缓冲器输入切换到DAC,缓冲器的输出级导通,几乎消除了输出毛刺。

开关稳压器的同步

在使用多个开关稳压器或控制器的具有多个电源轨的系统中,由于内部开关频率的差异,这些器件存在交互的可能性。这可能会导致拍频谐波,从而大大增加电源噪声并对EMI测试造成严重破坏。幸运的是,许多开关控制器和稳压器的设计允许其内部时钟同步。LDO 不存在这个问题,但由于它们的电流输出有限,并且在大多数情况下效率低下,并不总是希望使用它们。

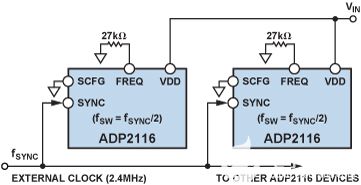

双通道开关稳压器ADP2116是可同步器件的一个很好的例子。其 SYNC/CLKOUT 引脚可通过 SCFG 引脚配置为输入 SYNC 引脚或输出 CLKOUT 引脚。作为输入SYNC引脚,它将ADP2116同步至外部时钟;两个通道以外部时钟频率的一半切换,彼此异相 180°。

作为 CLKOUT 引脚,它提供的输出时钟是通道开关频率的两倍,异相角度为 90°。因此,配置为CLKOUT选项的单个ADP2116可以充当主转换器,并为所有其他DC-DC转换器(包括其他ADP2116器件)提供外部时钟(图6)。它们配置为从站,接受主站的外部时钟并与之同步。通过同步系统中的所有DC-DC转换器,这种方法可以防止可能导致EMI问题的拍频谐波。

图6.从外部时钟同步ADP2116。

结论

本文讨论处理多个电源系统的方法。时序控制器、监视器、稳压器和控制器提供的高度功能集成使设计人员无需使用充满分立IC的电路板即可解决潜在的电源问题,这种功能为设计人员提供了良好的价值,并以最少的重新设计和电路板旋转增加了成功设计的几率。

审核编辑:郭婷

-

牵引供电系统的监控测试系统的设计及应用方案2021-03-09 5866

-

PCB电源供电系统设计概览与分析2018-09-11 2163

-

电源供电系统设计指南2018-11-19 2039

-

多轨预偏置负载应用的灵活排序方法详解2019-06-04 1011

-

多轨电源设计的排序2019-07-24 1341

-

电池供电系统中的电子开关和保护2019-09-30 2371

-

如何去实现PCB电源供电系统的设计?2021-04-26 1842

-

简述轨道交通直流供电系统的开关设备2010-08-26 1001

-

供电系统的谐波2008-11-23 1567

-

基于AM3359的管轨牵引供电系统监控平台2016-01-04 981

-

详细解释三类TN式供电系统2018-01-26 35796

-

面向多轨预偏置负载应用的灵活排序2021-03-18 555

-

电池供电系统中的电子开关与保护2021-05-18 908

-

供电系统的供电质量电压指标2023-12-13 2557

-

临时用电供电系统模式设置的问题2024-01-02 2423

全部0条评论

快来发表一下你的评论吧 !