一个全面的处理器性能评估方案

处理器/DSP

描述

处理器的评估其实是一个很复杂的事情。很多软件、机构都在做相关的工作,但是往往大家都会在表象层面进行讨论。其背后的问题其实并不复杂,但是由于手机、电脑厂家为了用一个量化的“数值”来标榜自己,所以会针对这个分值进行优化,特别是一些KPI文化的厂家,手机跑分很牛,打游戏却很卡。其背后的原因,我们理解处理器的评估方法之后,就很清楚了。

1、主频

我们知道“身大力不亏”,如果跟一个大体重、大身高的对手打架,对方的基础数据是非常说明实力的。我们一般观测一个处理器水平如何,一般我们首先先看主频数值,和处理器的核数。

主频也叫时钟频率,单位是Hz,用来表示CPU的运算速度。它决定计算机的运行速度,随着计算机的发展,在同系列微处理器,主频越高就代表计算机的速度也越快,但对于不同类型的处理器,它就只能作为一个参数来作参考。另外CPU的运算速度还要看CPU的流水线的各方面的性能指标。由于主频并不直接代表运算速度,所以在一定情况下,很可能会出现主频较高的CPU实际运算速度较低的现象。因此主频仅仅是CPU性能表现的一个方面,而不代表CPU的整体性能。

这也就是说一个人如果又高又壮,但是未必能打得过泰森。拳击比赛,身高体重一定有优势,但是不是胜负的评判标准。类比于人脑,就是说,反应快,但未必智商高。但是智商高的人,反应一般都快。

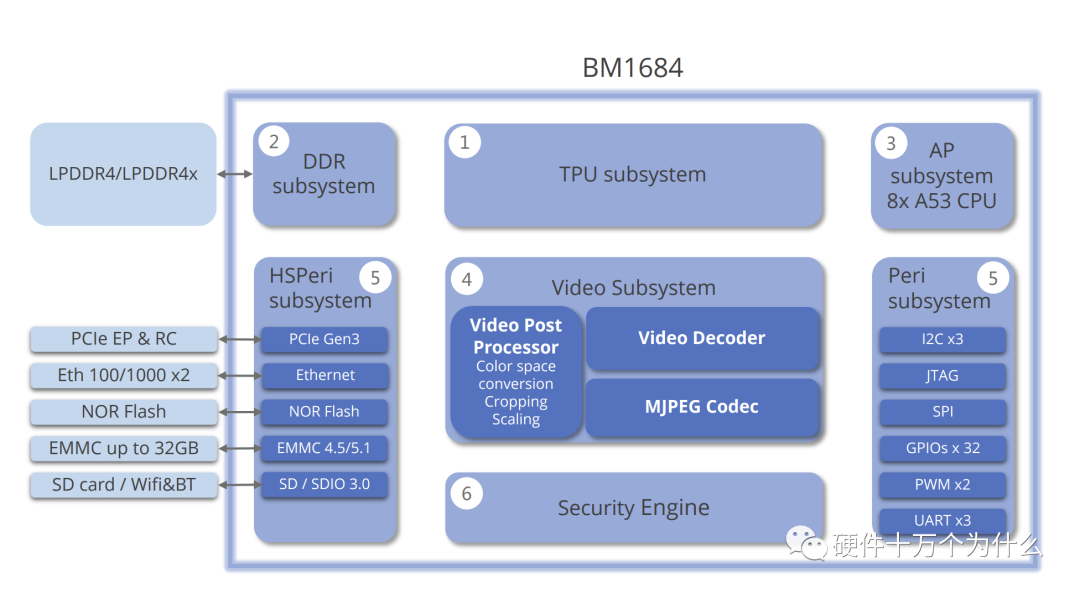

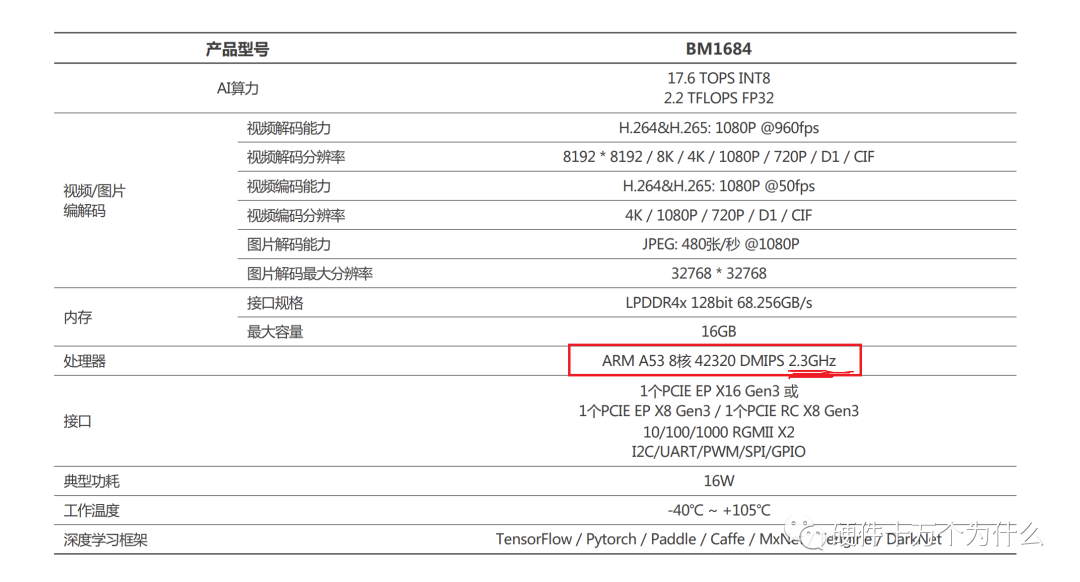

但是,如果是相同的处理器架构,则主频高,一定会比相同处理器架构的要强。也就是说,同比例放大泰森到身高两米,力量也同比例放大,再跟泰森本人PK。那么放大版泰森必胜。如下图中TPU的处理器内核是8核的Cortex-A53,但是处理器主频却高达2.3GHz,那么它一定比同为8核A53的其他处理器性能强。在其他条件相同的的情况下,处理器的主频彰显处理器实力。

对于我们买电脑的时候也一样,如果选择X86处理器的时候,我们选择AMD的处理器,有时主频非常高,但未必有Intel处理器跑得流畅。如果我们同时选择Intel的处理器,但是第几代酷睿,i3、i5、i7、i9确定的前提下,主频越高越好。但是主频高的9代i3未必有更低主频的11代酷睿i5好用。

也就是说姚明虽然又高又壮,但是应该是打不过泰森的。

2、核数

核数多,就是多人作战。多人,当然好,但是中国有句老话“一个和尚挑水喝、两个和尚抬水喝,三个和尚没水喝。”,虽然多核没有那么夸张。但是多核没有调度好,可能也是白搭。

多核不一定会使你的手机或电脑速度更快,但它将提高你的PC或者硬件系统的整体性能,这是一个有所不同的细微的技术特色。多核处理器的性能提升并不是简单CPU核心的倍数,因为受到两(多)个核之间共享资源的拖累。比如双核性能只是单核的1.4~1.8倍,实际情况取决于具体的应用。

首先跟实际应用有很大关系:

性能指标评测通常分为单核分数和多核分数。

单核分数与轻线程的游戏和应用程序更为相关,这意味着它们依靠单个内核来处理许多(但不是全部)指令。

多核分数与重线程的游戏和应用程序更相关,这意味着它们在多个内核之间分配指令。

您如何判断游戏是轻线程还是重线程?

打开任务管理器。运行游戏后,在 Windows 10 中打开任务管理器 (CTRL+SHIFT+ESC) ,然后单击“性能”选项卡。您会看到一个 CPU 使用率活动图。

配置 CPU 图表。右键单击图形,然后单击“将图形更改为逻辑处理器”。您会看到每个 CPU 内核上的负载将分别显示出来。

比较内核活动。如果游戏内容不多,那么大部分活动将被隔离到一个内核。

从架构上区分

同构多核架构:系统中的处理器在架构上是相同的

异构多核架构:系统中的处理器在架构上是不同的

同构多核架构在硬件与软件设计上比较简单,通用性高。

异构多核处理器有:TI的达芬奇平台DM6000系列(ARM9+DSP)、Xilinx的Zynq7000系列(双核Cortex-A9+FPGA)、Cell处理器(1个64位POWERPC+8个32位协处理器)等等。

同构多核处理器有:Exynos4412,freescale i.mx6 dual和quad系列、TI的OMAP4460等,Intel的Core Duo、Core2 Duo等。

从运行模式上区分:AMP/SMP/BMP

在软件上区分的话,多核处理器有三种运行模式:

AMP(非对称多处理)

SMP(对称多处理)

BMP(受约束多处理)

AMP

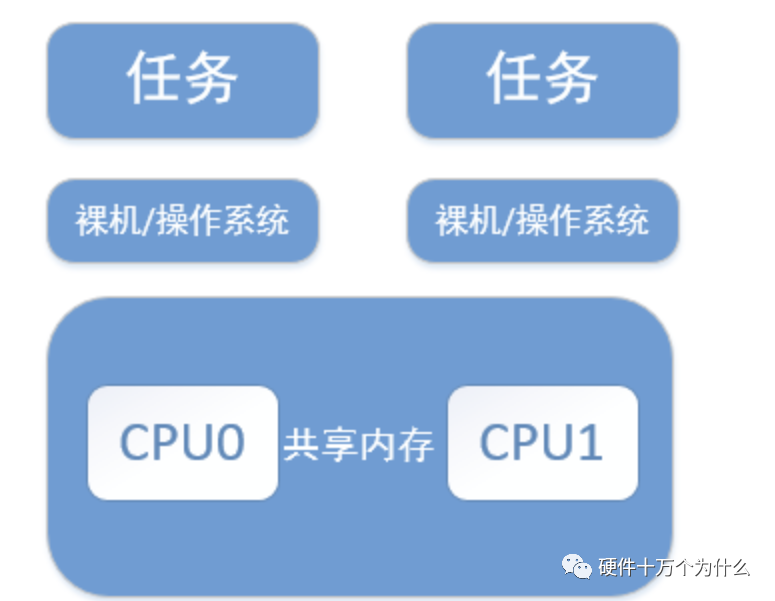

AMP是指,多个核相对独立地运行不同的任务,每个核之间相互隔离,可以运行不同的操作系统或裸机程序。

AMP运行模式

AMP的运行模式基本不会存在开销问题,尤其是在运行裸机程序时,甚至没有开销,这种模式比较适合实时性高的应用。但是两个核心之间的通信与资源共享需要有一套优秀的处理机制。

虽然多个核心可以运行不同的系统,但是需要有一个主要的核心,需要使用该核心来控制整个系统以及其他的核心。例如:一个核心运行运行实时性较高的任务,另一个核心运行UI界面。

AMP:

SMP:

SMP是指多个核心运行一个操作系统,该操作系统同等的管理多个内核,这种运行模式就是简单提高运行性能。目前支持该运行模式的操作系统有:Linux,Windows,Vxworks。

目前,我们的PC机使用的就是这种运行模式,一般适用于功能复杂,对实时性要求不高的系统。

SMP运行模式BMP

BMP运行模式与 SMP类似,同样也是一个OS管理所有的核心,但开发者可以指定将某个任务仅在某个指定内核上执行 。

多核的出现还让系统设计变得更加复杂。如运行在不同内核上的应用为了互相访问、相互协作,需要进行一些独特的设计,如高效的IPC(进程间通信,interprocess communication)机制、共享内存的数据结构和同步原语(synchronization primitives)。

程序代码迁移(code migration)也是个问题。大多数系统厂商都在针对单核CPU架构的代码库上进行了大量投资。因而,这些公司需要有一个清晰的迁移策略,来使其代码可以最大化地利用多核硬件资源。

针对多核设计的操作系统可能会大大减少解决上述挑战所需的工作量,也可能增加另一些问题的复杂性。这全都取决于操作系统是如何支持多核芯片的多处理模式。多处理模式主要有以下三种:

| 非对称多处理(Asymmetric multiprocessing,AMP) | 每个CPU内核运行一个独立的操作系统或同一操作系统的独立实例(instantiation) |

| 对称多处理(Symmetric multiprocessing,SMP) | 一个操作系统的实例可以同时管理所有CPU内核,且应用并不绑定某一个内核 |

| 混合多处理(Bound multiprocessing,BMP) | 一个操作系统的实例可以同时管理所有CPU内核,但每个应用被锁定于某个指定的核心 |

但是有个处理器,其实就是将两颗,或者多颗处理器集成在一起,可以看成是两个完成独立的处理器,都不像AMP那样共享内存,有自己独立的内存空间。可以看成是完全独立的处理器,只不过从芯片的角度是一颗芯片。这种情况在有些场景下是有用的,例如一些工控场景,我们需要一个处理器单独做一些事情,如果没有这个处理器,我们会用一个MCU来单独做一些实时性的任务。

3、流水线

处理器内核中的流水线越多,当然性能响应的会越好。但是流水线太多,在异常出现的时候,会导致计算回退,反而导致更低效率。

流水线处理概述

CPU主要工作方式:

顺序

重叠

流水

和铺地板的原理相似…

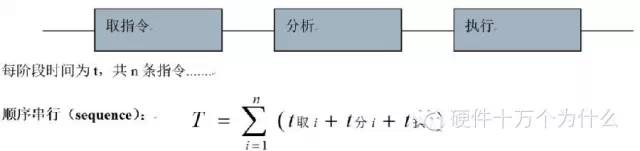

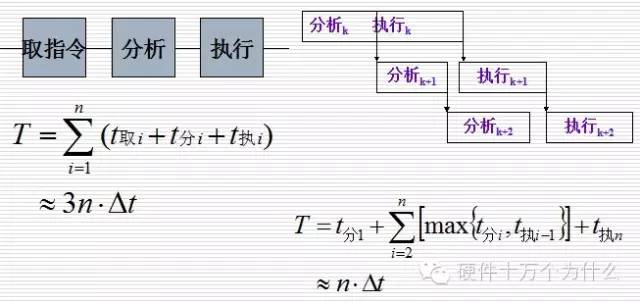

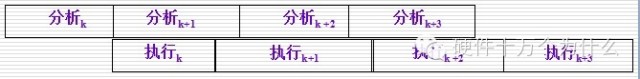

设指令工作方式分成取指令、分析、执行指令

若各阶段执行时间相等,则共需3n t

优点:控制简单;

缺点:速度慢,机器各部件的利用率很低。

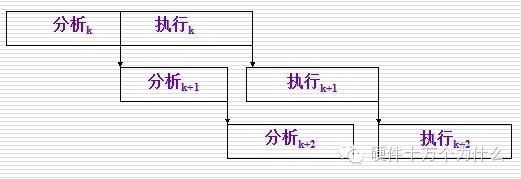

重叠(Overlap):在两条相近指令的解释过程中,某些不同解释阶段在时间上存在重叠部分。

包括一次重叠、先行控制技术和多操作部件并行。

将相邻两条指令的重叠时间再往前提前一个阶段;T=3×t+(n-1)×t=(n+2)×t

一次重叠:把取指令操作隐含在分析、执行指令过程中,则在任何时候只允许上条指令“执行”与下条指令“分析”相重叠。T=(n+1)×t

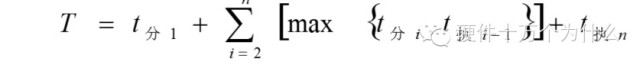

若各段时间不等时,有实际执行时间:

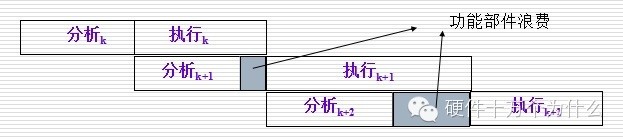

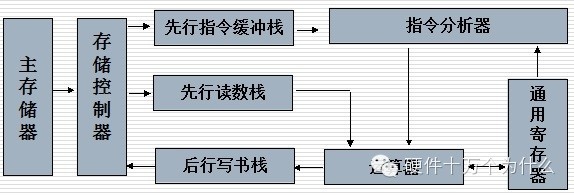

先行控制:分析部件和执行部件能分别连续不断地分析和执行指令,预取和缓冲相结合的技术 ,通过对指令流和数据流的先行控制,使指令分析器和执行部件能尽量连续并行工作。

执行时间:

多操作部件并行:采用有多个功能部件的处理机,把ALU的多种功能分散到几个具有专门功能的部件中,这些功能部件可以并行工作,使指令流出速度大大提高。

先行控制:现代计算机指令系统是复杂的,“分析”和“执行”所需要的时间往往相差很大,从而造成功能部件的浪费,因此,需要采用先行控制技术。

分析指令和执行指令时间不等时的一次重叠方式

采用先行缓冲栈是指令执行过程的一种表示方法

先行控制:

一般采用先行缓冲栈的方式实现:

一般设置四种缓冲栈:

先行指令缓冲栈

当主存比较忙时,指令分析器能够从先行指令缓冲栈中得到所需指令。

先行操作栈

对于条件转移等使用。

先行读书栈

主存储器和运算器之间的缓冲存储器,用来平缓运算器和主存储器之间的工作。

后行写数栈

当前没有完全写道主存的数据可以暂存到写数栈

先行控制的处理机结构:

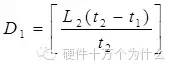

先行控制中的缓冲深度设计:

通过一种极端情况计算举例:

假设先行指令缓冲栈已经完全充满,缓冲深度是D1。

此时指令缓冲栈输出端,指令流出速度最快,而输入端,流入最慢

假设指令序列的最大长度是L1,平均分析一条指令的时间是t1

而此时更坏的是取指令很慢,平均取一条指令的时间是t2

假设先行控制栈充满到被取空的过程中指令分析条数是L1

则此时有:L1t1 = (L1-D1)t2

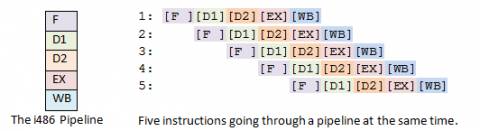

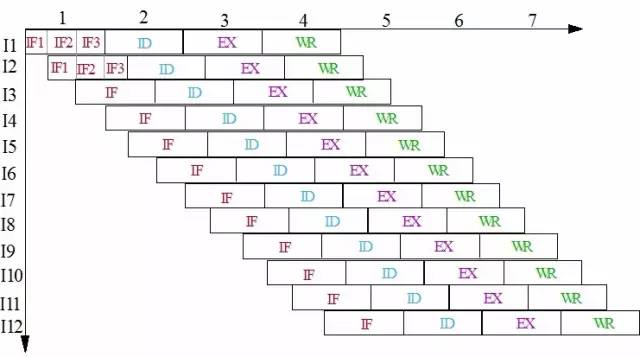

1989年推出的i486处理器引入了五级流水线。这时,在CPU中不再仅运行一条指令,每一级流水线在同一时刻都运行着不同的指令。这个设计使得i486比同频率的386处理器性能提升了不止一倍。五级流水线中的取指阶段将指令从指令缓存中取出(i486中的指令缓存为8KB);第二级为译码阶段,将取出的指令翻译为具体的功能操作;第三级为转址阶段,用来将内存地址和偏移进行转换;第四级为执行阶段,指令在该阶段真正执行运算;第五级为退出阶段,运算的结果被写回寄存器或者内存。由于处理器同时运行了多条指令,大大提升了程序运行的性能。

处理器一般由如下功能单元组成:

取指单元

译码单元

执行单元

Load/store单元(load用于从内存中取数据,而STORE用于存储数据到内存)

例外/中断单元

电源管理单元

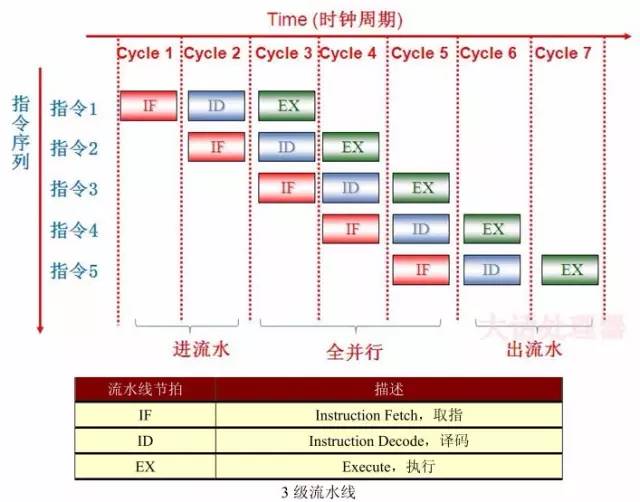

流水线通常由取指、译码、执行及Load/Store等单元组成。各单元按图所示的几个步骤循环重复自身工作。

流水线的含义:

与工厂生产线类似,将一件工作分成若干个固定的工序进行。

cpu流水线技术是一种将指令分解为多步,并让不同指令的各步操作重叠,从而实现几条指令并行处理,以加速程序运行过程的技术。指令的每步有各自独立的电路来处理,每完成一步,就进到下一步,而前一步则处理后续指令。(原理和生产流水线一样)

CPU指令流水线

根据之前描述的基础,指令进入流水线,通过流水线处理,从流水线出来的过程,对于我们程序员来说,是比较直观的。

I486拥有五级流水线。分别是:取指(Fetch),译码(D1, main decode),转址(D2, translate),执行(EX, execute),写回(WB)。某个指令可以在流水线的任何一级。

但是这样的流水线有一个明显的缺陷。对于下面的指令代码,它们的功能是将两个变量的内容进行交换。

|

1 2 3 |

XOR a, b XOR b, a XOR a, b |

从8086直到386处理器都没有流水线。处理器一次只能执行一条指令。在这样的架构下,上面的代码执行并不会存在问题。

但是i486处理器是首个拥有流水线的x86处理器,它执行上面的代码会发生什么呢?当你一下去观察很多指令在流水线中运行,你会觉得混乱,所以你需要回头参考上面的图。

1、第一步是第一条指令进入取指阶段;

2、然后在第二步第一条指令进入译码阶段,同时第二条指令进入取指阶段;

3、第三步第一条指令进入转址阶段,第二条指令进入译码阶段,第三条指令进入取指阶段。

4、但是在第四步会出现问题,第一条指令会进入执行阶段,而其他指令却不能继续向前移动。

5、第二条xor指令需要第一条xor指令计算的结果a,但是直到第一条指令执行完成才会写回。

所以流水线的其他指令就会在当前流水级等待直到第一条指令的执行和写回阶段完成。第二条指令会等待第一条指令完成才能进入流水线下一级,同样第三条指令也要等待第二条指令完成。

这个现象被称为流水线阻塞或者流水线气泡。

常用概念:

1、流水线级数:流水线的节拍数。

2、吞吐率:单位时间内流水线能处理的任务数量。

3、最大吞吐率:流水线达到不间断流水的稳定状态后可获得的吞吐率。

4、加速比:流水方式的工作速度与等效的顺序工作方式时间的比值。

流水线指标:

1、流水技术无助于减少单个任务的处理延迟(latency),但有助于提高整体工作负载的吞吐率

2、多个不同任务同时操作, 使用不同资源

3、潜在加速比= 流水线级数

4、流水线的速率受限于最慢的流水段

5、流水段的执行时间如果不均衡,那么加速比就会降低

6、开始填充流水线的时间和最后排放流水线的时间降低加速比

低功耗嵌入式领域的ARM7就是采用3级流水线结构。

超流水

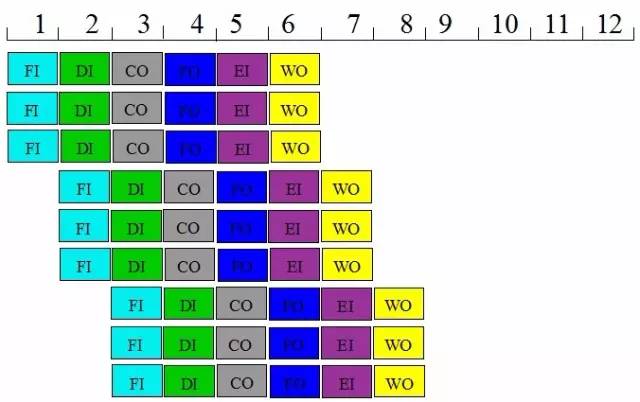

超流水线技术是通过细化的流水,提高主频。使得机器在一个周期内完成一个甚至多个操作,其实质是用空间换取时间。

超流水处理器是相对于基准处理器而言的,一般cpu的流水线是基本的指令预取,译码,执行和写回结果四级。超流水线(superpiplined)是指某型CPU内部的流水线超过通常的5~6步以上,例如Pentium pro的流水线就长达14步。将流水线设计的步(级)数越多,其完成一条指令的速度越快,因此才能适应工作主频更高的CPU。这一点我们可以用日常事例来说明,比如有5个人接力传送木头(对应一个5级的流水线),超流水是说细化该流水过程,即由10个人接力(此时为10级流水),显然完成全部任务的速度会快。相当于毛主席的一句话:人多力量大(效率高)。

超标量

超标量是指在CPU中有一条以上的流水线,并且每时钟周期内可以完成一条以上的指令,这种设计就叫超标量技术。其实质是以空间换取时间。

CPU架构是指在一颗处理器内核中实行了指令级并行的一类并行运算。这种技术能够在相同的CPU主频下实现更高的CPU吞吐率(throughput)。

4、指令与指令集

通过上面描述流水线,我们知道指令,是具体每一次处理器运行要干的事情。这里不可回避的一个问题就是“指令集”。

不同指令集的处理器,其主频相同的情况下,会有很大的差异。

这个也就是很多朋友经常会问到的一个问题:相同的主频,为什么ARM的性能会比X86差很多。

CISC是复杂指令集CPU,指令较多,因此使得CPU电路设计复杂,功耗大,但是对应编译器的设计简单。

RISC的精简指令集CPU,指令较少,功耗比较小,但编译器设计很复杂,它的关键在于流水线操作能在一个时钟周期完成多条指令。

同样的打拳,同样出拳速度都很快,马保国和泰森还是有很大差别的。

由于定位的不同,ARM处理器基于精简指令集(RISC)架构。指令集数量少就可以简化硬件逻辑的设计,减少晶体管数量,也就意味着低功耗。而且由于移动平台应用通常简单,程序的控制流不复杂,执行效率没有必要很高,所以流水线、分支预测等硬件逻辑都比较简单。这些都降低了晶体管总量。同时因为移动设备有电池的能源限制,ARM的电源管理是作为重要部分特别设计了的。比如移动设备的处理器在待机时通常只以极低的主频在运行,甚至可以暂时关闭闲置的核心、协处理器来降低功耗。

x86就截然不同。x86是复杂指令集(CISC)架构,存在很多机器指令,只为了高效地完成一项专门任务(比如MMX, SSE中的指令)。这就使得硬件的逻辑很复杂,晶体管数量庞大。为了高效地进行运算,x86架构有较长的流水线以达到指令级并行(ILP)。长流水线带来的一个弊端,就是当遇到分支时,如果预载入分支指令不是未来真实的分支,那么要清空整个流水,代价较高。所以x86为此还必须有复杂的分支预测机构,确保流水线的效率。再加上多级cache,支持超线程、虚拟化等等,x86的复杂度其实相当高。

对于ARM来说,能够直接调用的指令集相对少很多。每一个指令,都相当于我们开发FPGA时,固化下来的固定算法、固定电路。那么指令种类越多,则需要的逻辑资源也就越多。固化成处理器,其硅片面积就会大很多。

对于复杂指令集,本质是用硅片的面积换取计算的性能。而对于精简指令集,对于其自身没有的指令,需要用多次运行原本有的指令实现,相当于用多次计算来实现,牺牲了性能。但是ARM和X86的差异还有很多点,这里就是把最关键的点简化给大家讲清楚最基本的差别。

但是RISC指令集的处理器之间也是有很大差异的:MIPS、PowerPC、RISC-V、ARM之间还是有很多不同点。所以虽然他们相同主频和近似的指令集。但是具体的性能并不能只看以上四个指标。

5、MIPS、DMIPS

MIPS:million instruction per second,表示每秒多少百万条指令,如 10MIPS ,表示每秒一千万条指令。

MIPS/MHz :表示 CPU 在每 1MHz 的运行速度下可以执行多少个MIPS ,如 10MIPS/MHz,表示如果 CPU 运行在 1MHz 的频率下,每秒可执行一千万条指令,如果 CPU 运行在 5MHz 的频率下,每秒可执行五千万条指令。

DMIPS:Dhrystone MIPS,并非字面上每秒百万条指令的意思。它是CPU运行一个叫Dhrystone(整数运算)的测试程序时表现出来的相对性能高低的一个单位(很多场合人们也习惯用MIPS作为这个性能指标的单位)。

Dhrystone:是于1984年由Reinhold P. Weicker设计的一套综合的基准程序,该程序用来测试CPU(整数)计算性能。其名“Dhrystone”是与另一算法“Whetsone”区分而设计的名字。与Whetsone不同,Dhrystone并不包括浮点运算,其输出结果为每秒钟运行Dhrystone的次数,即每秒钟迭代主循环的次数。

Dhrystone的重要性在于其能作为处理器整数计算性能的指标。很多现代的编译器应用了静态代码分析技术,会将对输出没有影响的代码忽略,这会使很多基准测试代码不能正常运行,包括早些版本的Dhrystone。之后Weicker于1988年开发出了2.0版本,并于同年五月开发出了2.1版本,基本解决了这一问题。

Dhrystone所代表的处理器分数比MIPS(million instructions per second 每秒钟执行的指令数)更有意义,因为在不同的指令系统中,比如RISC(Reduced Instruction Set Computer精简指令集计算机)系统和CISC(Complex Instruction Set Computer复杂指令集计算机)系统,Dhrystone的得分更能表现其真正性能。由于在一个高级任务中,RISC可能需要更多的指令,但是其执行的时间可能会比在CISC中的一条指令还要快。由于Dhrystone仅将每秒钟程序执行次数作为指标,所以可以让不同的机器用其自身的方式去完成任务。另一项基于Dhrystone的分数为DMIPS(DhrystoneMIPS),其含义为每秒钟执行Dhrystone的次数除以1757(这一数值来自于VAX 11/780机器,此机器在名义上为1MIPS机器,它每秒运行Dhrystone次数为1757次)。

作为一项基准程序Dhrystone具有以下缺陷:

它的代码与具有代表性的实际程序代码并不相同。

它易受编译器影响。举例来说,在Dhrystone中有大量的字符串复制语句,用来测量字符串复制的性能。然而Dhrystone中字符串的长度不变,并且均开始于自然对齐的边界,这两点便与真实的程序不同。因此一个优化性能好的编译器能够在去掉循环的情形下通过一连串字符的移动代替对字符串的复制,这将会快很多,可能会高达30%。所以我们在编译测试程序的时候,如果指定编译器的优化等级的话,我们会发现在不同的优化等级下,表现出来的性能指标会有差别,优化等级越高,性能指标越好,以下是一款芯片在不同的优化等级下的指标参数

Dhrystone代码量过小,在现代CPU中,它能够被放进指令缓存中,所以它并不能严格的测量取指性能。

DMIPS/MHz:表示 CPU 在每 1MHz 的运行速度下可以执行多少个DMIPS,由于DMIPS与CPU频率具有正相关性,所以这一分数更容易比较不同的CPU在不同的时钟频率下运行Dhrystone的结果。

从上面的几个概念来看,都是为了评估cpu的性能—cpu的计算速度,由此引申开来,在软件行业,都需要一个基准测试程序,来评估某种性能----比如CPU的运算效率或者内存效率,我们称之为benchmark。比如在评估cpu运算速度领域,就有上面提到的dhrystone,coremark,whetstone等等;在评估内存效率上,有mem_test等等;评估web功能的有Apache Benchmark,Redis-Beachmark等等

dhrystone软件如何测试性能呢?

我们可以从网上搜到到dhrystone软件的source code。

其实也就是三个文件,分别是dhry.h、dhry_1.c、dhry_2.c。如果是在linux环境下开发的话,我们需要配置好makefile,然后编译并生成可执行程序,运行即可;如果在其他平台上,比如在ARM Cortex-M上开发的话,有些集成的IDE会自带这些功能。

根据以上介绍的基本概念以及知识,那么MIPS和DMIPS有什么区别呢?CPU性能的评估主要有两个方面:

每秒钟能够执行的指令集数量

显然MIPS反映的就是这方面的能力,这个能力由cpu的架构,内存memory的访问速度等硬件特性来决定

每秒钟能够实现的工作数量

DMIPS反映的就是这样的能力,这个能力除了包含第一部分的特性之外,还包括了这些指令集在实现我的测试程序的时候,是如何高效实现的呢?

举例来说,一个PIC16xxx的cpu,运行在20MHz主频,MIPS=5;但是这些指令只能处理8bit数据,并且不能处理除法和乘法运算,另外一个是一个8088的cpu,主频是5MHz,因此我们可以说PIC16xx在某些方面的性能比8088更快(比如在只有加减法运算的场合),在另外一些场合,8088的运算速度会比PIC16xx的更快,所以仅仅看MIPS的值,并不能够有效的反映的一款cpu性能

这里我们发现处理器性能评估的时候,只看MIPS和DMIPS有以下局限性:

a、相同MIPS的前提下,指令集,指令的种类和复杂度,影响实际性能。MIPS只能说明出拳速度,虽然你会闪电五连鞭,但是出拳的技巧,力量等各个维度的数值,才决定你是不是很强大。

b、DMIPS是让处理器做一件非常简单的事情,来反映处理器的性能。第一,处理器并不是只做这么简单的事情;DMIPS处理的是整数,当处理浮点数的时候性能需求与处理整数的时候性能表现有比较大的差异。

c、处理器的位宽没有参与评估。

6、SPEC

SPEC指标体系由Standard Performance Evaluation Corp.制定,目前主要包括针对CPU性能的SPEC CPU2000(已有CPU2006,但尚无数据)、针对Web服务器的SPECweb2005、针对高性能计算的SPEC HPC2002与SPEC MPI2006、针对Java应用的jAppServer2004与JBB2005以及对图形系统、网络和邮件服务器的测试指标。

| 缩略语 | 英文全名 | 中文解释 |

| SPEC | Standard Performance Evaluation Corparation | 标准性能评估组织 |

| Speed | Speed | SPEC CPU2000的一种测试方法,针对单一任务考察运行时间 |

| Rate | Rate | SPEC CPU2000的一种测试方法,针对固定时间考察完成任务量 |

| Base | Base | 只为所有的场景提供一种优化 |

| Peak | Peak | 为一个单独的场景提供所有的优化 |

其中CPU2000和web2005两类是被引用最广泛的指标。

CPU2000 注重CPU

SPEC CPU2000 是一组针对 CPU 和内存的测试,它主要测试的对象是 CPU、内存,不测试硬盘、I/O 效率和网络等部分。SPEC CPU2000 由许多源代码程序组成,这些程序都从实际的应用(主要来自配置1~4颗CPU的工作站应用)中取出来的,例如 164.gzip 就是gzip 压缩程序。这些程序区分成“整数”和“浮点数”两组。SPECint2000 就是“整数”部分,而 SPECfp2000 则是“浮点数”部分。“整数”部分有 12 个程序,使用 C 或 C++ 语言,它们不使用CPU的浮点单元;而“浮点数”部分有 14 个程序,使用 FORTRAN 77/90 和C语言,这些程序的主要运算是浮点数的。

SPECint2000 和 SPECfp2000 的结果,以执行时间为准。每个程序的执行时间和一个参考平台(Sun Ultra5/10 300MHz)相比,计算出其倍数。如果执行时间和参考平台相同,结果就是100。如果只花了一半时间完成,结果就是200。“整数”的12 个程序的结果,取其平均值,得到的就是SPECint2000 的测试结果。“浮点数”的 14 个程序也是一样。

由于SPEC CPU2000的测试程序都是源代码形式(以保证跨平台测试),所以编译器效率就显得十分重要。SPEC CPU2000规定,测试结果有“Base”和“Peak”两种结果。“Base”测试中,对于编译时的最佳优化参数有所规定(所有的程序都需使用同样的参数,且参数数目不能超过四个),而“Peak”测试则比较宽松。

另外,因为 SPEC CPU2000的程序都是针对单CPU的系统设计,因此,在多CPU系统上,如果要测试多CPU系统的效率,则是采取同时执行多个相同程序的方法,这个结果就是“Rate”。因此,同样有 SPECint_rate 和 SPECfp_rate 的测试结果。需要说明的是,“Rate”测试同时执行多个相同的程序,但程序之间并不会有关联,所以这是一种理论计算能力测试,并不代表实际并行计算能力。

SPEC测试需要注意的还有以下几点:

①SPEC CPU2006测试所得到的数据不能和CPU2000进行直接对比,因为它们是基于不同的算法结构。

②其次SPEC测试时,CPU基本是100%跑的,所以基本不能进行其他复杂的数据操作或者编译操作。

③测试过程时间较长,中间是不允许中断的,除非kill掉和SPEC相关的所有进行,results中的debug文件也只会保留kill进程之前的最后一个测试完成的场景结果。

如果发现最终的SPEC值过低,可以从以下几点中查找结果:

①编译器是否正确,是否符合进行测试的处理器。

②其次是指令集是否为此CPU的最佳指令集。

③内存的配置是否符合要求。

④处理器的实际工作频率是否达到它应有的频率。

⑤温度等外在的环境因素是否导致处理器降频使用。

如果单板不是用作服务器应用,一般的嵌入式应用,通常用MIPS作为指标进行评估。这里说的MIPS不是处理器架构,是其原本的含义。MIPS(Million Instructions Per Second):单字长定点指令平均执行速度 Million Instructions Per Second的缩写,每秒处理的百万级的机器语言指令数,这是衡量CPU速度的一个指标。像是一个Intel80386 电脑可以每秒处理3百万到5百万机器语言指令,即我们可以说80386是3到5MIPS的CPU。处理器架构相同的情况下,MIPS能够比较出处理器之间的性能关系,不同的处理器之间因为指令的功能、数量、效率并不相同,MIPS值仅做对比参考。不同版本的测试软件也会测试出不同的结论,所以对比两款处理器时应该选择相同版本的测试软件。

准确测试cpu的mips或者mflops一般是设计体系结构时候用cpu模拟器或者verilog前仿真得到的。对于用C语言比较准确的测试mips或者mflops,你可以用一个程序读取系统时间,然后执行第二个程序,第二个程序执行完成后再记录执行的时间,然后反汇编第二个程序,统计第二个程序中执行的指令条数,通常第二个程序中执行的指令数是确定的,(分支和循环的次数是可确定的)。mips和mflops在RISC CPU的评价中比较有价值。

处理器的主频提高与业务能力不是线性的,同样其测试结果也不代表其业务能力。有些处理器的实际性能用简单的评价标准并不能说明其业务能力,需要直接测试其业务能力。直接在demo板上移植业务软件,评估其业务能力是最可信赖的一种方式。例如选择多核DSP替代原有的单核DSP电路板时,直接测试多核DSP的G.711转码性能,与原先的单核DSP进行对比,可以得出具体的业务能力。然后根据其业务需求,评估需要在一块单板上安排多少数量。当然还需要评估成本、功耗、散热等维度的挑战。

7、鲁大师之类的软件对PC、手机的评分

类似鲁大师之类的软件,用自己的评分权重把处理器整点数、浮点数、多核运行、内存读写、3D特性的性能做了测试,然后按照自己的权重标准,给一个综合打分。

尽管 CPU 性能指标评测 很重要,但每个组件在系统性能中都能发挥作用。

CPU。具有复杂人工智能、物理和显卡后处理功能的游戏往往倾向于 CPU 密集型,并且可能会从具有更高内核/线程数和更高时钟速度的 CPU 中获益更多。

GPU。在评估系统的游戏性能时,除了 CPU 性能指标评测外,还要检查 GPU 性能指标评测,因为某些游戏更依赖于 GPU。例如,独立显卡可以处理 3D 渲染的大部分工作。

内存和存储。这些组件会影响系统的响应能力和加载时间。

软件。无论您的系统配置如何,性能都会因游戏不同而有所变化。这都会发生。这与游戏的编程方式有关。您正在玩的显卡设置和分辨率也会影响性能。

由于很多用鲁大师这样软件测试计算机性能的朋友,主要用PC来打游戏,所以游戏运行过程中的关键指标作为评估的主要依据,而像SPEC这样主要按照服务器应用来评估处理器以及周边硬件的性能。

同样手机跑分跟PC跑分是一个原理。

基准测试程序(Benchmark)用来测量机器的硬件最高实际运行性能,以及软件优化的性能提升效果,可分为微基准测试程序(Microbenchmark)和宏基准测试程序(Macrobenchmark)。

基准测试程序(Benchmark)用来测量机器的硬件最高实际运行性能,以及软件优化的性能提升效果,可分为微基准测试程序(Microbenchmark)和宏基准测试程序(Macrobenchmark)。微基准测试程序用来测量一个计算机系统的某一特定方面,如CPU定点/浮点性能、存储器速度、I/O速度、网络速度或系统软件性能(如同步性能);宏基准测试程序用来测量一个计算机系统的总体性能或优化方法的通用性,可选取不同应用,如Web服务程序、数据处理程序以及科学与工程计算程序。

为了达到上述目标,基准测试程序需要满足如下条件:首先。基准测试程序包含最常见的计算、通信和访存模式,能够为实际的应用程序预测不同高性能计算系统性能排名;其次,能指导高性能计算系统和应用的改进,亦即在基准测试程序上有效的优化方法能移植到实际应用中。

编辑:黄飞

-

多内核处理器应用趋势下的高性能视频系统设计2010-03-16 2726

-

评估通过Python快速开发异构处理器FPGA应用性能(PYNQ评测)2018-06-19 2942

-

询问DSP和处理器的开发环境等问题2018-11-02 2327

-

基于ARM Cortex-M4处理器与板载NAND闪存的ATSAM4E-EK评估套件2019-04-22 2072

-

SHARC处理器的评估系统2020-03-16 2237

-

网络处理器,什么是网络处理器2010-04-03 1011

-

苹果专门开发一个AI专用的处理器用以提升AI方面的性能2017-09-25 671

-

处理器系列之最全面的MIPS知识2018-01-26 2301

-

嵌入式开发的独立处理器和集成处理器的详细资料说明2019-04-26 1942

-

处理器型号和性能的查看方法2020-05-28 3739

-

英特尔酷睿Lakefield处理器推出,提供性能和全面的Windows兼容性2020-06-11 2888

-

微处理器在人工智能方面的应用2024-08-22 2335

-

盛显科技:解决投影融合处理器的性能评估标准2024-12-26 912

-

MAX1702评估套件:为微处理器应用提供高效电源管理方案2026-04-02 115

-

LP3972 USB评估板:助力先进处理器电源管理评估2026-04-22 233

全部0条评论

快来发表一下你的评论吧 !