基于eFlexPWM的多级串联载波移相脉宽调制技术实现

描述

参考方案简介

随着电力电子技术的发展,电力电子交直流变换装置应用日益广泛,移相载波技术可以有效的减小PWM调制过程中产生的谐波,被广泛应用到多相多电平等场合。 本文描述了使用eFlexPWM实现多级串联载波移相PWM输出的逻辑、外设配置及实现方法。 本参考设计主要向读者介绍了eFlexPWM强大功能,并给出了六路互补移相60°的PWM实例作为参考,可以指导客户快速实现想要的PWM输出模式。

eFlexPWM简介

eFlexPWM全称是:Enhanced Flex Pulse Width Modulator的缩写,直译为增强型灵活脉冲脉宽调制器。 i.MX RTxxxx系列一般具有1-4个强大的eFlexPWM(eFlexPWM1~eFlexPWM4)模块。每个eFlexPWM有4个子模块,可以产生四路互补PWM即产生8路PWM,也可以产生8路相互独立的PWM波。

每个eFlexPWM模块拥有一个向上计数的16位计数器,它仅在向上方向计数至VAL1值,然后重置为初始(INIT)值。在计数过程中,计数值与VAL2/VAL3/VAL4/VAL5寄存器中的值作比较,控制输出电平高低翻转。

PWM又有中心对齐、边沿对齐、移相和双开关模式。

每个eFlexPWM具有各自的故障检测电路,当故障发生时根据程序锁定PWM输出引脚的电平状态,这在逆变、整流及电机控制应用中能够有效的提高设备的安全性。eFlexPWM可以产生多种多样的开关模式,包括非常复杂的波形。它可以用来控制大部分已知的电机类型,用于控制开关电源也非常具有优势。

eFlexPWM主要特点

eFlexPWM脉宽调制器的主要特点如下:

16位精度,支持中央对齐、边沿对齐和非对称PWM输出;

分数PWM时钟生成器可生成高精度PWM周期和占空比;

可工作在互补输出模式或独立工作模式;

每个PWM输出双沿(上升沿/下降沿)可独立控制;

可与外部硬件或其他PWM子模块同步;

双缓冲PWM寄存器,可设置1~16的整数周期重载或半周期重载;

支持PWM输出的双切换(周期和占空比);

一个PWM周期可以产生多个输出触发事件;

故障输入可以指定连接控制多个PWM输出;

独立的可编程PWM输出极性设置;

独立的死区时间设置;

增强型双沿(上升沿/下降沿)捕获功能。

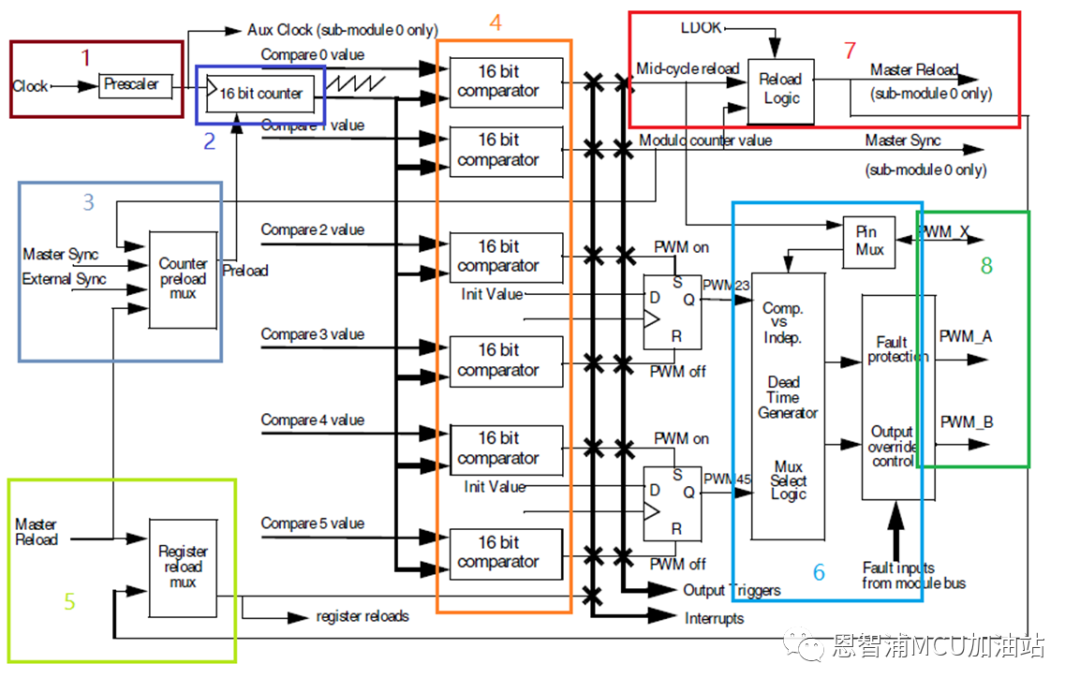

PWM子模块功能图

图1 PWM子模块功能框图

图1 PWM子模块功能框图

图中各个部分说明如下:

1是时钟源模块,可以选择不同的时钟源;

2是16位计数器;

3是同步寄存器,有四个同步信号供选择,可以初始化计数器,可以方便的和外部同步;

4是比较器,用于产生PWM波,每个子模块有6个比较寄存器,可以产生三路的PWM。

5和7是重装载选择器,可以用来选择重装载寄存器和N个PWM周期或者半周期重装载。

6是输出控制模块,比较器产生的PWM23与PWM45经过这些控制模块转变成PWM_A和PWM_B。主要包含互补控制,死区补偿,故障保护等功能。

多级串联PWM的实现

每个eFlexPWM子模块有一个外部同步信号输入,和两个触发信号输出。外部同步输入信号允许外部的信号源来初始化PWM计数器。通过这种方式,eFlexPWM子模块的行为可以与外部电路同步。

两个触发信号输出可以去控制其他模块的行为,例如在特定的时刻触发ADC采样。

本文将使用输出触发信号去触发其他eFlexPWM子模块。

两个输出触发信号分别由不同的寄存器值比较产生。当PWM计数器匹配val0、val2或val4时,TRIG0被置位。当PWM计数器匹配val1、val3或val5时,TRIG1被置位。计数器发生匹配事件后延迟两个clock的后输出触发信号。

图2 PWM子模块外部同步输入和Trig输出

在一些电源应用中,需要多路PWM输出,并且需要彼此之间有固定相移,此时就能充分凸显i.MX RT系列eFlexPWM强大的性能。

下面我们通过输出六路互补且彼此之间相差60°相移的PWM为实例,详述eFlexPWM使用方法和配置。

实例要求

下面以一个具体实例来介绍,方便读者理解和运用eFlexPWM模块。

具体的实例要求如下:

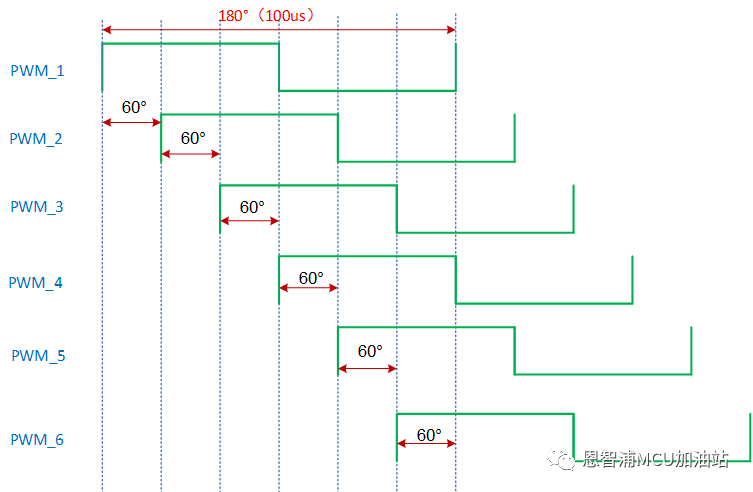

PWM频率为10KHz

六路互补PWM输出

两路之间移相60°

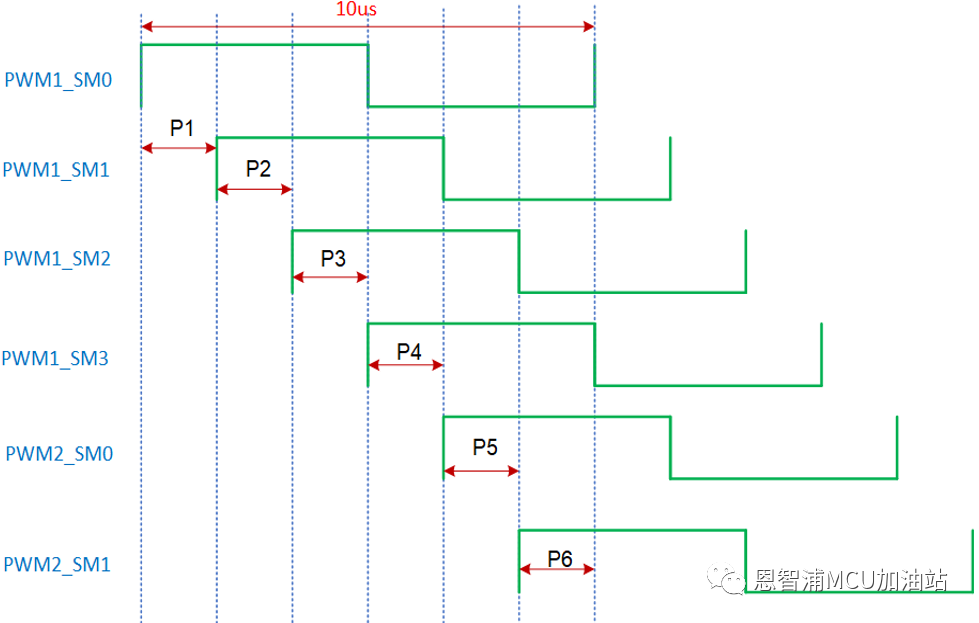

6路PWM输出的逻辑如下图所示:

图3 6路PWM相移图

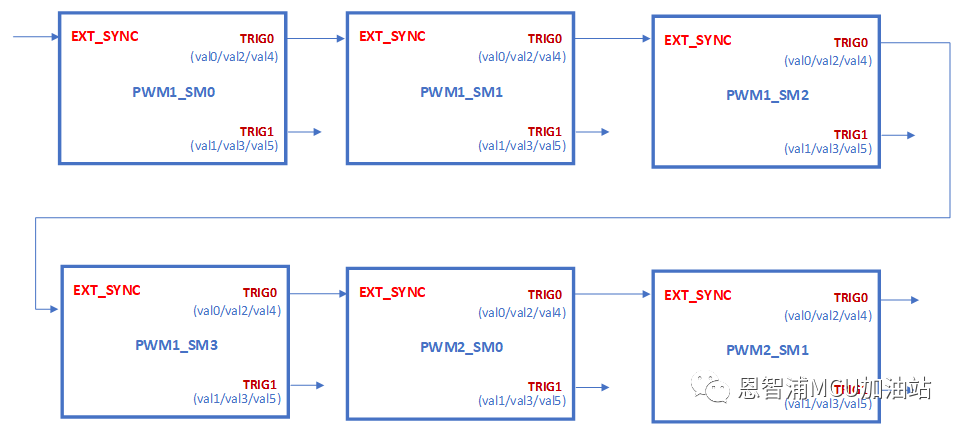

eFlexPWM子模块组合

用6个eFlexPWM子模块级联,每个子模块输出一路互补的PWM,因为每个eFlexPWM子模块都有一个独立的计数器,因此实现起来比较方便。

图4 eFlexPWM子模块串联

图4 eFlexPWM子模块串联

通过每个前级子模块的TRIG0去触发后级子模块,我们通过设置前级子模块Val4的值来灵活的设定触发后级子模块的时刻。

经过这样的组合,可以进行0-360°任意相位的相移,读者可以很方便的调节成自己想要的相移。不需要复杂的软件操作,通过寄存器可以方便实现,减小了CPU的开销。

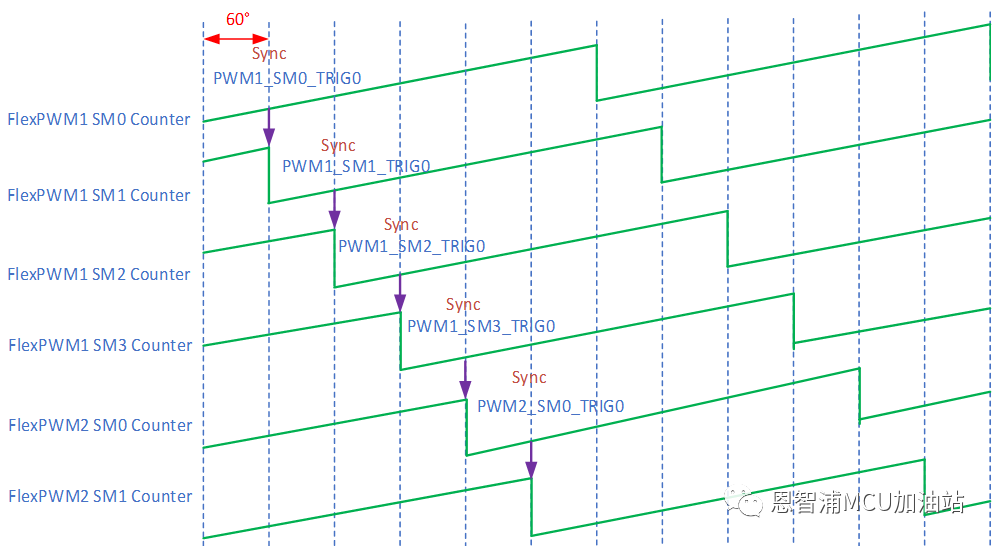

时序逻辑

图5给出了载波移相的逻辑,从图中我们可以看到六路PWM载波信号依次移相60°,后级子模块由前级子模块在特定时刻触发。通过载波的移动,载波和比较器比较后产生的PWM也就产生了相应的相移。  图5 时序逻辑

图5 时序逻辑

从图5中可以看出每个后级子模块都由前级的TRIG0触发产生的,只要设定好触发时刻,就可以得到所预想的相移。

后级子模块检测到前级子模块的TRIG0触发信号后,会用两个clock时钟去同步。再加上TRIG0输出前有两个clock的延迟,所以总共会有4个clock的延迟,后面实验结果可以验证。

测试结果

考虑到前级触发后级的延迟,本文进行了实际测量和分析,如图6所示测量两相之间的时间间隔。

图6 PWM 相移间隔图

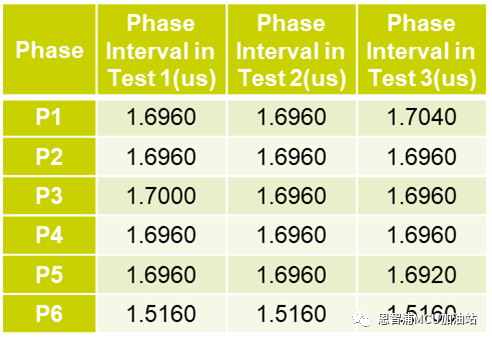

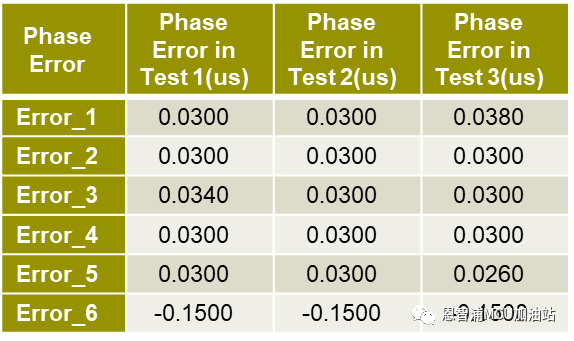

测量三次P1-P6的相位偏移时间,结果如下:

表1 P1-P6的相位偏移时间

因为本实例中PWM频率是10Hz,所以P1-P6的理论间隔时间是16.667us(60°)。下表给出了实测和理论值的误差。

表2 P1-P6的相位误差

从测试结果我们可以看出,实测结果后级子模块比理论有了30ns的延迟。这样从初级子模块,到最后级子模块,误差不断积累,最后会导致最后级子模块有150ns的延迟。如果级数更多,则误差会更大。

因此我们需要一些方法进行补偿。

延迟补偿方案

因为每个后级子模块的延迟都是固定的,所以我们可以通过把触发时刻前移固定时长的方法补偿此延迟。

根据PWM clock频率和延迟时间我们可以计算出需要补偿的计数值。

counter=delay_Time*PWM_Clock

本实例中PWM clock的频率是132M,延迟是30ns,从而计算出需要补偿的数值约等于4。

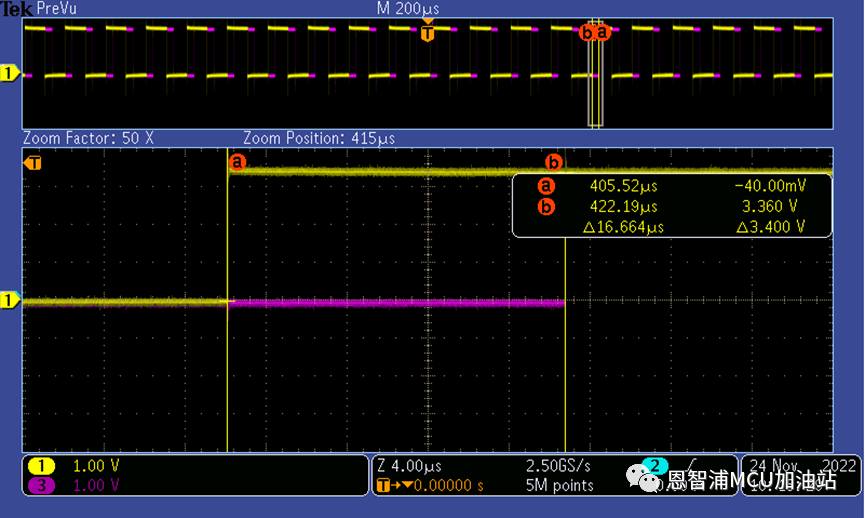

在程序中补偿后,测量两相波形相移如下图所示:

图6 补偿后的PWM移相图

从图中可以看出两相移相时间是16.664和理论值非常接近,考虑到测量误差,已经基本达到设置的目标。这样就完美的解决了延迟的问题。从而就实现了多级串联载波移相的PWM输出。

-

正弦脉宽调制原理是怎样的 正弦脉宽调制控制的方法有哪些2024-02-06 3765

-

SPWM正弦脉宽调制介绍2021-11-15 2387

-

浅析正弦脉宽调制技术SPWM2021-09-03 1330

-

DSP载波移相控制C语言源代码下载2021-05-12 1989

-

脉宽调制(PWM)技术2020-05-24 2922

-

空间矢量脉宽调制技术2018-10-29 1754

-

PWM再生成电路的组成与高精度脉宽调制信号移相电路的设计2017-11-06 1349

-

采用载波移相技术永磁电机高频振动抑制研究_袁飞雄2017-01-07 1007

-

移相键控(PSK/DPSK)调制与解调实验2016-01-05 5256

-

载波移相多电平SPWM研究2012-03-07 10615

-

二相相对移相调制(2DPSK)原理是什么?2010-03-18 27015

-

PWM脉宽调制技术2008-08-27 18563

全部0条评论

快来发表一下你的评论吧 !