单芯片直接数字频率合成与模拟PLL的比较

描述

作者:Jim Surber and Leo McHugh

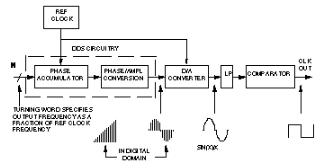

新的集成完整DDS产品为敏捷频率合成应用提供了一种有吸引力的模拟PLL替代方案。长期以来,直接数字频率合成 (DDS) 一直被认为是生成高精度、频率捷变(宽范围内可快速变化的频率)、低失真输出波形的卓越技术。DDS架构(图1)采用精密相位累加器和数字信号处理技术来生成数字正弦波表示,该表示以高度稳定的参考时钟为参考。然后将数字正弦波数据施加到高速数模转换器(DAC),以产生相应的模拟正弦波输出信号。

图1.基本完整DDS系统框图。

DDS系统的一个主要优点是,可以在数字处理器控制下精确快速地控制其输出频率和相位。其他固有的DDS属性包括能够以极精细的频率和相位分辨率进行调谐(频率控制在毫赫兹(mHz)范围内,相位控制<0.09°,以及频率快速“跳跃”(每秒高达2300万次输出频率变化)。这些特性相结合,使该技术在军用雷达和通信系统中非常受欢迎。事实上,DDS技术以前几乎完全被降级为高端和军事应用:它成本高,耗电大(以瓦特为单位的耗散),难以实现,需要分立的高速信号DAC,并且有一组用户不利的系统接口要求。

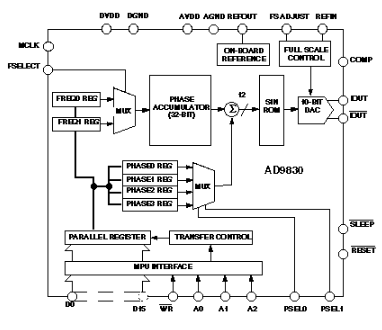

图2.AD9830 50 MHz C-DDS的框图

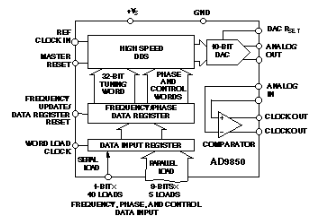

ADI公司推出的全新突破性CMOS数字频率合成器产品系列提高了基于DDS的频率合成器解决方案的吸引力。AD9850、AD9830125MHz和50 MHz完整DDS(CDDS)器件包括片内10位信号DAC(图2和图3)。它们针对低输出失真进行了优化,具有 72 dBc 窄带的无杂散动态范围 (SFDR) 和高达 54 dBC 的宽带 @ 40 MHz。 其他产品特性,如小型表面贴装封装、极低的功耗(+3.3 V时低至155 mW)、增强的功能和低廉的价格,共同确保这些器件确实是DDS技术的最新技术。它们现在允许用户处理成本敏感型、大批量、消费类合成器应用;它们为基于模拟的锁相环(PLL)技术提供了一种可行的替代方案,用于生成敏捷的模拟输出频率。

AD98x0器件对于本振(LO)和上/下变频级应该具有独特的吸引力,而这些器件迄今为止一直是基于PLL的模拟频率合成器的专属领域。出于多种原因,AD98x0器件的完整DDS架构与等效的基于PLL的敏捷模拟频率合成器相比具有明显的优势。例如:

输出频率分辨率:AD98x0 C-DDS产品具有32位相位累加器,可实现比基于PLL的频率合成器更精细的输出频率调谐分辨率。AD9850的可调输出分辨率为0.06 Hz,时钟频率为125 MHz;AD9830的调谐分辨率为0.012 Hz,参考时钟为50 MHz。此外,这些器件的输出在过渡到新频率期间是相位连续的。相比之下,基于 PLL 的基本模拟频率合成器的输出调谐分辨率通常为 1 kHerz;它缺乏数字信号处理提供的固有分辨率。

输出电压开关时间:模拟PLL频率开关时间是其反馈环路建立时间和VCO响应时间的函数,通常>1 ms。基于 C-DDS 的频率合成器切换时间仅受 DDS 数字处理延迟限制;AD9850的最小输出频率开关时间为43 ns。

调谐范围: 关键反馈环路带宽和输入参考频率关系决定了典型模拟PLL电路的稳定(可用)频率范围。基于 C-DDS 的频率合成器不受此类环路滤波器稳定性问题的影响,并且在整个奈奎斯特范围(<时钟速率的 1/2)内可调谐。

相位噪声: 由于分频,基于C-DDS的解决方案在输出相位噪声方面比模拟PLL频率合成器具有明显的优势。C-DDS频率合成器的输出相位噪声实际上优于其参考时钟源,而基于模拟PLL的频率合成器的缺点是实际上会增加其参考频率中的相位噪声。

电路板空间要求: 高度集成的AD98x0 C-DDS器件采用非常小的表面贴装封装,与大多数高质量等效带宽分立PLL频率合成器方案相比,不需要更多的电路板空间。

成本: 打破现有的DDS价格障碍,基于C-DDS的解决方案在大批量应用中具有竞争力,具有带宽等效的基于PLL的分立式频率合成器解决方案。

功耗: C-DDS频率合成器的功耗比早期的分立DDS解决方案低得多。例如,AD9850在3.3 V时,采用100 MHz参考时钟产生40 MHz信号时功耗为155 mW。这与同类分立式模拟PLL电路相比具有竞争力。

实施复杂性: 完整的DDS解决方案,包括信号DAC,意味着系统设计变得容易。不再需要实现DDS解决方案所需的RF设计专业知识;困难的部分已经完成。用于控制的简单数字指令集可最大程度地降低支持硬件的复杂性。数字系统设计取代了基于PLL的模拟频率合成器解决方案所需的模拟密集型系统设计,以解决类似问题。

图3.AD9850 125 MHz C-DDS框图

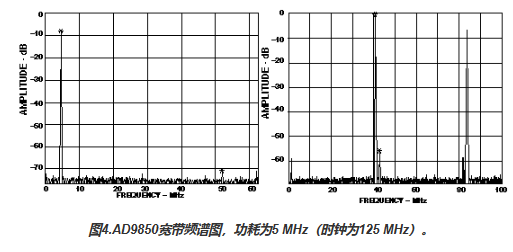

交流性能是选择频率合成器时的一个重要考虑因素。C-DDS频率合成器系统的失真性能受其信号DAC的限制;AD98x0器件在CMOS DAC性能方面树立了新的基准。其板载 10 位 DAC 内核针对宽输出带宽上的高 SFDR 进行了深入优化,本身就是技术突破(请参阅本期第 7-9 页)。图4和图5显示了AD9850输出的宽带频谱图,该输出频率采用125 MHz参考时钟产生5 MHz和40 MHz输出频率。在62.5 MHz奈奎斯特带宽(参考时钟速率的1/2)下,AD9850输出的SFDR分别为62.8 dB和55.2 dB。这种动态性能以前只能通过耗散几瓦的昂贵双极性DAC来实现。

图4.AD9850宽带频谱图,功耗为5 MHz(时钟为125 MHz)。

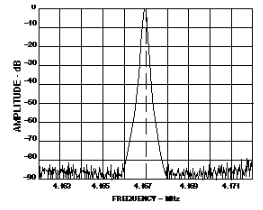

在其他应用中,其中许多应用以基于模拟PLL的频率合成器解决方案为主,窄带性能是一个重要的考虑因素。在窄带应用中,C-DDS频率合成器输出的杂散性能在很大程度上取决于DDS的数字截断电平,而不是DAC的性能。图6显示了AD9830在4.16 MHz A时的窄带图外和一个 50 MHz 时钟。SFDR在基波的±5 kHz窗口内大于79 dB。

图6.AD9830窄带频谱图4.1 MHz Aout(50 MHz时钟)。

AD9850和AD9830均采用非常简单的负载方案,以实现用户友好的操作。它们只需要一个数据时钟和数据/地址总线来控制输出频率和相位,并启用休眠模式。除了输出滤波的特定要求外,不需要模拟密集型系统设计。AD9850还有一个有用的附加特性:集成高速比较器。DAC的滤波输出可施加到该比较器,以产生方波输出而不是正弦波,从而便于将该器件用作频率捷变时钟发生器。两款器件均提供PC兼容评估板,便于对合成系统进行台架测试。

快速输出跳频、数字控制、低输出失真和高调谐分辨率的组合使 Complete-DDS 解决方案成为模拟 PLL 频率合成器的可行替代方案。AD9830和AD9850在CMOS DAC和DDS技术方面的突破值得认真考虑任何频率合成器要求。

是呢环保局:郭婷

-

直接数字频率合成(DDS)技术的原理及优势2024-05-23 6954

-

直接数字频率合成信号发生器的设计2023-10-30 598

-

ADI直接数字频率合成器(DDS)2022-11-14 1801

-

直接数字频率合成技术(DDS+PLL)2021-06-07 1142

-

怎么设计直接数字频率合成器?2019-08-21 1677

-

直接数字频率合成技术的频率研究2019-07-10 5137

-

数字频率合成芯片AD9837的性能及应用分析2019-07-04 8379

-

基于单片机的直接数字频率合成详解2018-04-28 4143

-

直接数字频率合成技术DDS原理2015-10-30 1105

-

FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化...2012-08-11 10193

-

放大直接数字频率合成的DAC选型器应用2011-04-06 998

-

基于FPGA的直接数字频率合成器的设计2010-08-09 554

-

基于SystemView的数字频率合成器的设计2010-07-09 2746

-

基于FPGA的直接数字频率合成器的设计和实现2009-06-20 840

全部0条评论

快来发表一下你的评论吧 !