了解放大器噪声如何影响ADC信号链中的总噪声

描述

模数转换器(ADC)在模拟输入驱动至额定满量程输入电压时提供最佳性能,但在许多应用中,最大可用信号与指定电压不同,可能需要进行调整。满足这一要求的有用器件是可变增益放大器(VGA)。了解VGA如何影响ADC的性能将有助于优化整个信号链的性能。

本文分析使用双通道16位、125/105/80 MSPS流水线ADC和超低失真IF VGAAD8375的电路中的噪声。信号链包括一个增益设置为+6 dB的VGA、一个在100 MHz时滚降为–3 dB的五阶巴特沃兹低通滤波器和ADC。将显示放大器和滤波器的噪声计算,因为它们决定了ADC在目标频带上的动态性能。

问题

许多使用高速ADC的实际应用都需要某种驱动器、放大器或增益模块,将输入信号缩放到满量程模拟输入范围。1以确保最佳的信噪比 (SNR) 和无杂散动态范围 (SFDR)。此外,差分放大器还可以将单端信号转换为差分信号以驱动ADC。当处于活动状态时,这些元件会在ADC前端产生噪声。在工作带宽上积分这种噪声会降低转换性能。

为应用选择合适的ADC取决于许多因素,包括:

模拟输入范围

输入频率/带宽

所需分辨率/信噪比

所需的 SFDR

某些应用需要高动态范围和高分辨率。AD9268是这些应用的理想选择,在70 MHz中频下提供78.2 dBFS(相对于满量程的dB)SNR和88 dBc SFDR。

在系统层面,ADC前端可以使用放大器、变压器或巴伦,但使用放大器的实现最为常见。放大器可用于以下一个或多个原因:

为输入信号提供增益以提高ADC分辨率。

缓冲或变换输入源和ADC之间的阻抗。

将单端输入信号转换为差分输出信号。

AD8375 VGA可在各种增益设置下保持高线性度和均匀噪声性能,可用于将单端信号转换为差分信号。这些特性使其成为以较高中频驱动ADC的良好候选者。遗憾的是,信号链中存在有源器件(放大器)会限制ADC的性能。

例

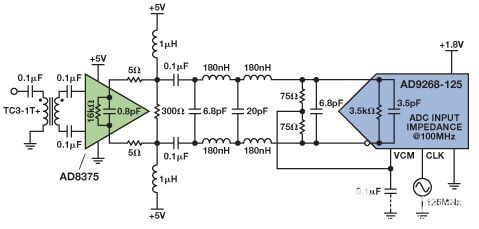

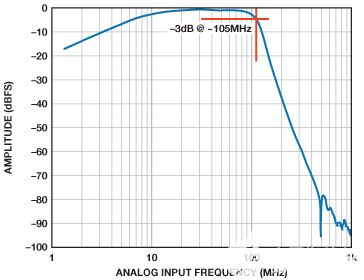

图1显示了用于执行噪声计算的电路拓扑。AD8375具有高阻抗差分输出(16 kΩ||0.8 pF)。具有100 MHz带宽和150 Ω输入和输出阻抗的五阶低通抗混叠滤波器(AAF)将放大器连接到ADC。图1所示电路的频率响应如图2所示。

图1.AD8375、AAF和AD9268信号链。

图2.AD8375、AAF和AD9268信号链的频率响应。

性能

系统设计人员可能不希望驱动ADC输入的放大器会降低系统的整体动态性能,但为一种应用选择驱动器和ADC组合并不意味着它将在另一种应用中提供相同的出色性能。此处描述的技术允许系统工程师在选择放大器之前估计预期性能。

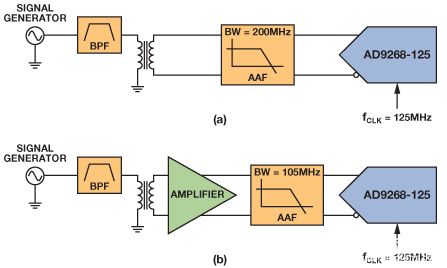

图3显示了两种不同的设置: 图3(a)使用无源耦合到转换器,可作为客户评估板上的默认选项。无源前端网络使用变压器或巴伦将单端信号转换为差分信号,以及一个在大约200 MHz时滚降的无源低通滤波器。 图3(b)显示了可选的放大器路径。下面比较了这两种设置产生的噪声。使用低中频(10 MHz)的单音快速傅里叶变换(FFT)来计算放大器增加的噪声。

图3.典型的ADC前端:(a)无源。(b) 主动。

分析噪声通常使用两种技术,但每种技术都可能很麻烦。噪声频谱密度(NSD)定义了每单位带宽的噪声功率。ADC的均方dBm/Hz或dBFS/Hz表示,放大器的均方根nV/√Hz表示。这种单位不兼容为放大器驱动ADC时计算系统噪声提供了障碍。

噪声系数(NF)是输入SNR与输出SNR的对数比,以分贝表示。RF工程师常用的这种规范在纯RF世界中是有意义的,但试图在带有ADC的信号链中使用NF计算可能会导致误导性结果。2

另一种但更有效的技术是“去规范化”噪声密度,将其表示为均方根噪声电压而不是均方电压。这种方法(如此处所述)非常简单,可以清楚地分析系统噪声。

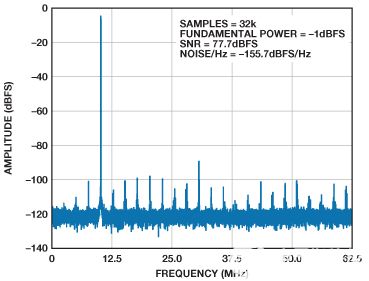

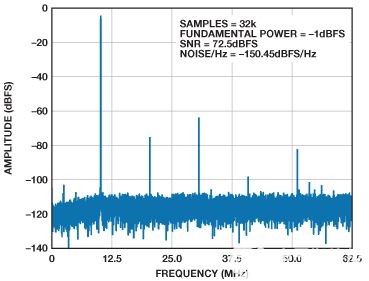

图4和图5显示了两个前端的低频单音FFT。请注意,无源前端的信噪比为77.7 dBFS SNR,而有源前端的信噪比为72.5 dBFS,比ADC的预期性能低5.2 dBFS。

图4.图3a电路的10 MHz模拟输入音的FFT。

图5.图3b电路的10 MHz模拟输入音的FFT。

分析

图3a和3b所示设置之间的唯一区别是在信号链中增加了放大器,因此可以安全地假设性能下降是由放大器的噪声引起的。以下计算有助于了解放大器引入的额外噪声。

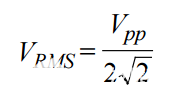

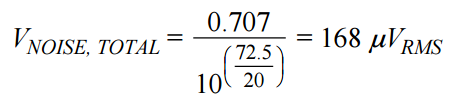

首先,使用数据手册中规定的转换器满量程差分输入电压。将峰峰值电压转换为均方根,除以2√2得到0.707 V rms。

|

(1) |

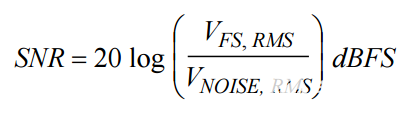

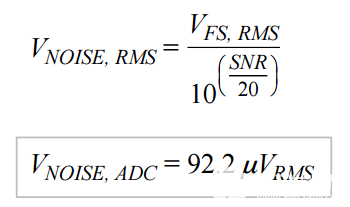

基于ADC在10 MHz时的典型SNR,转换器噪声的贡献为

| (2) |

| (3) |

使用 V噪声,模数转换器= 92.2 μV rms和系统SNR 放大器前端= 72.5 dBFS,使用公式3时,系统噪声为168 μV rms。

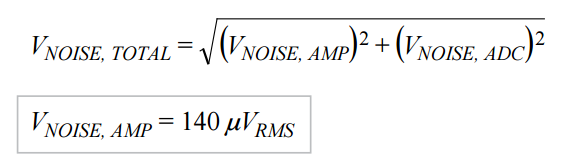

| (4) |

| (5) |

从公式4得到的系统噪声是ADC和VGA的组合噪声。放大器噪声可通过公式5计算为140 μV rms。该计算表明,放大器噪声至少比ADC噪声高50%,使其成为决定系统交流性能的限制因素。

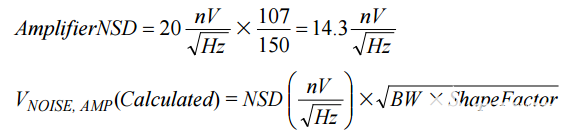

注意,我们必须确定V的值是否噪音,放大器以上计算结果与放大器的数据手册相符。额定噪声频谱密度约为20 nV/√Hz,差分输出阻抗为150 Ω。

虽然数据手册规定VGA的噪声随增益而相当恒定,但该噪声会随负载而变化,因此噪声频谱密度应与放大器输出驱动的总阻抗成比例。因为放大器的差分输出阻抗很大(16 kΩ||0.8 pF),放大器看到的阻抗(见图1)可以计算为

[10 Ω + (300 Ω||150 Ω||3.5 kΩ)] = 107 Ω。

使用此数字,本应用中AD8375的降额噪声频谱密度可从公式6中找到:

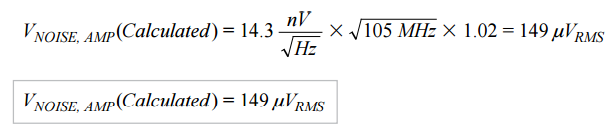

| (6) |

请注意,使用实际滤波器计算系统噪声时,噪声带宽的形状与理想滤波器的形状不同。频率响应的这种偏差由项、形状因子表征,并考虑了滚降区域的噪声。形状因子取决于滤波器的阶数,是噪声带宽与–3 dB带宽之比。3滤波器中的极点越多,形状因子就越接近统一。这种关系可以在表 1 中看到。

表 1.系统阶数与形状因子的关系

| 系统顺序 | 形状因子 |

| 1 |

1.57 |

| 2 | 1.11 |

| 3 | 1.05 |

| 4 | 1.03 |

| 5 | 1.02 |

在图 1 的示例中,形状因子为 1.02。使用公式6,放大器注入的噪声为;

VGA注入系统的估计噪声值与使用公式5的测量值非常吻合,证明由AD8375和AD9268组成的信号链的性能由放大器主导。

结论

在许多情况下,需要使用放大器(VGA或增益模块)将满量程信号驱动至系统信号链中的ADC。系统设计人员必须意识到ADC最佳性能下降是由放大器的选择引起的。在使用所选放大器和ADC进行设计之前,设计人员可以使用此处所示的方法计算放大器的噪声贡献,以估计预期系统实现的预期动态性能(如SNR特征)。

审核编辑:郭婷

-

了解音频电路中的运算放大器噪声2024-09-10 586

-

如何在PCB设计中克服放大器的噪声干扰?2023-11-09 1513

-

如何降低放大器噪声?2023-09-19 2851

-

信号放大器还是噪声放大器?2023-02-28 1977

-

信号链中放大器噪声对总噪声有多少贡献?2021-04-07 1633

-

了解锁相放大器的类型和相关的噪声源2020-09-18 3968

-

如何计算仪表放大器电路的总噪声2019-07-01 5491

-

如何计算ADC与放大器的组成系统中的的总噪声2019-04-12 3157

-

【转帖】正确选择低噪声放大器2018-12-19 3843

-

简述激励放大器与 ADC 之间的噪声规格关系2018-11-29 2947

-

ADC信号链中放大器噪声对总噪声有什么贡献2018-10-23 2829

-

激励放大器与ADC之间的噪声规格关系2018-07-03 8191

-

为精密 ADC 寻找合适的低噪声放大器2018-05-17 3615

-

了解ADC信号链中放大器噪声对总噪声的贡献2016-01-07 848

全部0条评论

快来发表一下你的评论吧 !