什么是寄存器

电子说

描述

有一个很无语的问题,什么是register?天天在配寄存器,但是不知道寄存器是什么。寄存器的地址偏移有的是1,有的是4。这个偏移量为什么偏移不是3?偏移量和register的data位数有没有关系

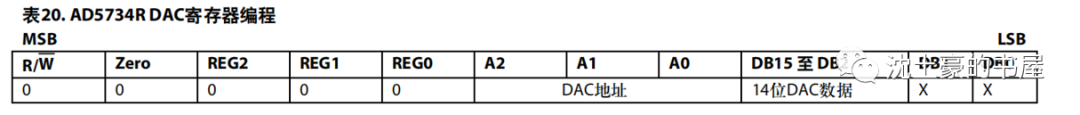

基本随便打开一份数字IC的数据手册我们就会得到designer提供的register table。

比如一颗DAC,通过SPI接口,配置电压寄存器。

24bit的register,A2:A0 选择DAC地址,DB15:DB2设置DAC输出电压。

给自己的一点理解:

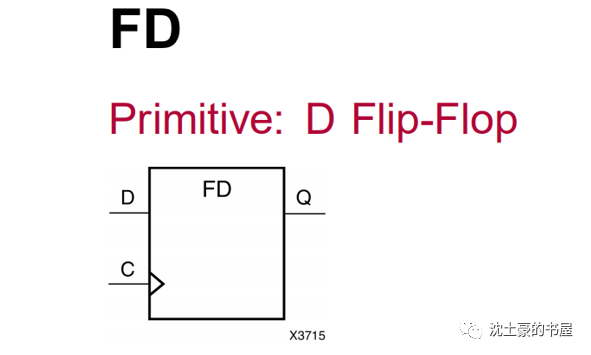

所有register,如果是接入clk的,xilinx称为原语D flip-flop,就是大学本科的教材,D触发器。

有32 bit的 register,就是32个DFF。DFF值从哪里来的?就是RTL级code的数百个module/IP里面input,output,reg信号。

这些信号拉到哪里去?拉到reg access的module,这个reg access的module就是通过填表,通过脚本gen出来的电路。

这个module port数非常大,大到只要register table里的有的信号,就会从其他各个模块电路拉进来,input output信号极其多。

这份文档有描述FPGA/ASIC状态寄存器和控制寄存器的做法:

csrGen: Automated CSRs for ASIC/FPGA Processor Interfaces .pdf

control/status registers (CSRs),的意思IC内部的控制寄存器和状态寄存器。

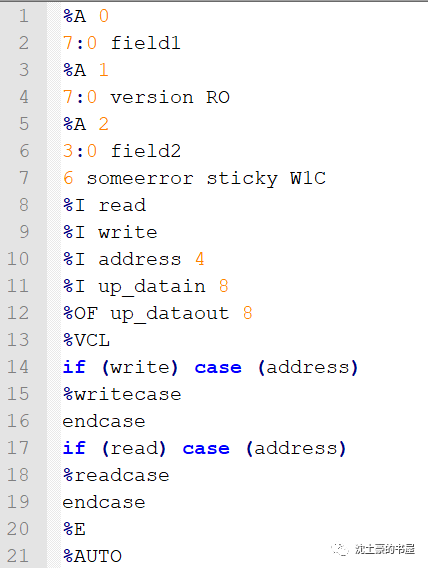

文档大概的意思是说是用csrGen写的一个脚本一样的code,用户可以通过填写register table,最后可以综合生成verilog register RTL code。

填表

用户填表:

大概的意思是:

第一行就是定义:A就是register的地址address缩写, 为0x0,共8bit,名字field1

第三行就是定义:A就是register的地址address缩写, 为0x1,共8bit,名字version,类型是RO

后面还有一些W1C,wite 1 clear register value,这种太难了我也看不懂怎么实现的。我们就看一个register读的,和写的。

后面通过它写的CSRGen,可以gen出一份RTL code。

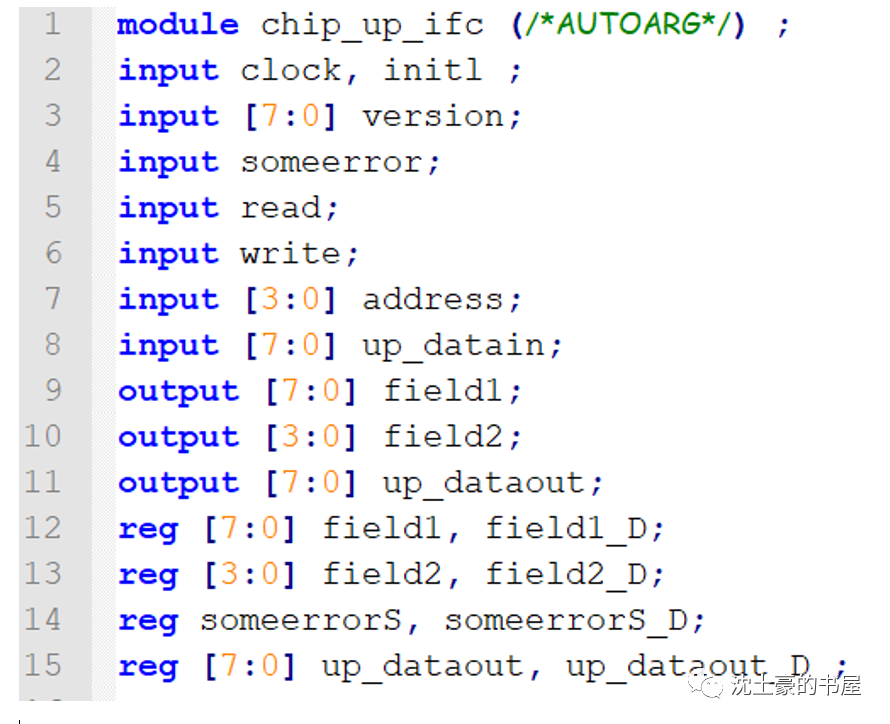

我们来看一下上面csrGen出来的RTL code。

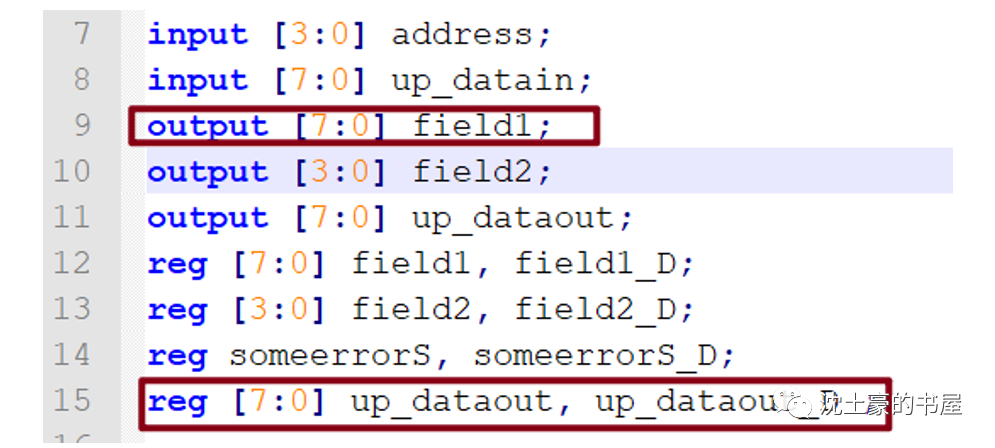

RTL级code定义了一个module,可以看到实际上对于读写指令,实际上就是1bit控制信号read/write,传入的address[3:0],和up_datain[7:0]。

同时可以看到刚才看到RO类型的寄存器8bit version,实际上是从其他IP拉过来的,可以认为IC内部有很多个module/IP,这个viersion[7:0]就是从其他IP拉给chip_up_ifc 模块的。

Read

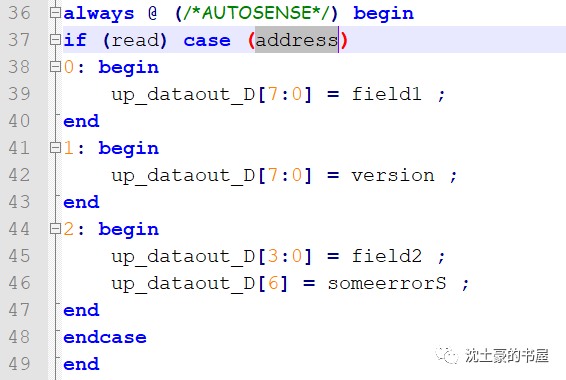

当我们去读写reg的时候,实际上就传入read的命令和address。

RTL怎么实现的呢?就是通过在chip_up_ifc,在敏感列表响应到read == 1’b1,采样address值,通过case匹配,把需要RW的register地址,赋值到用户的读写reg的接口上,即up_dataout_D[7:0] = version ;

version是其他module拉线来的,对于这个chip_up_ifc来说是input信号,up_dataout_D[7:0]是chip_up_ifc输出的。

Write

当我们去写reg的时候,实际上就传入write的命令和address和data值。

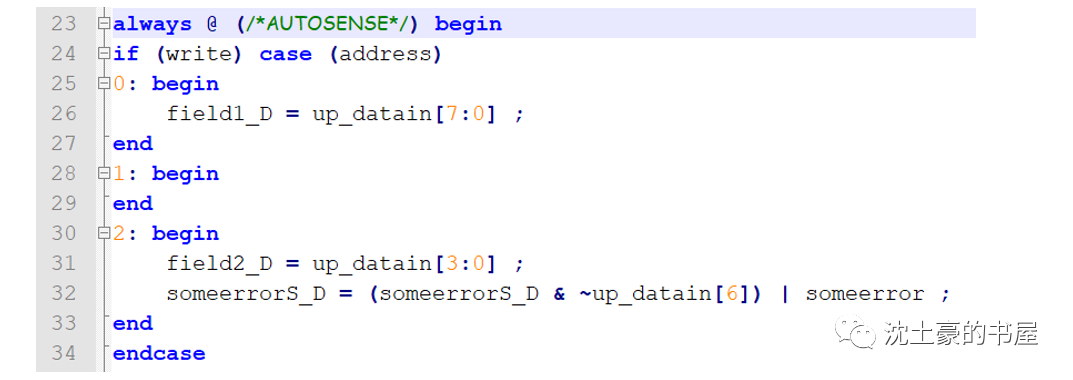

RTL级code如下,当always块敏感列表有write指令的时候,

看到case敏感列表里面是address,这里IC内部排布的reg地址是从0 1 2 3 4….

当对address 0,写的时候,就把用户想要写入的数据up_datain[7:0],赋值给address 为0的field1_D。

我们刚才填写的register profile就是

%A 0

7:0 field1

这里是对field1_D赋值而不是field1的原因是,在内部生成了2个reg。一个是field1,field1_D。以我几个礼拜的RTL coding基础,猜测是防止直接操作field1影响它原本所在的电路,通过下一个clk信号,

才把field1 <= field1_D,打了一拍。

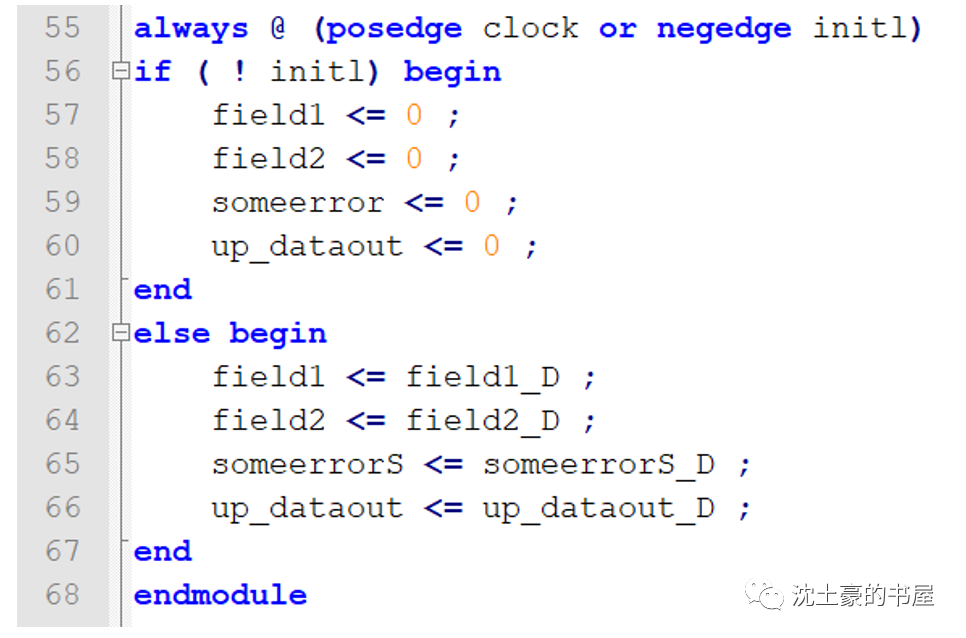

RTL在下面63行也有体现。register的初值怎么做到的,也在always块的init1下降沿触发赋值有体现。

所以就有了以下结论,

Q:IC内部的寄存器偏移地址一定是1或4,有什么含义吗?

A:没有任何意义。这边address,在always块每次匹配的是多少就是访问的哪个reg,它可以偏移1,偏移100,1000都可以,甚至排布可以是1 3 5 7 9;

A:每个address获得的reg数据位宽和偏移有关系吗?

Q:也没有,想定义每个address的reg的位宽是13个bit都可以,并不是8 /16/32 bit。RTL决定了本质是多少个DFF。在clock节拍下寄存下别的module拉过来的信号值。但是多少考虑到数据位宽,也要定义成8/16/32吧。

A:上面结论是不是都对的?

Q:不一定,都是我猜的,其实我是做硬件的不太懂FPGA,有幸在南邮读书期间和FPGA coder联调过小半年。这边我猜测:软件跑在SOC,SOC有些reg地址,好像就是access sram,sram有大小的,8k的sram就被分成了那么多地址。软件那边定义的应该有关联的吧?RTL实现的reg是无关联的。

-

寄存器分为基本寄存器和什么两种2024-07-12 3330

-

CPSR寄存器和APSR寄存器的组成2023-10-20 7098

-

寄存器是什么?怎么操作寄存器点亮LED灯?2023-07-21 5532

-

单片机工作寄存器作用 单片机常用专用寄存器2023-04-08 10117

-

ARM通用寄存器及状态寄存器详解2023-01-06 10047

-

GPIO寄存器2021-12-08 1435

-

AD转换寄存器设置2020-11-10 1261

-

移位寄存器的原理2019-07-15 77631

-

寄存器变量2019-06-03 3036

-

移位寄存器怎么用_如何使用移位寄存器_移位寄存器的用途2017-12-22 21318

-

寄存器与移位寄存器2010-03-12 1001

-

数据寄存器,数据寄存器是什么意思2010-03-08 13195

全部0条评论

快来发表一下你的评论吧 !