使用 ARC VPX DSP IP 以嵌入式方案的预算实现高性能传感器融合

嵌入式技术

描述

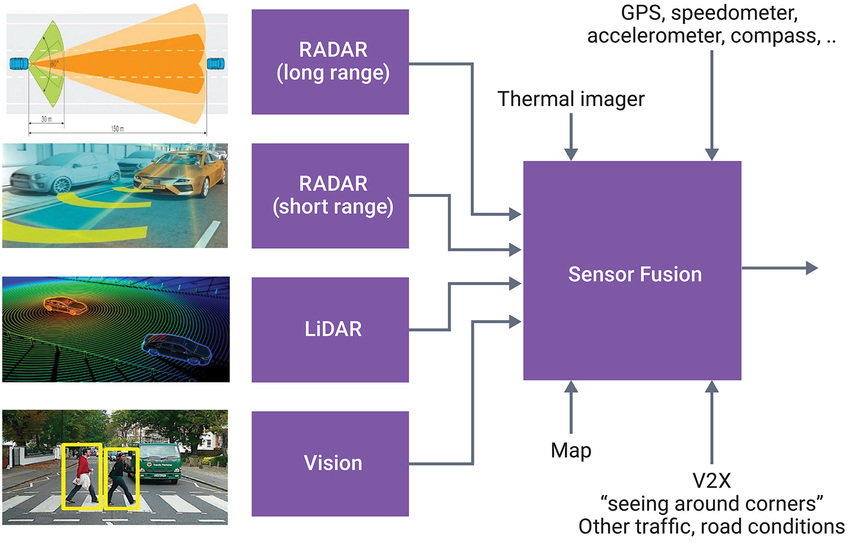

推动传感器融合需求的主要趋势

传感器融合是指组合来自多个传感器的数据,以获得更为完整和准确的结果。通过使用由多个传感器提供的信息,可以实现更好的环境感知。拿我们人类来说,我们可以通过组合各种“传感器”(眼睛、耳朵、鼻子、舌头、皮肤)中收集的信息,来了解周围的环境,从而决定如何应对各种情况。这就是一个典型的传感器融合示例。 传感器融合需要满足三个条件:小型化的传感器、从传感器产生的数据流中提取相关信息的复杂算法,以及在可用功耗和成本预算内提供执行算法所需性能的 SoC。 人类身体的每个“传感器”具有互补优势并提供独特的信息,嵌入式系统中的传感器也必须如此。以 ADAS 为例,雷达在不同光线和天气条件下性能稳健,LiDAR 可提供具有良好视角分辨率的广阔视野,而基于摄像头的视觉功能则可对物体实现快速准确的分类(图 1)。

图 1:ADAS 系统中的多个不同传感器

从传感器信号中提取有效信息,以及组合来自不同传感器流的信息,都需要用到算法。根据应用的不同,这些算法的复杂程度可能会有很大差异,性能要求也大不相同。比如在消费类应用中,只有检测到某个语音命令时,始终在线的智能家居设备才会醒来,但 ADAS 系统必须持续监控其环境。

复杂的算法需要能够提供执行算法所需性能的 SoC。当然,该SoC需要需要满足可用功耗和面积的限制,因为这将在很大程度上影响企业总体盈利能力。散热和有限的电池容量是两个主要驱动因素,具体情况视应用而定。理想情况下,这类 SoC 完全可编程,以实现最大的灵活性。算法在产品的生命周期内可能发生演进,传感器在其生命周期内可能需要不同的校准,而且非常希望在可通过软件进行区分的情况下,对产品的多个版本使用相同的 SoC。

传感器融合高效实现的关键特性

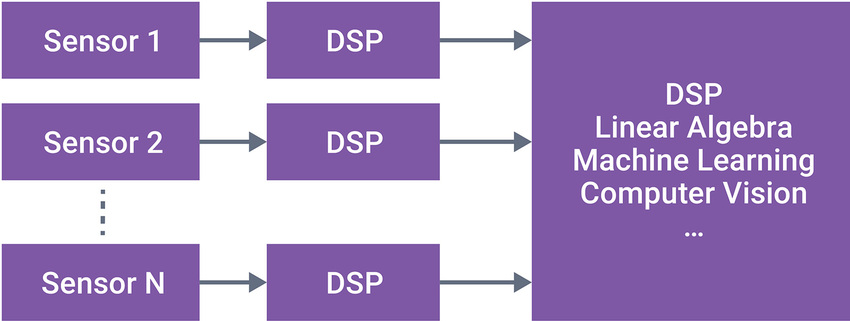

如前所述,传感器融合包含两个主要阶段:(1) 提取信息,(2) 结合信息以得出结果。这在图 2 中加以说明。

图 2:传感器融合处理链

第 1 阶段也可以称为传感器融合的前端。根据传感器和感兴趣的信息,应用不同的数字信号处理算法。对于语音,这可能是计算梅尔频率倒谱系数 (MFCC),应用傅里叶变换和其它各种 DSP 操作,从语音信号提取频谱特征。数据将以整数格式,很可能以 16 位表示。

对于摄像头,它是具有图像缩放、色彩空间转换、过滤或特征检测等功能的图像信号处理。此处数据表示为像素,数据格式为 8 比特,最多 16 比特。

最后,对于雷达,此类前端处理包括范围和速度 FFT ,以及用于阈值的恒定虚警率 (CFAR)。由于动态范围和精度要求,数据类型为半精度或全精度浮点。 第二阶段是信息结合(后端处理)。要使用的算法与应用息息相关。任务包括对象检测、识别、跟踪以及预测。可以应用基于 AI 的机器学习算法和线性代数操作。当然,数据类型将取决于算法。

由于这些特定但不同的要求,传感器融合需要一款满足下列关键要求的数字信号处理器 (DSP)。

多功能性

算法和数据类型在很大程度上取决于应用。因此,DSP 架构必须支持丰富的指令集,以便高效实现不同的算法,并特别关注 FFT 或线性代数等性能关键型操作。DSP 必须支持不同精度的整数和浮点数据类型。

这种 DSP 需要成为合格的灵活计算资源,这意味着它需要能够执行通常与 DSP 相关联的“经典”过滤操作,以及机器学习和计算机视觉算法。

可扩展性

为了避免一次性投资,可扩展性是关键。虽然对不同传感器的要求不同,但对于不同设计的所有信号处理要求,非常希望使用相同的基准架构,以降低系统集成工作,并最大限度地提高整体软件开发效率。可扩展性让设计师能够选择配置,从而为目标应用提供最佳 PPA。

可扩展性不仅仅关乎硬件。针对特定架构进行内核优化,是软件方面的一项重大投入。重要的是,此类软件可以在这些 SoC 上重复使用,从而能够重复使用不同版本的 SoC(例如低端/中端/高端版本)。

PPA 优化

就性能/功耗/面积(PPA)而言,有很多方面可进行优化。首先,性能关乎核心本身的循环效率(即执行特定功能所需的循环次数),以及可用的处理引擎和能够利用这些引擎的 ISA。这直接关系到对数据移动的有效支持,与数据处理并行,然后连接到一组丰富(最好是可配置的)接口。例如将加速器和外围设备直接连接到核心,而不通过系统存储器。

DSP 的最大时钟频率体现出另一方面的性能。它决定 DSP 可以提供多少功率(以每秒周期为单位),但也影响物理 SoC 设计中时序收敛所需的工作量。 低功耗与性能效率,以及仅在需要时唤醒某些内核的选项直接相关(如智能家居应用中所述:等待唤醒信息)。

最后,小面积对成本以及漏电有直接影响。

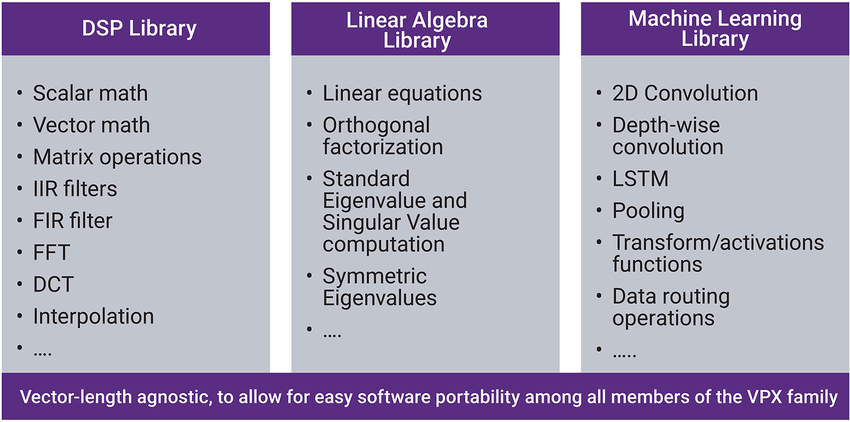

高效的软件开发

软件开发必须高效,因为对于几乎所有项目来说,大笔的投资(以及相关人员)都耗费在了软件开发和测试上。这需要一个具有优化编译器的高级编程模型,以及一组丰富的库,其中包含用于滤波、转换(例如 FFT)、矢量数学、线性代数和机器学习的现成优化内核。当然,还需要驱动程序、DMA 处理程序、中断处理程序等低级模块。

DesignWare® ARC® VPX DSP IP

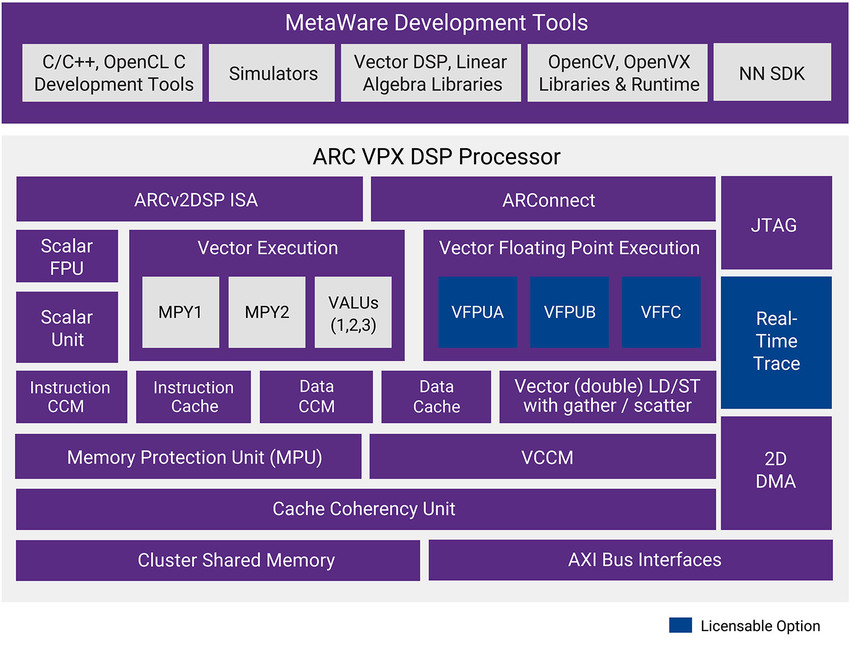

VPX DSP IP 是 VLIW/SIMD 处理器系列,适用于从常开设备到汽车 ADAS 再到视觉、机器学习和高性能计算等广泛的信号处理应用。图 3 提供了概述。

图 3:DesignWare ARC VPX DSP IP 块状图

VPX 系列非常适合传感器融合要求,因为它可提供可扩展性和多功能性,以实现最佳的 PPA 和软件开发效率,从而提高整体生产效率。

所有 VPX 系列产品均基于相同的 VLIW/SIMD 架构。客户可以根据自己的需求扩展解决方案,从 128 位到 512 位的不同矢量长度中进行选择。 除矢量长度外,客户可以从单核、双核或四核配置中进行选择,多核配置已预先集成并准备好用于缓存一致性和共享的多通道 DMA。

除了不同的矢量长度外,每个 VPX 内核都高度可配置,从而可定制架构以获得最佳性能,同时拥有最小的面积。

正如前文所解释,根据传感器和算法不同,需要不同的数据类型。VPX 支持的数据类型范围广泛,从浮点到覆盖应用(如高分辨率雷达)所需的动态范围,再到用于 AI 应用的小规模整数类型。 VPX 指令集架构 (ISA) 已调整为高效执行关键信号处理内核,例如 FFT 或矩阵操作。这避免了采用专用硬件加速器而带来的成本开支,从而实现了功率和面积的节省。

ISA 和微架构(即实施不同功能单元的方式)是实现最佳 PPA 的关键要素。但是,需要一个软件开发环境来释放硬件的功能。VPX 配有 MetaWare 工具套件,其包括优化 C/C++ 编译器、模拟工具和复杂的调试环境。为了支持对 AI 日益增长的需求,MetaWare 还提供 NN SDK 和先进的图形映射工具(支持 TensorFlow、Caffe、ONNX)。

图 4:随 MetaWare 一起提供的库,针对 VPX 进行了优化

VPX 系列包括为功能安全 (FuSa) 认证量身定制的 VPXxFS 变体(VPX2FS、VPX3FS 和 VPX5FS)。这些核心满足随机故障检测和系统功能安全开发流程要求,完全符合 ASIL D ISO 26262 合规性。VPXxFS DSP 集成了硬件安全功能,例如存储器和接口的 ECC 保护、安全监测器和锁步机制。一套全面的安全文档可帮助汽车设计师获得 ISO 26262 功能安全认证。此外,VPXxFS DSP 还提供“混合”选项,使用户可以选择更高ASIL D 的安全级别。

总结

传感器融合是一个快速增长的市场,已进入几乎所有应用领域。得益于低成本传感器的可用性,以及先进的算法,它可以在不同市场实现新的用户体验,包括智能移动设备、汽车、健康或工业控制。传感器融合导致不同的信号处理工作负载,因为不同的传感器需要不同的数据类型来表示数据,并且需要不同的 DSP 算法来提取与实际融合过程相关的信息。

融合过程(即组合各种传感器信息流并从中产生有意义的决策)在很大程度上是特定于应用程序的。要处理这些不同的工作负载,需要一个可扩展的处理器来处理不同的数据格式和性能要求,并且需要通用和可配置的架构,包括储存器和接口,以满足 PPA 要求。DesignWare ARC VPX IP 系列是传感器融合应用的理想解决方案:其矢量长度为 128 位、256 位或 512 位,可满足各种信号处理工作负载的需求。凭借定制的指令集和专用的数学硬件引擎,它可通过无与伦比的 PPA 提供卓越的循环效率。其可变矢量长度编程模型可确保软件可在 VPX 系列的所有产品之间重复使用。

- 相关推荐

- 热点推荐

-

基于dsp嵌入式uiptcp_ip协议栈的应用研究2023-09-25 748

-

使用 ARC VPX 嵌入式DSP IP实现高性能传感器融合2023-01-31 1450

-

怎么实现嵌入式WEB传感器的网络化接口设计?2021-06-04 1967

-

嵌入式和传感器如何融合起来2019-10-18 7313

-

高性能DSP如何抢攻嵌入式视觉市场?2019-09-04 2489

-

高性能惯性检测解决方案助力自主式机器应用2018-10-19 2241

-

如何轻松整合传感器到嵌入式系统2017-12-05 4235

-

高性能电容式指纹模块,支持嵌入式系统2017-03-21 3150

-

高性能6U VPX高速信号处理平台2016-03-02 2591

-

新思猛攻高阶嵌入式应用 ARC处理器新IP发功2013-11-21 2197

全部0条评论

快来发表一下你的评论吧 !