ADC建模工具可加快评估速度

描述

消费者对更快、更智能、更好产品的需求正在将创新推向前所未有的水平。因此,系统设计人员面临着一个共同的困境:在已知平台上设计新产品,只进行增量更改;或者使用具有最先进产品和功能的全新平台。前者可能快速且风险低,但回报较低;而后者提供更好的多功能性、功能和价值,但风险更高。

现在,一套新的仿真工具支持在软件中快速原型设计,最大限度地降低开发风险,并使设计人员相信他们的新产品将按预期工作。该软件提供了对模数转换器、时钟IC和放大器等单个产品功能的洞察,并且可以组合器件(例如ADC和时钟),而无需获取实际组件。购买硬件的决定可以在软件评估完成后做出,从而节省时间和金钱。

本文演示了ADIsimADC的多功能性,™ ADIsimCLK,™以及 VisualAnalog 软件套件,用于预测 ADC 与采样时钟结合使用时的性能。本示例使用16位、250 MSPS模数转换器AD9467和低抖动时钟发生器AD9523-1。第一部分介绍软件评估,仿真ADC随频率变化的性能,并展示如何在软件中连接器件。第二部分详细介绍了使用评估板和SPIController软件进行的实际硬件设置。本例为AD9467的时钟频率为245.76 MSPS。AD9523-1评估板使用交互式GUI配置时钟输出。

使用 ADIsimADC 和 ADIsimCLK 进行协同仿真

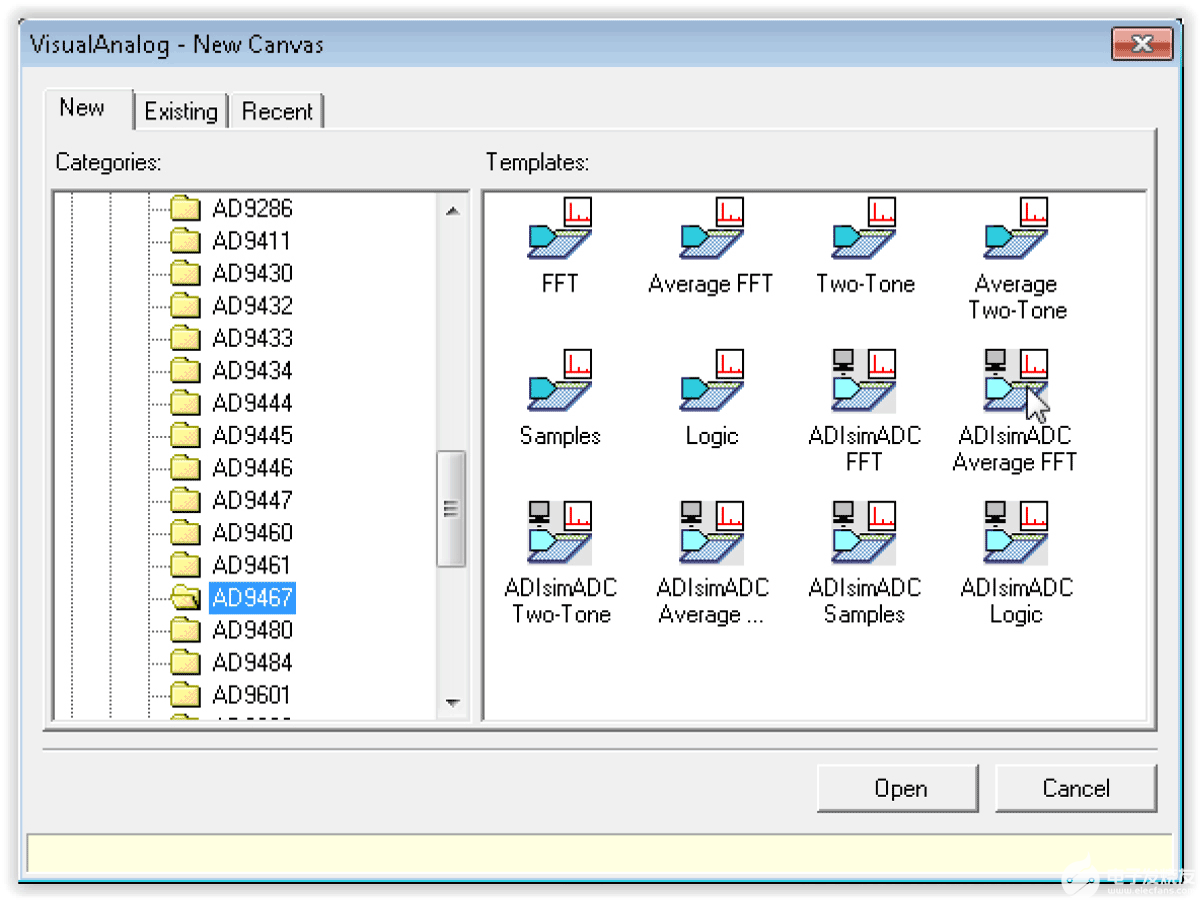

首先,下载并安装VisualAnalog和AD9523-1评估软件。ADIsimADC与VisualAnalog一起封装。启动 VisualAnalog 后,弹出窗口将要求用户选择一个 Canvas,如图 1 所示。

图1.视觉模拟新画布窗口。

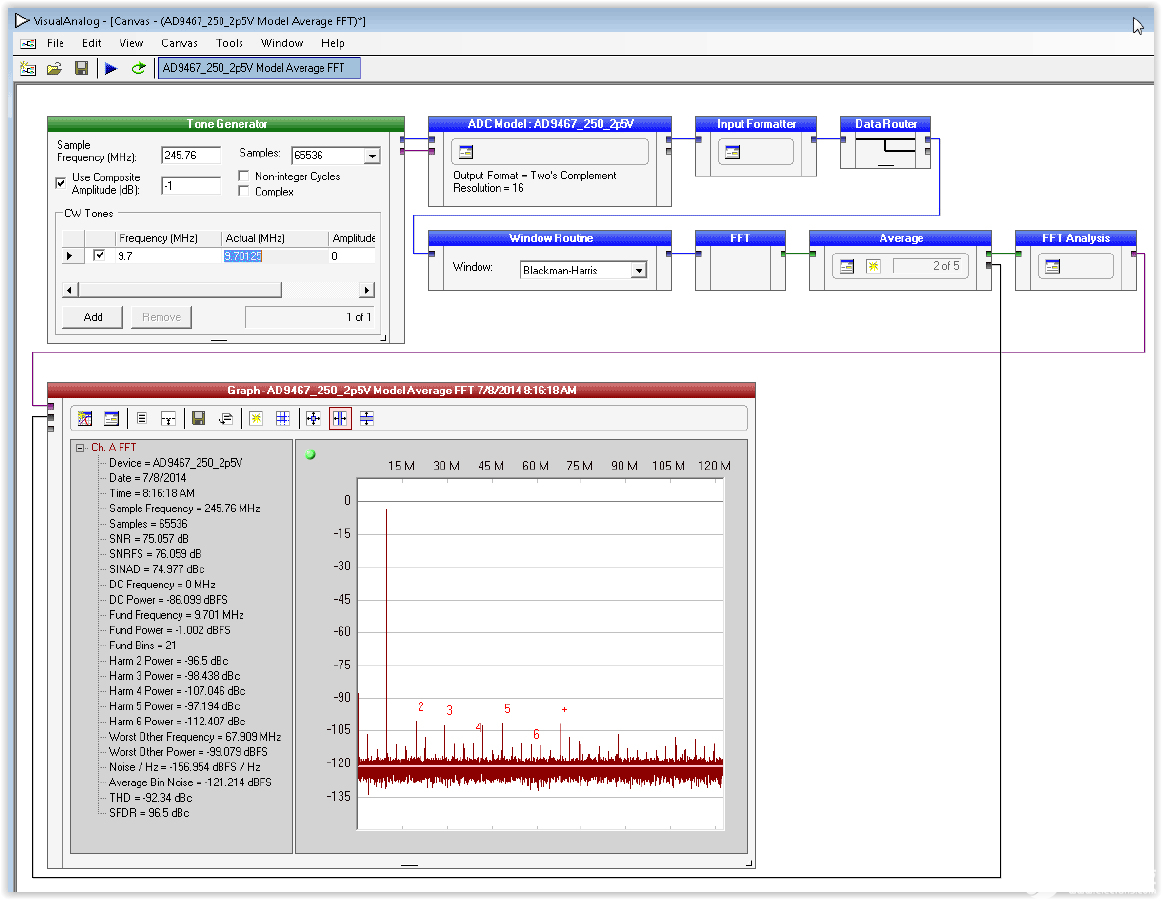

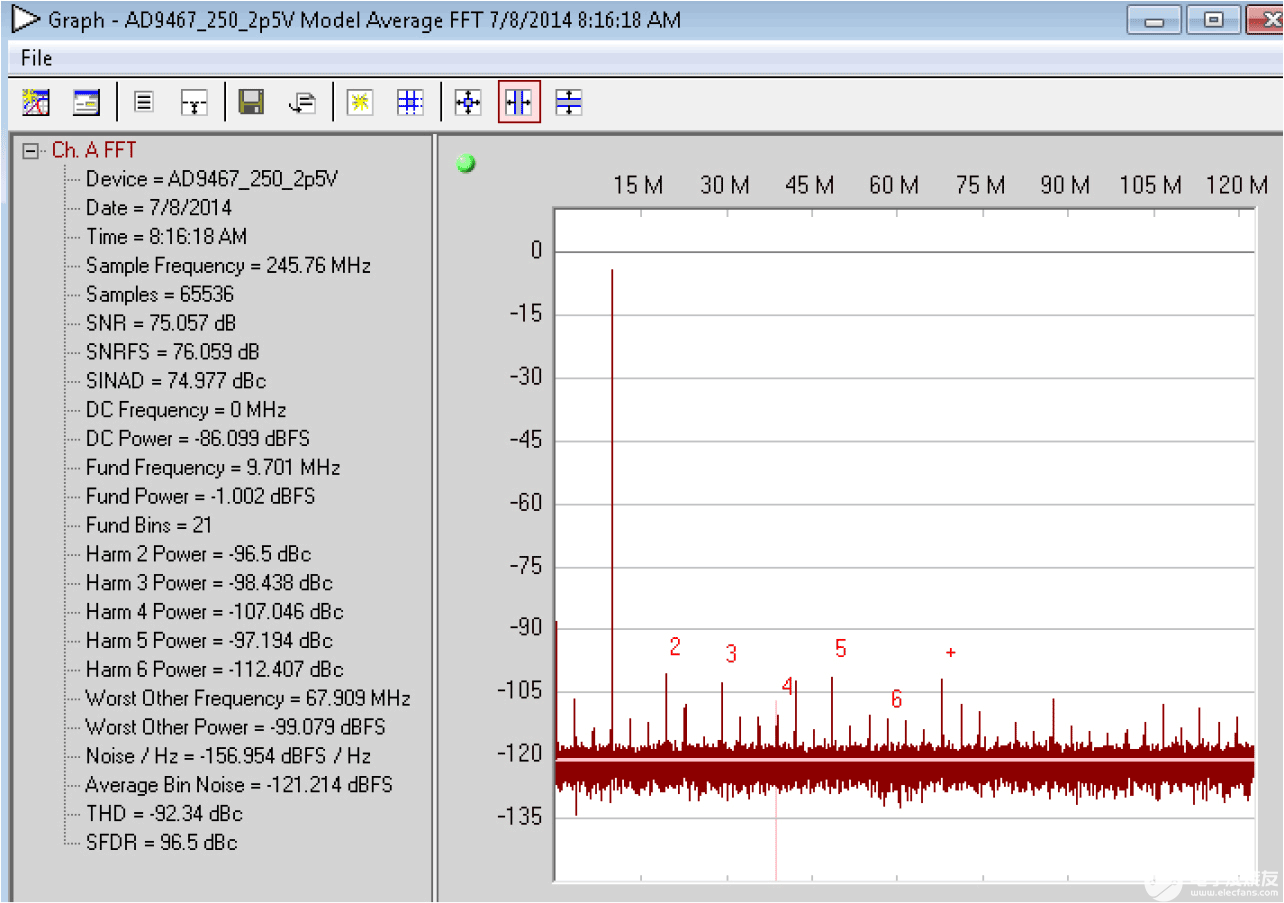

AD9467的ADIsimADC型号可在ADC→单通道→AD9467菜单选项下找到。图2显示了ADIsimADC平均FFT曲线。

图2.ADIsimADC画布显示采用9.7 MHz单音FFT的AD9467。

设置ADIsimADC以预测ADC行为

在音调发生器模块中输入一个频率,然后按 Tab。 ADIsimADC 根据采样速率和样本大小自动将此频率转换为相干频率。图3显示了默认设置下9.7 MHz单音输入的FFT。

图3.ADIsimADC单音FFT,频率为9.7 MHz。

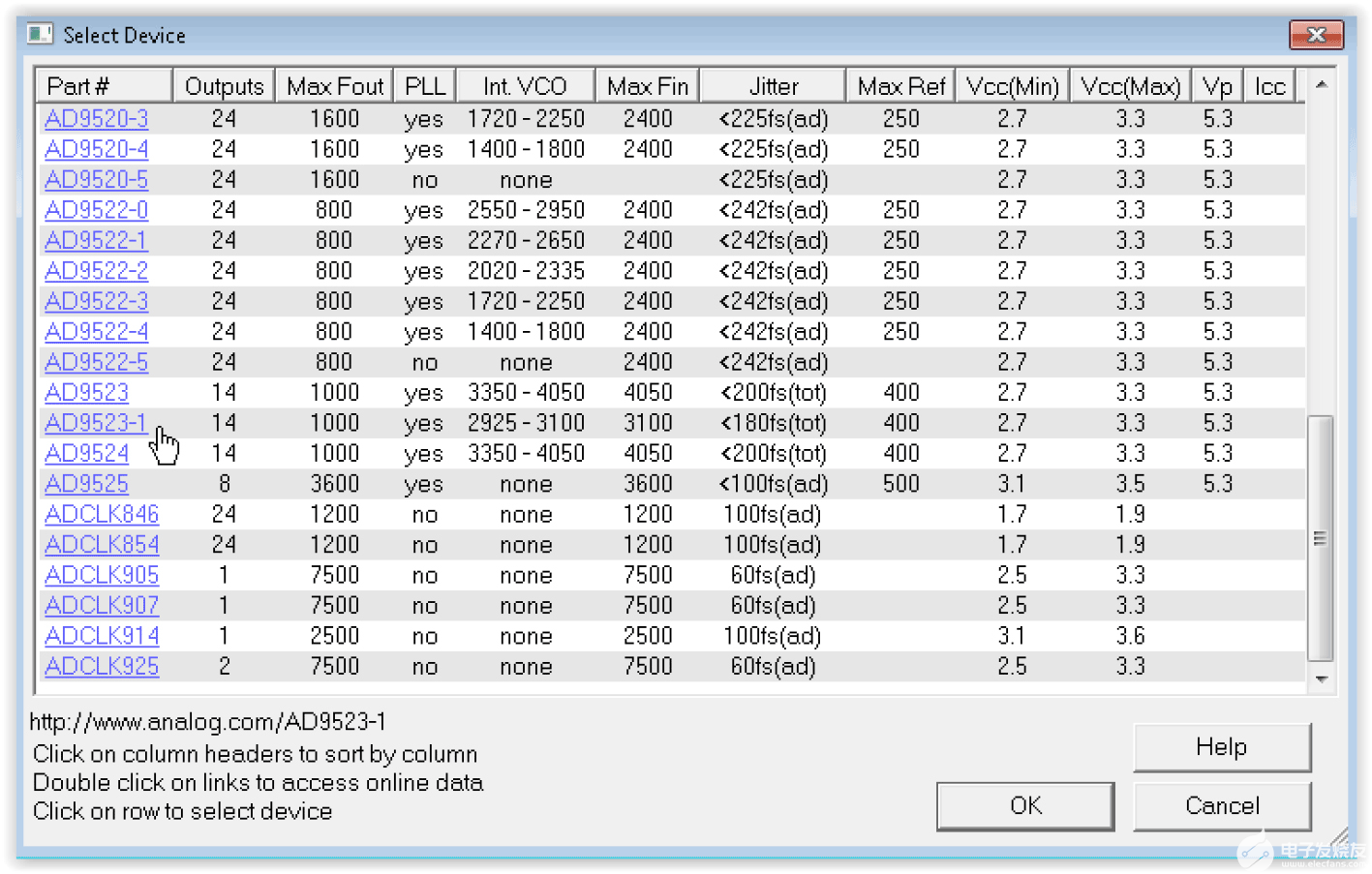

设置ADIsimCLK以预测AD9523-1行为

接下来,下载并安装ADIsimCLK软件。安装后,打开程序并选择文件→新建。将出现一个窗口,其中包含一系列设备,如图 4 所示。

图4.ADIsimCLK器件选择。

遵循与实际预期系统实现最相似的设置方法。在本例中,外部 30.72MHz 时钟提供对第一个 PLL 的参考。Crystek CVHD-950用作双回路PLL第一个环路的VCXO。内部VCO频率设置为2949.12 MHz,内部除以3。OUT7 上的 4 分频提供 245.76MHz 时钟。此设置如图 5 所示。

图5.ADIsimCLK中的AD9523-1设置。

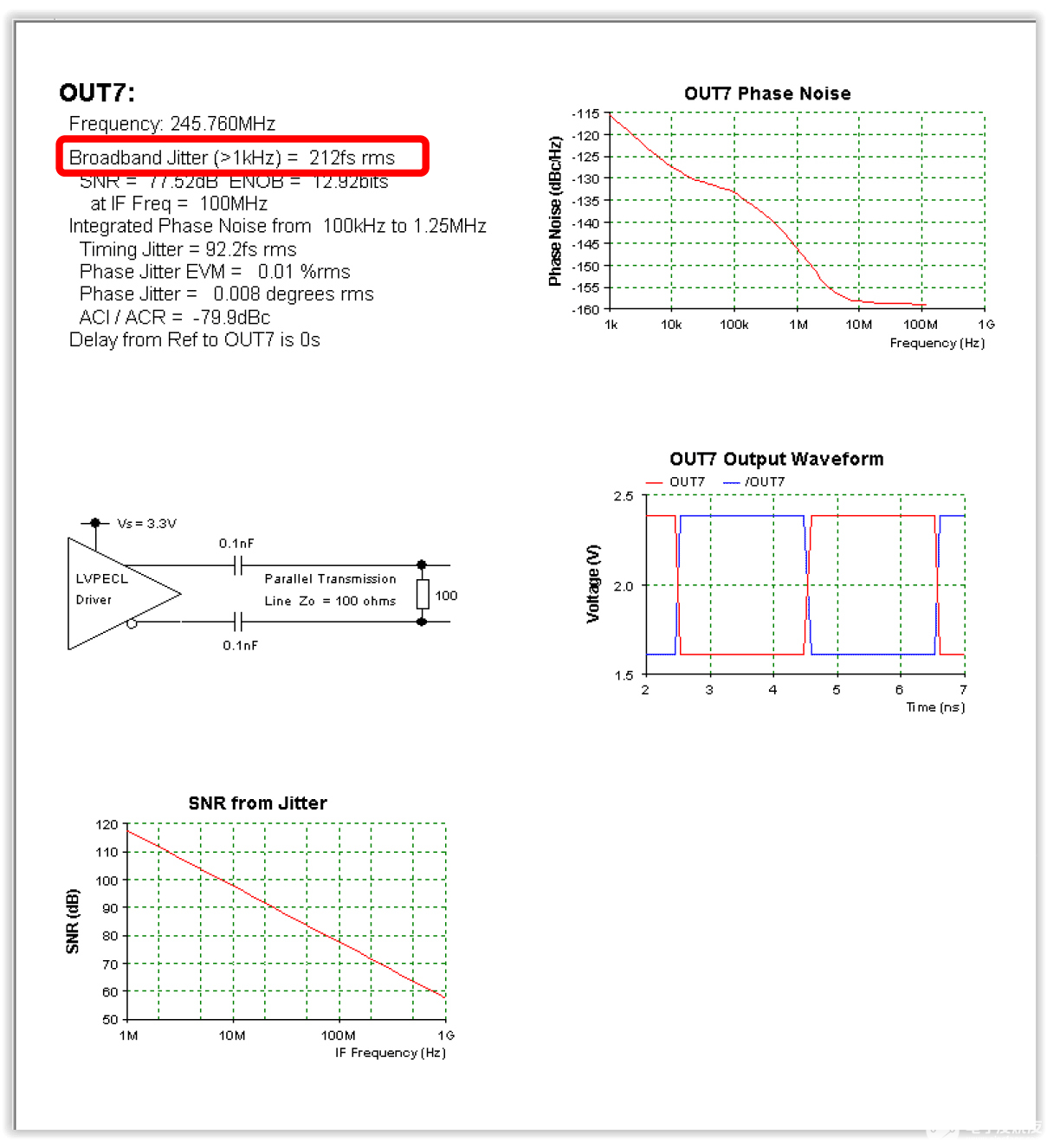

ADIsimCLK还可生成时钟输出报告,包括各种积分范围内的输出相位噪声和抖动。这些报告在与各种输出相对应的选项卡上可用。在此设置中,OUT7用于为AD9467评估板提供时钟。报告页如图 6 所示。突出显示了关键规格宽带抖动。

图6.ADIsimCLK 中的 OUT7 报告。

使用AD9523-1仿真AD9467

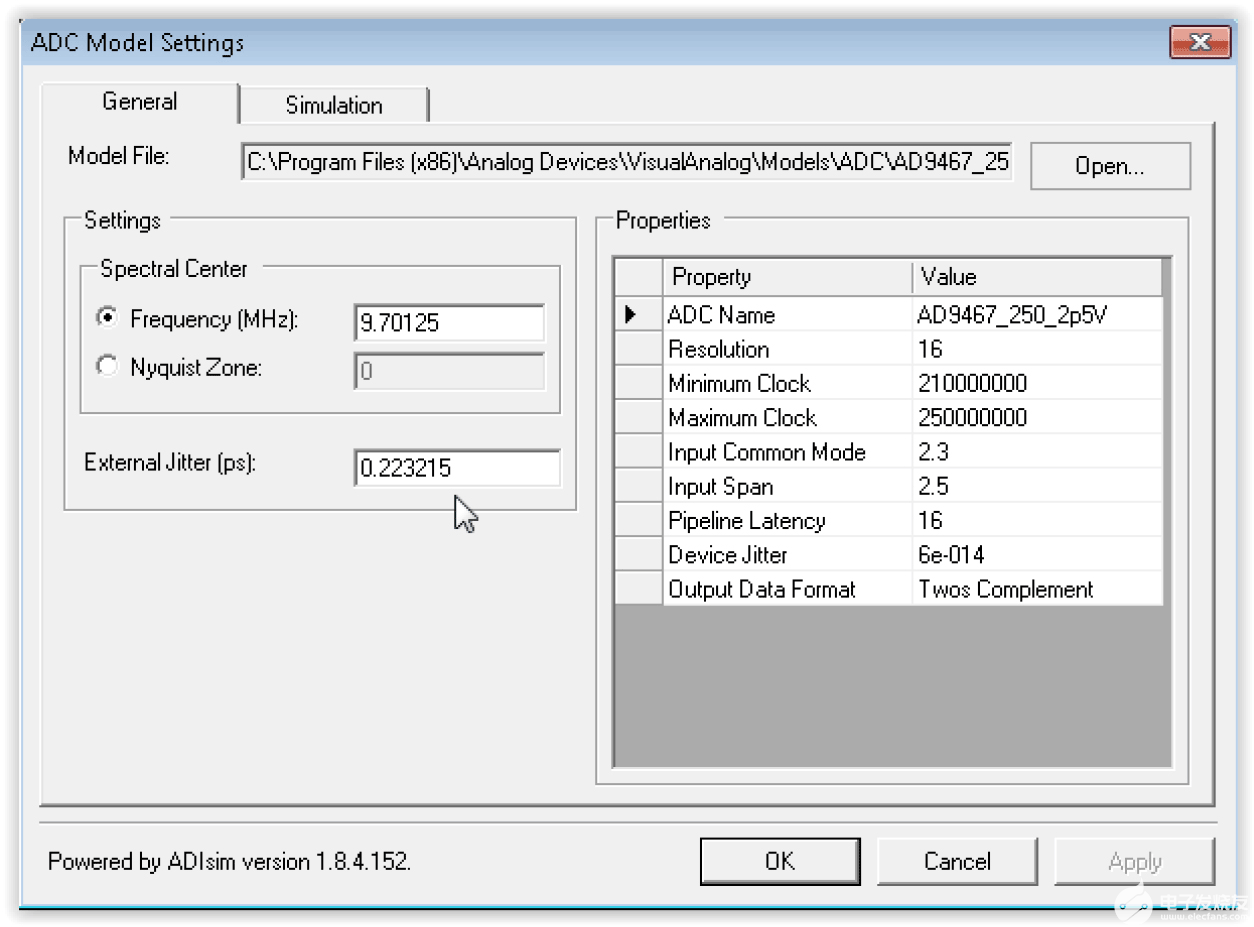

ADIsimADC可以预测AD9467与AD9523-1时钟配合时的性能。ADIsimCLK报告中的宽带抖动规格可以传递到ADIsimADC画布。在FFT画布中,ADC模型模块使用户能够更新总抖动规格,如图7所示。

图7.更新ADIsimADC模型中的抖动。

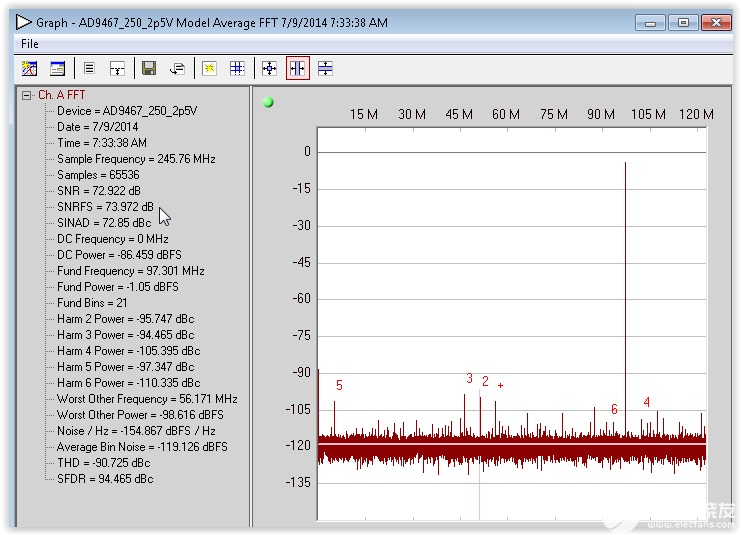

总抖动可以计算为各个抖动分量的和方根 (rss)。在这种情况下,孔径抖动为60 fs,宽带抖动为215 fs。传递给ADIsimADC的rss抖动为223.2 fs,产生图8所示的97 MHz单音FFT。利用更新的抖动,ADIsimADC可以预测任何输入频率下的预期性能。

图8.97 MHz输入时的单音FFT,具有ADIsimADC中更新的抖动特性。

关于抖动的简短说明

ADC必须定期对模拟信号进行采样。需要一个稳定的采样时钟,因为任何非理想的时钟源都会产生一些相位噪声。抖动是采样时钟载波两个指定频率偏移之间的相位噪声在时间段内的积分。对于ADC,宽带噪声通常被认为是最重要的。ADIsimCLK计算宽带抖动,对高于1 kHz偏移的相位噪声进行积分。该宽带抖动被传递到ADIsimADC模型,以了解抖动对ADC性能的影响。有关采样时钟抖动如何影响ADC性能的更多信息,请参阅AN-756应用笔记:采样系统以及时钟相位噪声和抖动的影响。

测量的性能

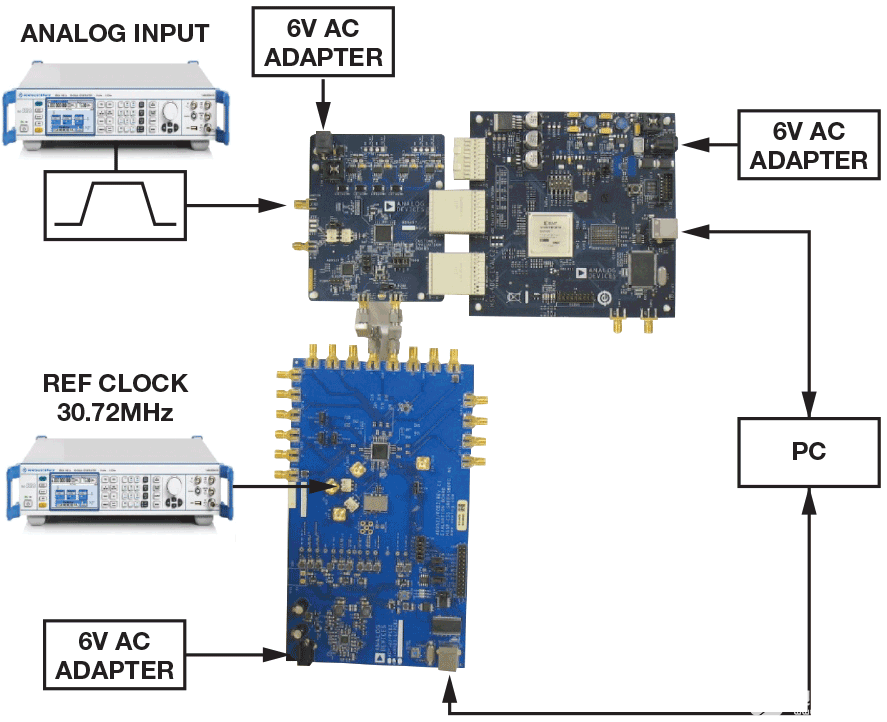

ADIsimADC预测使用AD9467评估板和AD9523-1评估板进行测试。AD9523-1配置为在OUT7上产生245.76 MHz LVPECL时钟。该输出耦合到AD9467评估板,该评估板经过修改,可接受J200和J201上的差分时钟输入。此设置如图 9 所示。

图9.显示AD9523-1和AD9467评估板的硬件设置。

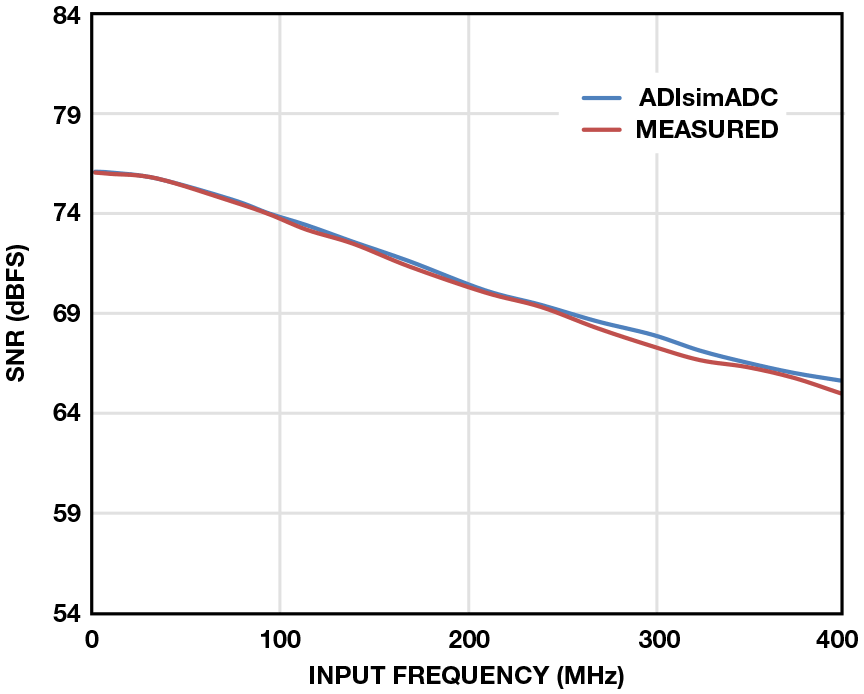

该设置使用2 MHz至400 MHz的模拟输入频率收集数据。 使用VisualAnalog捕获单音FFT,并根据ADIsimADC预测编译和绘制数据。图10显示了SNR与频率的关系。请注意模拟与实际测量值的匹配程度。

图 10.SNR与模拟输入频率的比较ADIsimADC和实际测量数据

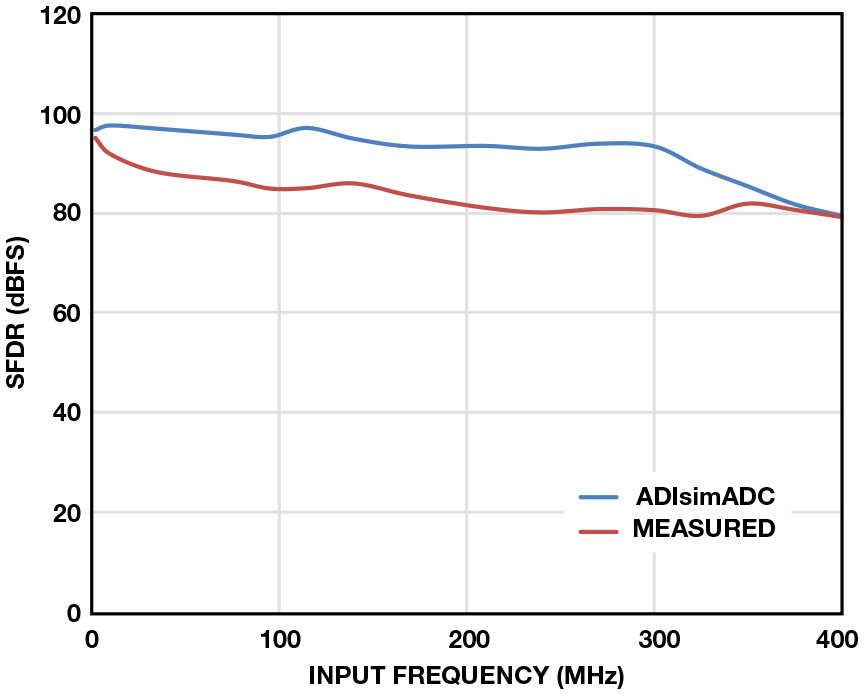

图 11 显示了 SFDR 数据。这些数字并不完全一致,但不同频率的模拟数据和测量数据之间的总体趋势非常吻合。SFDR高度依赖于PC板布局,组件,时钟幅度,这可以解释差异。

图 11.SFDR与模拟输入频率的比较ADIsimADC和实际测量数据

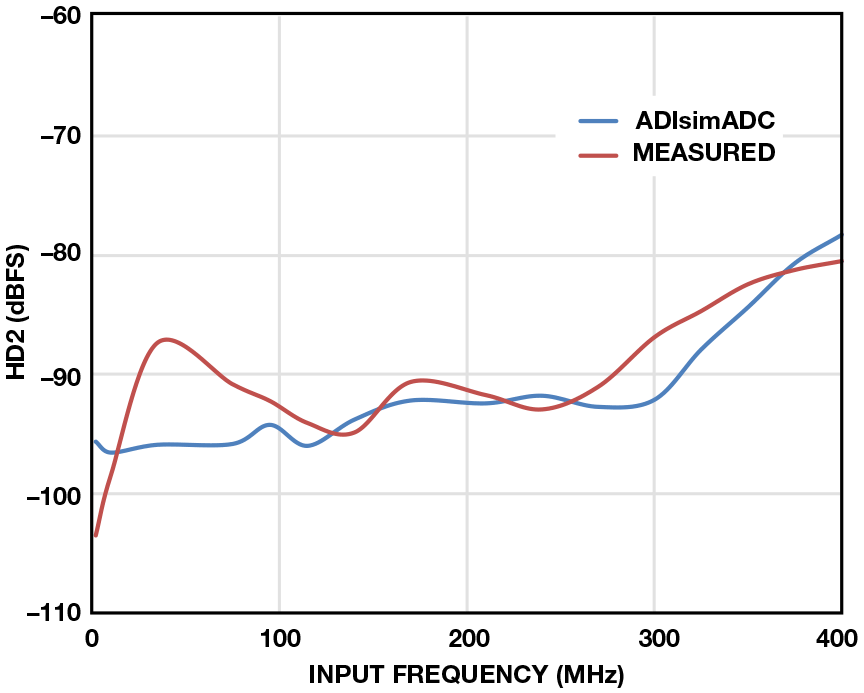

更好的失真测量方法是比较二次和三次谐波失真的仿真和测量数据,如图12和图13所示。仿真和测量的HD2性能非常匹配,证明进入评估板ADC的差分信号在幅度和相位方面非常平衡,并且评估板的布局足够好,不会显著影响差分信号平衡。

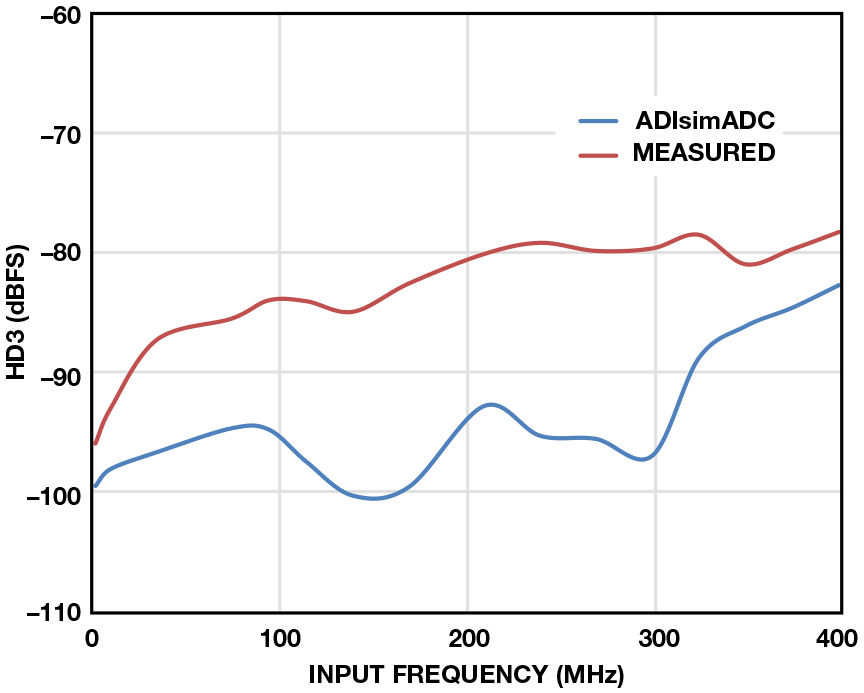

另一方面,预测 HD3 性能随频率变化可能很棘手。ADIsimADC模型是通过查看特性化过程中的ADC性能和DNL数据而开发的。该算法使用插值和外推技术来预测特定频率下的动态范围,但无法准确预测HD3在所有点的性能。

图 12.HD2与模拟输入频率的比较,比较ADIsimADC和实际测量数据。

图 13.HD3与模拟输入频率的比较,比较ADIsimADC和实际测量数据。

HD3的实际性能在很大程度上取决于实际因素,如电源电压、元件选择、ADC输入缓冲器和时钟信号质量。

HD3 预测可能并不总是正确的,但频率的总体趋势在模拟数据和测量数据之间提供了良好的一致性。

在许多系统设计中,主要的性能指标是SNR。SFDR和动态范围取决于许多其他因素。仿真和测量数据之间的SNR值匹配得非常好,这使系统设计人员对ADC和时钟的选择充满信心。

结论

对更短设计周期的需求给系统设计人员带来了巨大的压力,要求他们评估新产品的设计。硬件评估几乎总是必要的,但选择错误的硬件组合最终可能会花费金钱和时间。软件评估可以作为对ADC产品的快速简便的初步了解。ADIsimADC和ADIsimCLK为系统设计人员选择ADC和时钟IC提供了一种简单有效的方法。这些软件工具允许系统设计人员混合搭配各种ADC和时钟IC,从而对所选组件产生足够的信心,以执行硬件评估。

审核编辑:郭婷

-

Semtech发布LoRa® Corecell参考设计,可加快室内网关产品上市2019-12-03 2057

-

lavbiew 加快读取txt的速度2014-02-11 4529

-

怎么设计射频器件建模工具?2019-08-20 1878

-

ADC 建模工具加快评估过程2019-10-23 3299

-

如何对系统进行最佳建模2021-01-07 1625

-

请问放大器参数评估工具是如何工作的?2021-04-20 1634

-

如何加快32的运行速度?2023-11-06 644

-

并联稳压器可加快电源供应启动速度2009-10-25 1174

-

学生发明可加快伤口愈合设备2010-03-26 1142

-

ADC建模工具加快评估过程2016-01-07 385

-

ADI高速ADC的行为模型及工具软件2018-06-03 3972

-

安森美行业首创的云联接平台Strata Developer Studio简化并加快您的研发、评估和设计2019-03-22 4342

-

用于评估ADC的产品及其评估板的模型及工具软件2019-06-11 4056

-

如何用ADIsimADC完成ADC建模2023-11-28 488

-

C2000 MCU的ADC输入电路评估(使用TINA-TI仿真工具)2024-09-07 562

全部0条评论

快来发表一下你的评论吧 !