EDA探索之GIDL技术分析

EDA/IC设计

描述

2022年,集成电路半导体行业最热的头条是“EDA被全面封锁”。如何突破EDA封锁,成为行业发展的关键词,也是群体焦虑。在全球市场,有人比喻EDA是“芯片之母”,如果没有了芯片,工业发展和社会进步将处处受制,EDA的重要性也上升到了战略性高度。尽管国际封锁形势严峻,但睿智的中国科技人擅于把危机化为机会,从《加快自动研发应用,让工业软件不再卡脖子》,到《破解科技卡脖子要打好三张牌》,即一要打好“基础牌”,提升基础创新能力;二要打好“应用牌”,加强对高精尖国货的应用;三是要打好“人才牌”,让人才留得住、用得上、有发展……,各种政策、举措和实际行动,处处彰显了我们中国科技的发展韧性。

我们EDA探索频道,今天迎来了第7期的精彩内容——GIDL:DIBL的远房兄弟,下面就跟着小编一起来开启今天的探索之旅吧~

在半导体器件当中,提到DIBL时,往往会提到GIDL。所谓GIDL是Gate Induced Drain Leakage的简称。实际上,GIDL与DIBL除了名字比较像之外,实质上并无多少关系。所以最多只能算远房兄弟。

所谓GIDL,实际上是晶体管在截止时的一种漏电机制。以NMOS为例,其发生在漏端高电压,栅极零电压或者负电压的状态。这种状态实际上MOS的电流应该处于Ioff的状态。而由于GIDL的存在,Ioff会异常上升,并且随着栅极负压的增大而变得更明显。

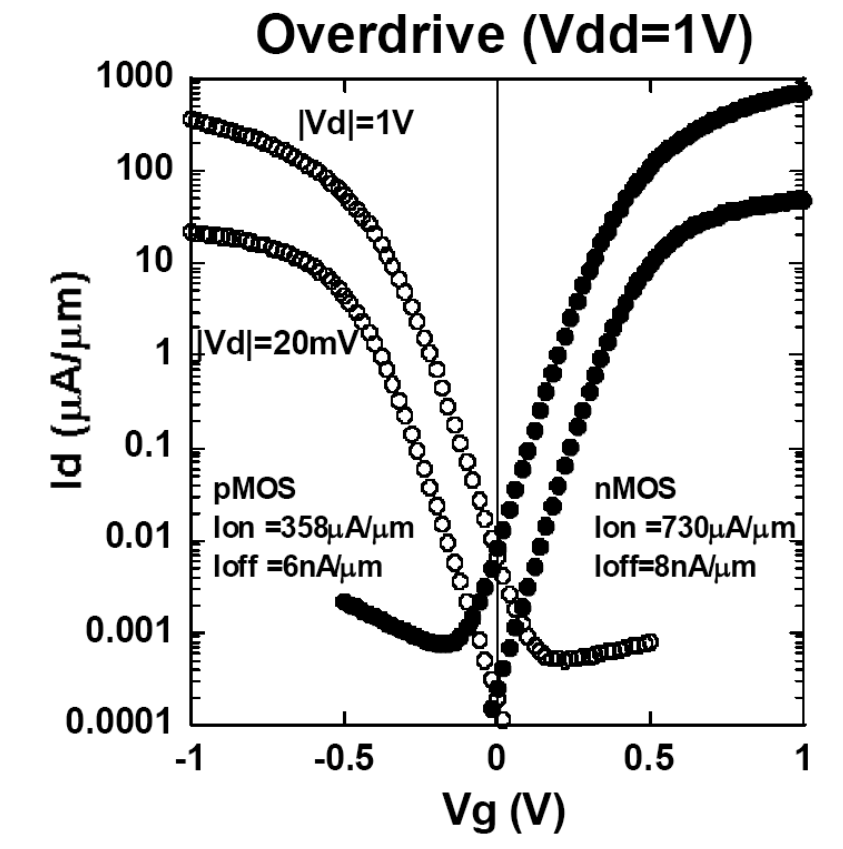

图:GIDL的例子:实心点NMOS,空心点PMOS。来自M. Lundstrom Lecture Notes EE-612 F06

一般来讲,我们认为器件在线性区漏极电压很小,没有GIDL现象 。从上图明显可以看到在0V时Idsat曲线比Idlin曲线的电流高了两个数量级。在反方向继续扫描Idsat曲线,Ioff反而会进一步升高。

另外,在这个图中同样也可以看到DIBL。有兴趣的同学可以复习一下前面的内容。EDA探索丨第5期:DIBL究竟是什么?

一句话概括GIDL的机制,即是栅极与漏极交叠区发生的BTBT。这里面有两个要素:栅漏的交叠与BTBT漏电。

顾名思义,GIDL即是Gate与Drain之间的漏电。从物理上来说,栅极与漏极之间有绝缘层相隔,如果发生漏电则必须要有一定的交叠区域,来达到“面对面”的效果。对于理想的MOS来说,实际上栅与漏是没有交叠的。但是在实际器件当中,即便是自对准工艺也会让栅极和源漏之间有少量的交叠。这样,栅极和漏极之间便可以隔氧化层相望。

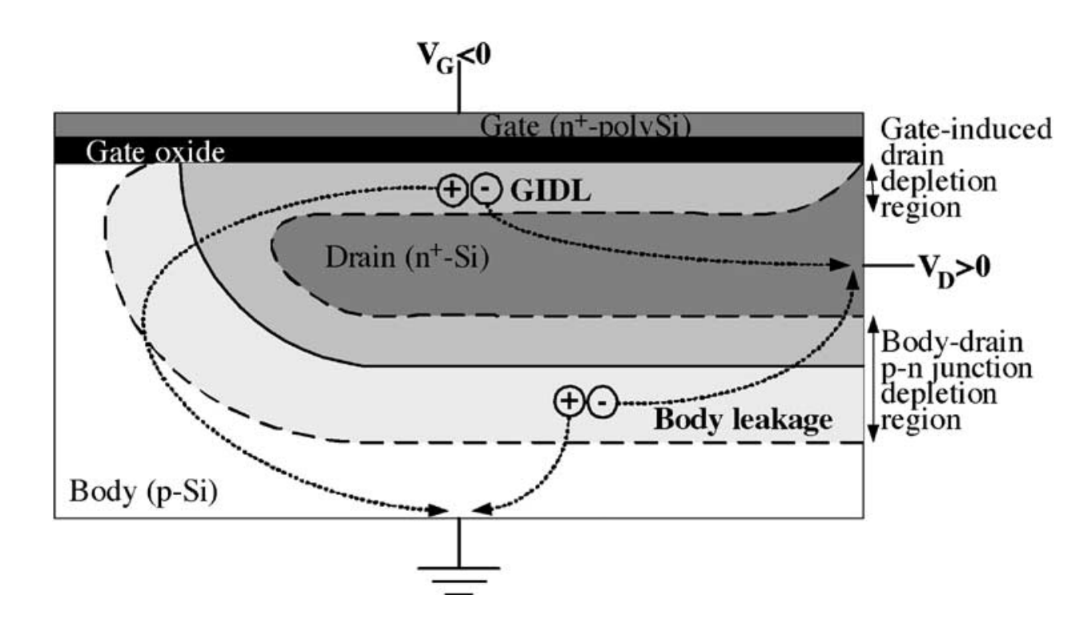

图:GIDL机制示意。来自IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 53, NO. 5, MAY 2006

在栅压为负,漏端电压较大时。在栅与漏的交叠区会产生一个小的耗尽区,称为Gate-induced Drain Depletion Region。在这个区域当中,新产生的电子空穴对可以被Body或者Drain端收集,产生电流。

至于新产生的电子空穴对,可以是自然的热激发,但是更主要的是BTBT,即Band-to-band tunneling的简称,中文一般叫做带间隧穿。

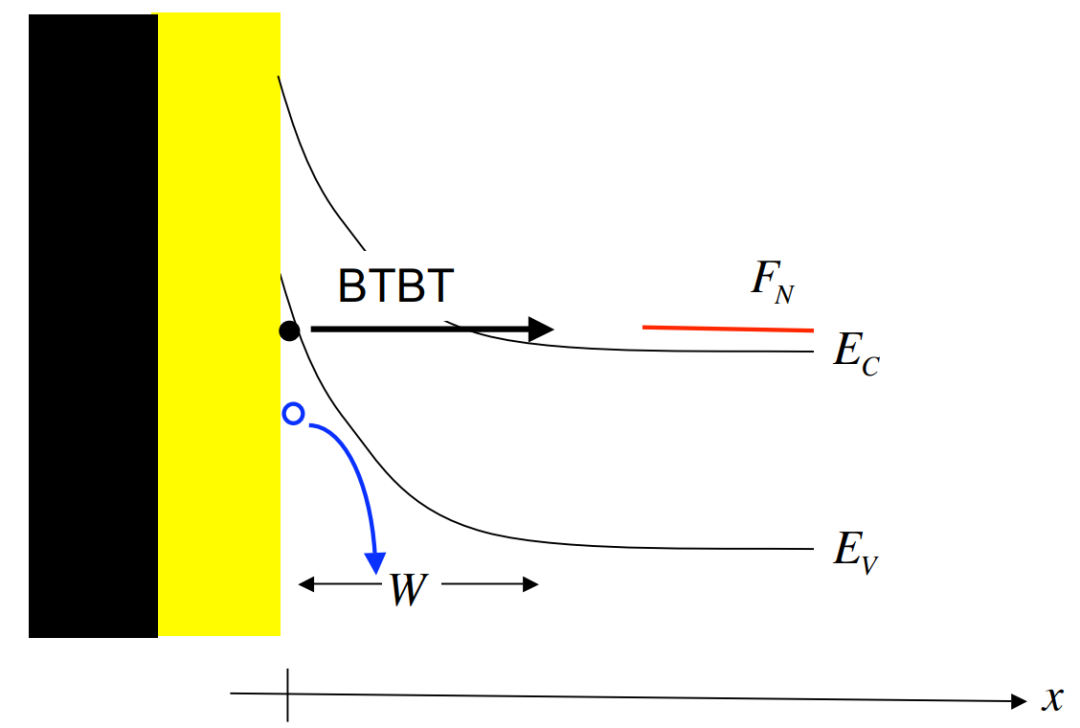

图:漏极耗尽区BTBT示意。来自M. Lundstrom Lecture Notes EE-612 F06

从能量的角度来看,导带中未被电子占用空能态与价带中被电子占用能态有相同能量,当势垒区比较窄时,电子可以从价带直接到导带,从而产生电子空穴对。进而载流子被收集。这个过程与太阳能电池是类似的,即半导体被光激发之后产生额外的电子空穴对,之后被分离与收集。只不过在BTBT当中,这种过程是在电场作用发自发产生的。但是产生了额外电流这一点是相同的。

GIDL主要影响的是半导体器件在关断状态下的功耗,随着器件普遍的移动化,小型化趋势。这种漏电是必须要克服的,否则会大大影响产品的续航表现。鲁迅先生告诉我们,解决问题要对症下药。既然GIDL的两个要素是栅漏电极的交叠和BTBT,那么我们在器件设计时,要尽量地减少栅极的交叠设计,同时仔细设计LDD等方法,以减小Gate-induced Drain Depletion Region的电场,从而降低BTBT的发生。

编辑:黄飞

-

为什么选择eda进行数据分析2024-11-13 1329

-

eda技术与vhdl基础 eda的主要功能优点 现代EDA技术的特点有哪些2023-08-09 3192

-

eda工具的技术来源 eda技术的设计方法2023-07-21 1419

-

EDA技术是什么?EDA常用软件有哪些2022-01-24 13902

-

EDA技术的发展,EDA技术的基本设计方法有哪些?2021-04-21 4320

-

什么是EDA技术?2019-07-30 2370

-

EDA技术从何而来?EDA技术发展历程2019-02-21 4155

-

eda是什么技术_eda为什么又叫单片机2018-03-12 22364

-

EDA技术的简单介绍及特点分析2018-01-05 12940

-

EDA技术基础知识及数字系统设计实例2013-01-08 4088

-

EDA技术应用与发展之管窥2012-09-12 2490

-

探索性数据分析(EDA)及其应用2011-01-24 1908

-

电基于公共数据结构的EDA仿真波形分析技术2009-12-07 777

-

基于公共数据结构的EDA仿真波形分析技术2009-10-23 921

全部0条评论

快来发表一下你的评论吧 !