浅析单电阻采样时序及具体实现

电子说

描述

在对产品体积及成本有较高要求时,单电阻电流采样方案foc进入我们的视野。理论上,单电阻电流采样方案可以实现和二电阻、三电阻电流采样同样的效果,唯一美中不足的是,单电阻电流采样方案没办法实现高调制比,不过这并不影响单电阻电流采样方案的广泛应用。

本文从单电阻电流采样原理出发,深入分析相关理论及时序,并通过simulink仿真实现相关算法

1、单电阻采样原理

母线电流能够反映三相电流。

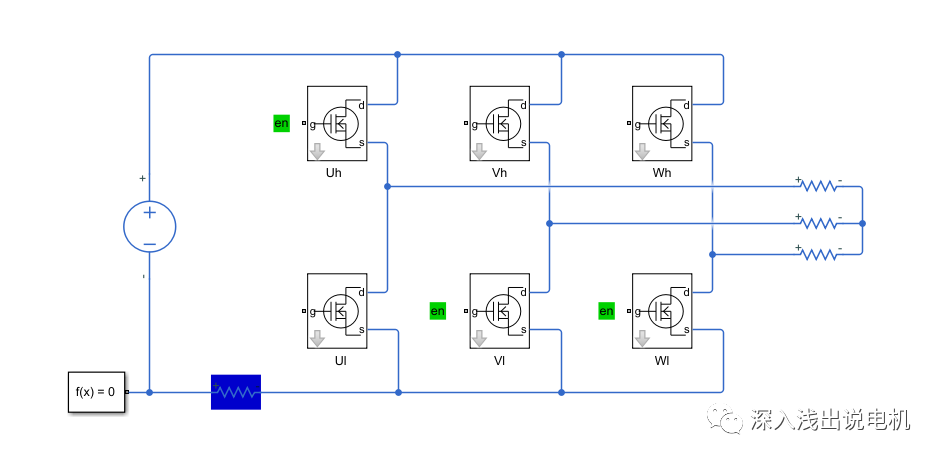

三相电桥示意图如下,电流采样电阻放在母线负端,电路工作在逆变工况时,可以将电路工作状态分为如下四种状态。

1.三个下桥导通,没有上桥导通

- 二个下桥导通,一个上桥导通

- 一个下桥导通,二个上桥导通

- 没有下桥导通,三个上桥导通

其中电路工作在状态1、状态4时,没有电流流过采样电阻。

工作在状态2时,如上图,采样到的电流均流经U相上桥,此时的母线电流等于U相相电流。

工作在状态3时,如上图,采样到的电流为流经U相上桥、V相上桥的电流之和,由基尔霍夫定律,Iu + Iv + Iw = 0; 可得此时的母线电流等于负的W相相电流。

工作在状态3时,如上图,采样到的电流为流经U相上桥、V相上桥的电流之和,由基尔霍夫定律,Iu + Iv + Iw = 0; 可得此时的母线电流等于负的W相相电流。

当三相电流中的两相电流能够采样得到后,第三相波形可以通过基尔霍夫定律重构。

对开关状态的划分可以再详细一点,整理所有上下桥开关状态下,母线电流与相电流的关系。参照上表(表格来自microchip应用笔记AN1299,文末给出下载方式)

**2、**单电阻采样时序

2.1、单电阻采样时序

上文分析了单电阻采样的原理,以下内容讨论如何协同采样时刻和foc计算。

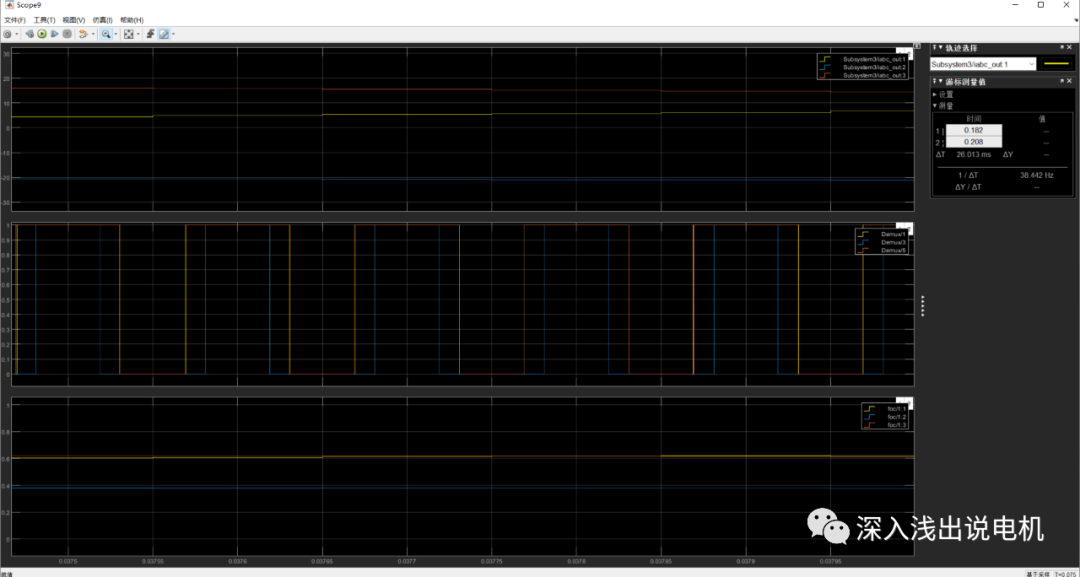

选择第一个采样点为每一个pwm周期导通时间最短的一相上桥关闭后延时若干个时钟(大于下桥臂导通延时)后的时刻。上图figure2中黄色信号时刻。

选择第二个采样点为每一个pwm周期导通时间第二短的一相上桥关闭后延时若干个时钟(大于下桥臂导通延时)后的时刻。上图figure2中红色信号时刻。

上图中figure1为三相上桥驱动波形,figure2为触发采样信号,每个pwm周期中前两个有效,figure3为母线电流信号,figure4为pwm计数器信号。

电流采样在每个pwm周期中,计数方向为向上计数的半个周期进行,计数到周期值后触发pwm更新事件中断,执行foc计算,电流采样中断优先级高于pwm更新时间中断。

考虑到实际adc采样需要一定的时间,三相pwm占空比中其中两相占空比非常接近时(有效导通时间过小),将导致采样失败,此时需要通过补偿来增加有效导通时间

2.2、补偿最小采样时间

如上图figure2,在svpwm扇区切换的时候,两相占空比几乎一样,有效导通时间小于单片机adc采样时间,此时必须补偿导通时间。

此处的补偿其实容易理解,我们的电流采样总是在pwm计数器上计数的时候触发,要保证采样时有足够的采样时间,只需要当两相占空比非常接近时,把占空比较大的一相加大即可,同时为了保证电压矢量大小不变,在pwm计数器下记数时,减去之前增加的时间。

实现方法为在pwm计数器计数到0和周期值时都触发pwm事件更新中断,当中断为下溢中断时,判断三相占空比之差,相差过近则增加占空比,并置标志位,上溢中断时判断标志位,标志位有效则减小相关相占空比。

补偿后波形如上图。其中figure1为三相上桥驱动波形,figure2为三相占空比大小。

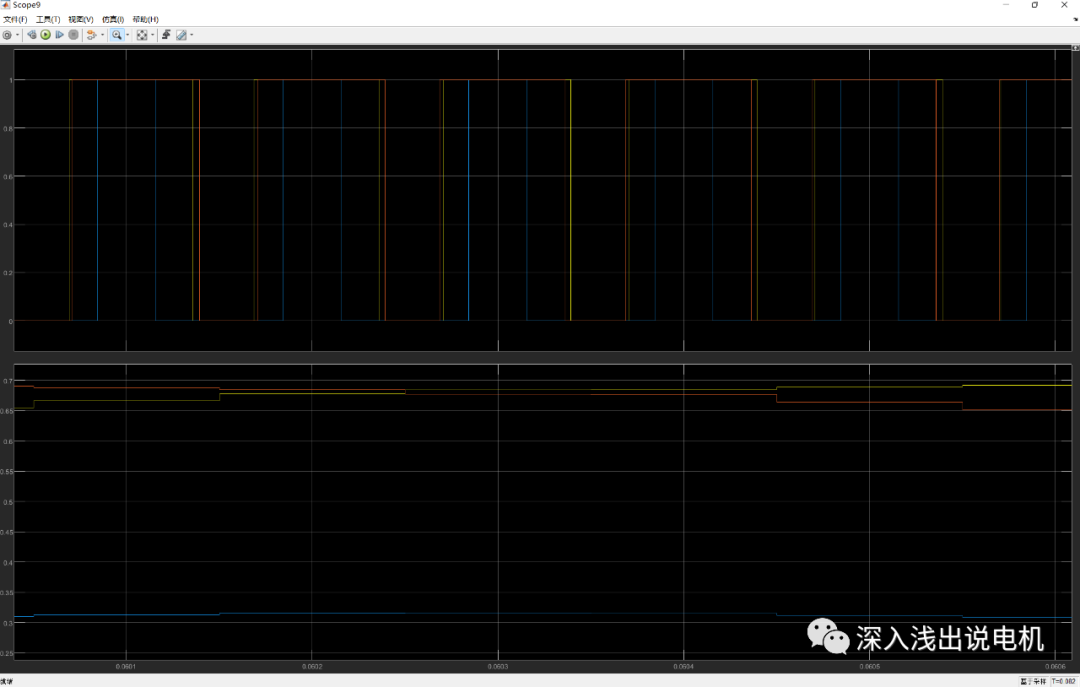

2.3、系统时序

完成实现过程分析后,我将单电阻电流采样foc分为以下4个模块

- 电流采样模块

- 电流重构模块

- foc计算模块

- 移相补偿模块

4个模块时序关系如上图,其中:

- figure1为pwm计数器;

- figure2黄蓝红波形为三相电流采样触发信号,绿色波形为电流重构模块执行时刻;

- figure3为foc计算模块执行时刻;

- figure4为移相补偿模块执行时刻。

放大波形如上。

- pwm计数器下溢时刻判断占空比大小,有需要的话进行补偿;

- pwm计数器上计数过程中完成两相电流采样;

- pwm上溢时刻进行电流重构,得到三相电流;

- 得到三相电流后执行foc计算;

- 完成foc计算后再次更新占空比,消除移相补偿造成的电压矢量误差。

3、单电阻采样具体实现

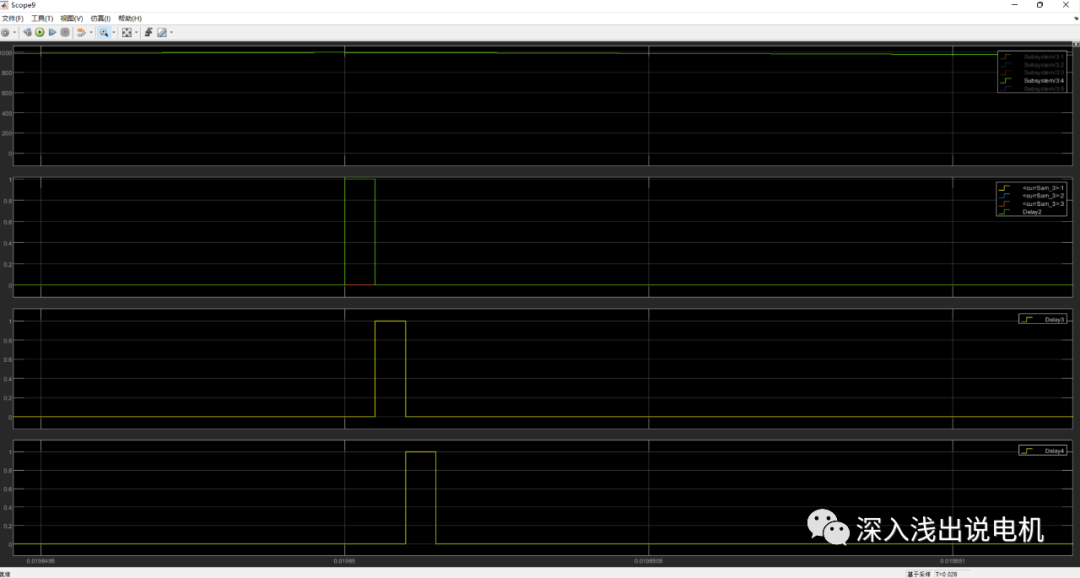

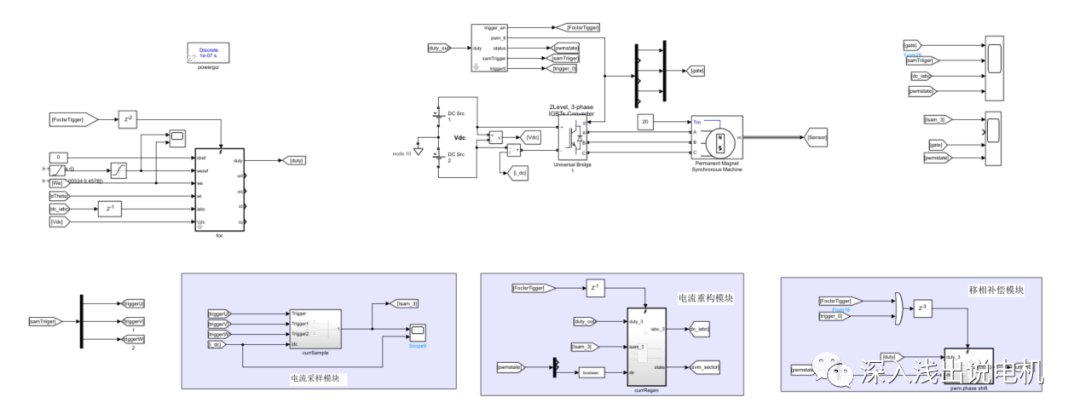

根据上述分析做出simulink仿真。

仿真中各个模块都尽量使用matlab程序实现,易于阅读,文末给出仿真模型的下载方式。

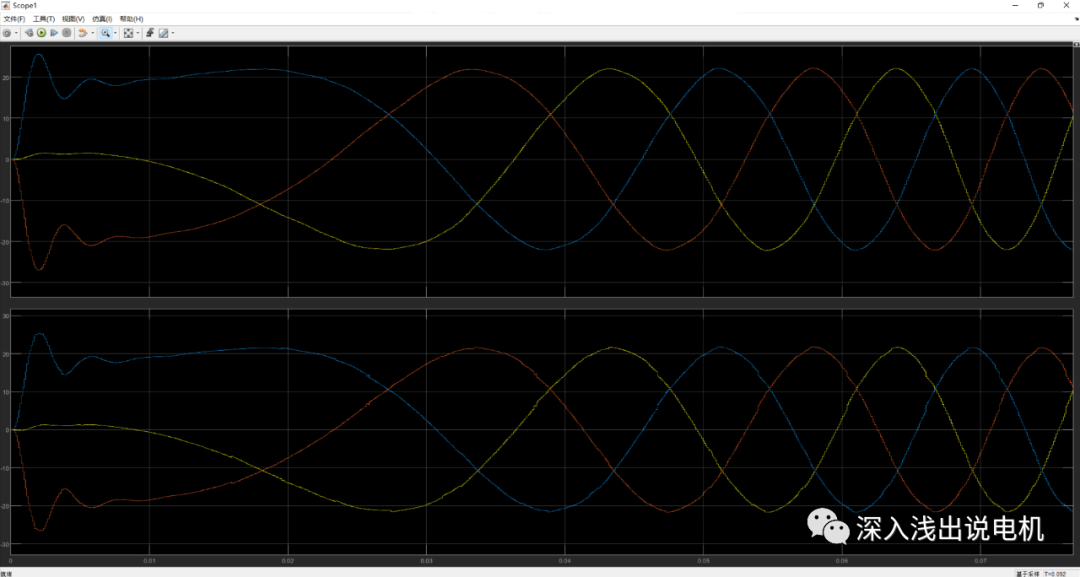

运行仿真,观查相间采样电流(上)和单电阻采样电流(下)结果,可见波形基本一样,美中不足的是单电阻采样电路在扇区切换时,因为采样点相对pwm周期的时刻发生变化,能看出受纹波电流的影响,单电阻采样电流存在畸变。

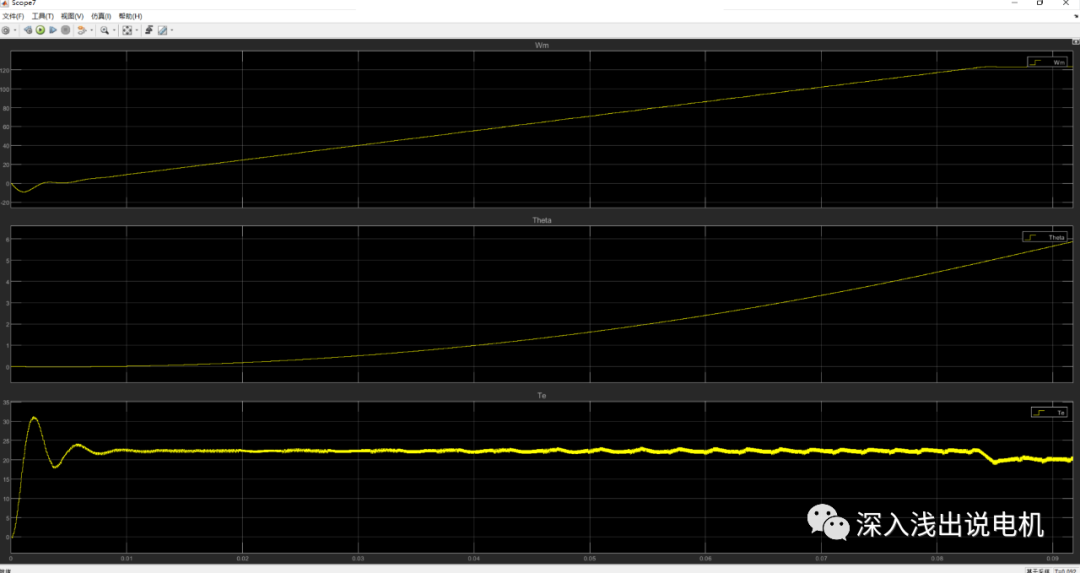

使用单电阻采样电流替换相间采样电流,引入环路,环路运行正常,与使用相间采样电流运行结果一致。

-

采样电阻按材质分类可分为:厚膜采样电阻和合金采样电阻;#采样电阻jf_92730378 2026-03-24

-

电流采样电阻的采样原理2024-08-27 4961

-

求助,关于FOC单电阻的电流采样问题求解2024-04-01 1875

-

foc单电阻采样时序的软件实现2023-12-28 3735

-

浅析采样电阻的选择与运放的使用2023-10-22 5680

-

解析单电阻采样的原理以及注意点2023-07-06 7110

-

如何用单电阻采样驱动电机?2023-05-17 671

-

Simulink永磁同步电机控制仿真:单电阻采样时序及具体实现2023-03-14 959

-

无刷直流电机矢量控制(二):单电阻采样2023-03-08 1142

-

采样电阻的作用_采样电阻的选型2019-11-08 11263

-

基于FPGA实现高速ADC器件采样时序控制与实时存储2018-08-28 15098

-

基于开关磁阻电机驱动系统的单电阻电流采样技术2018-03-06 1794

-

变频器单电阻电流采样及相电流重构方法_陈小波2016-12-16 1336

全部0条评论

快来发表一下你的评论吧 !