Congestion修复实例及脚本分享-加Blockage array/keepout margin

电子说

描述

分享一个Congestion的示例与解决这个Congestion用的2种方法以及对应的效果。

下面的一个Design有一个Macro的pin density非常高,有高达1万个Pin,每层都有出Pin,且Pin基本上都是一个Track放一个,因此在它周围非常容易产生Congestion问题。

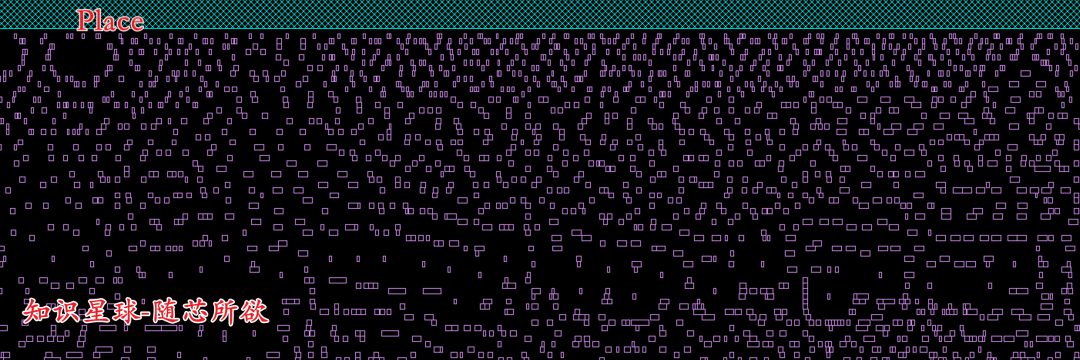

什么控制都不加,默认Place的Cell分布以及Congestion挺好的:

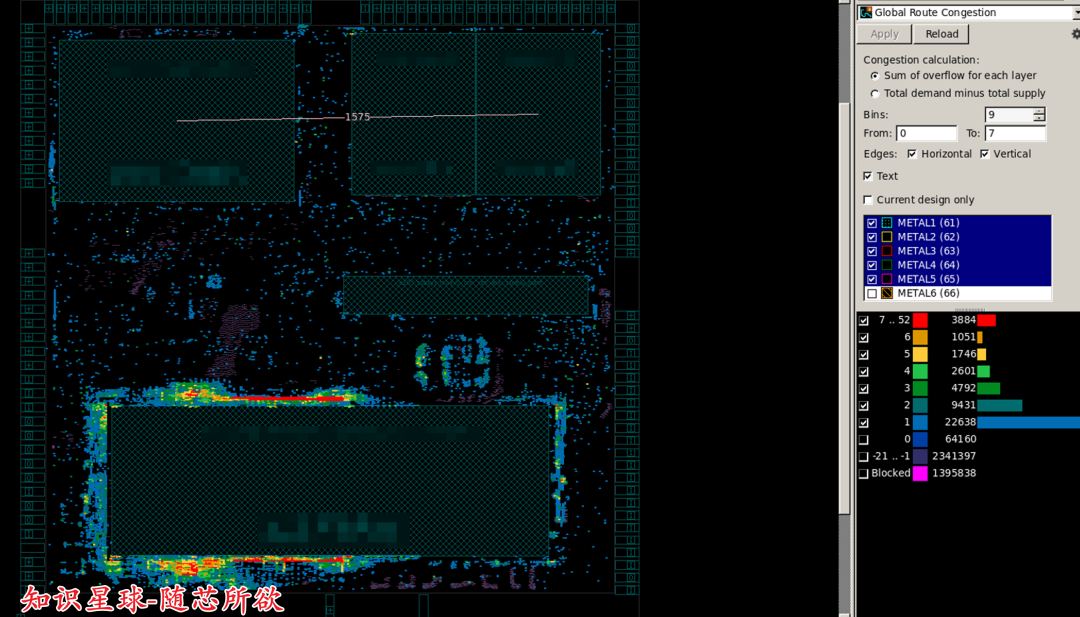

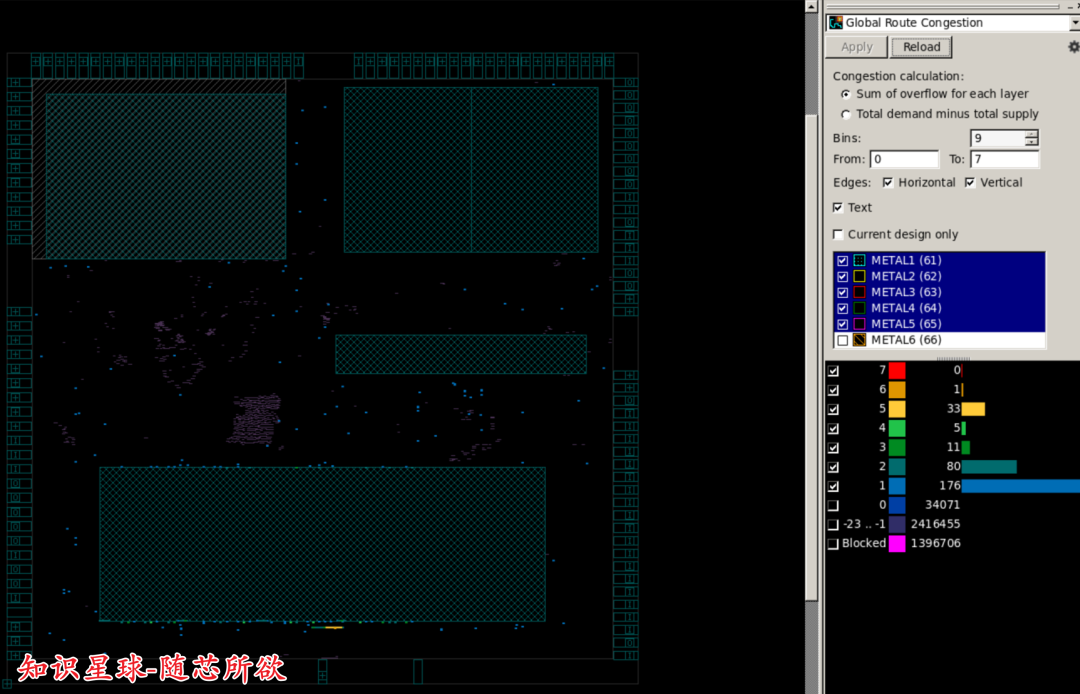

Place congestion:

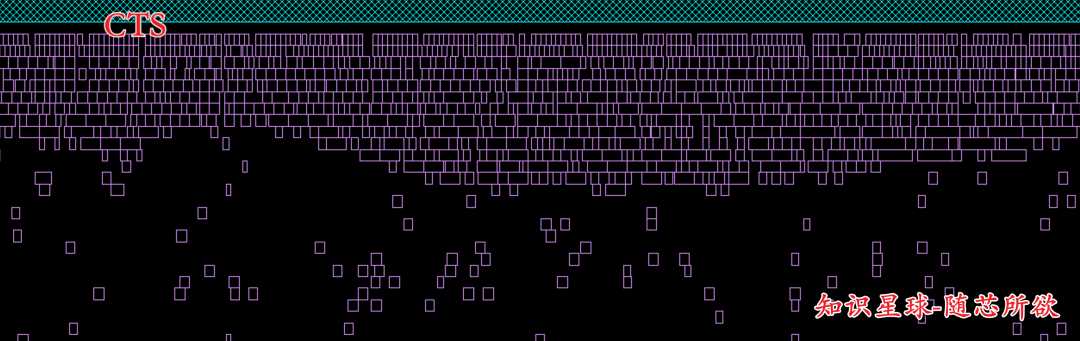

可是到了CTS之后发现Cell的摆放有很大的变化,Cell全部堆在了靠近Macro出pin的地方:

局部放大图(可以看到很多Buffer/inverter),density非常高:

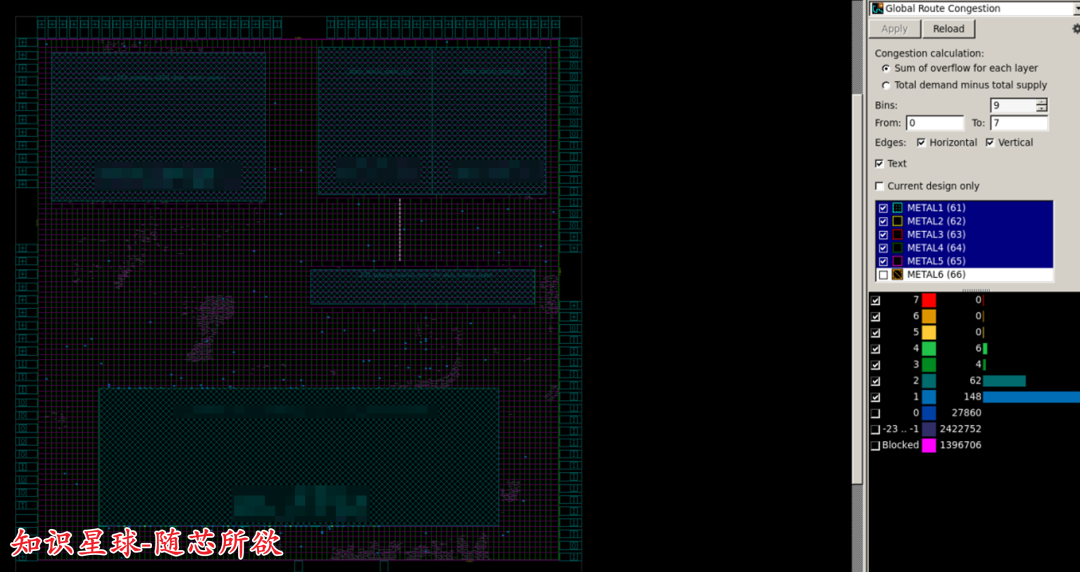

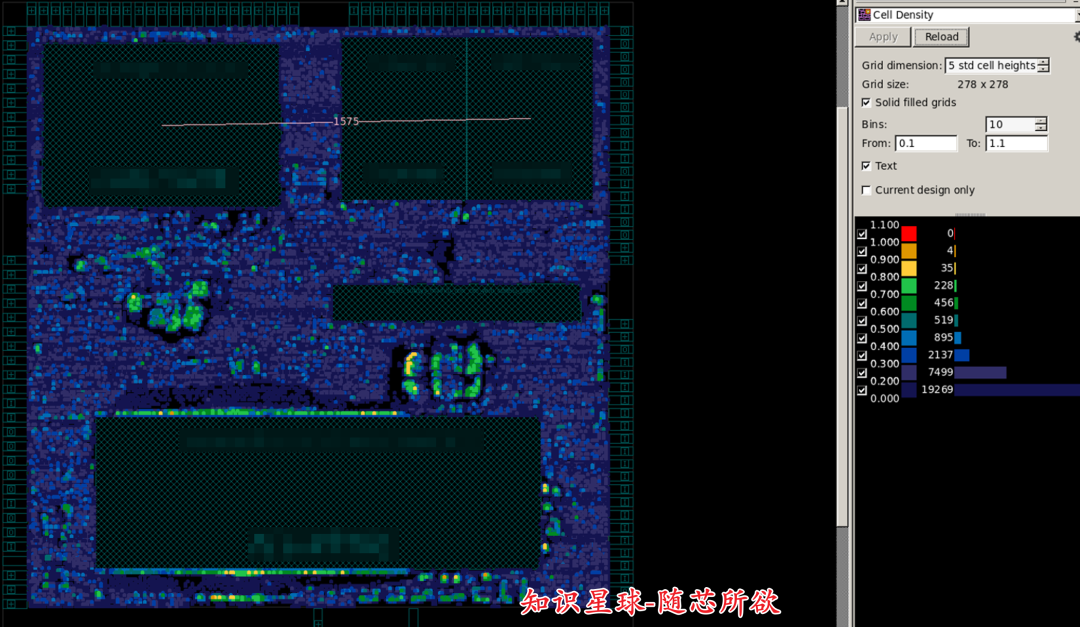

CTS阶段的congestion也变差很多:

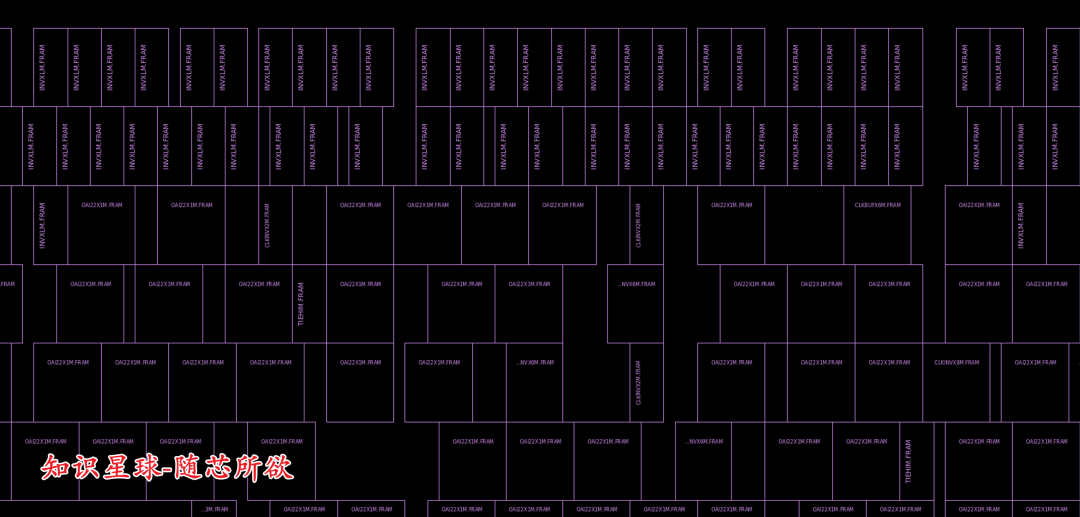

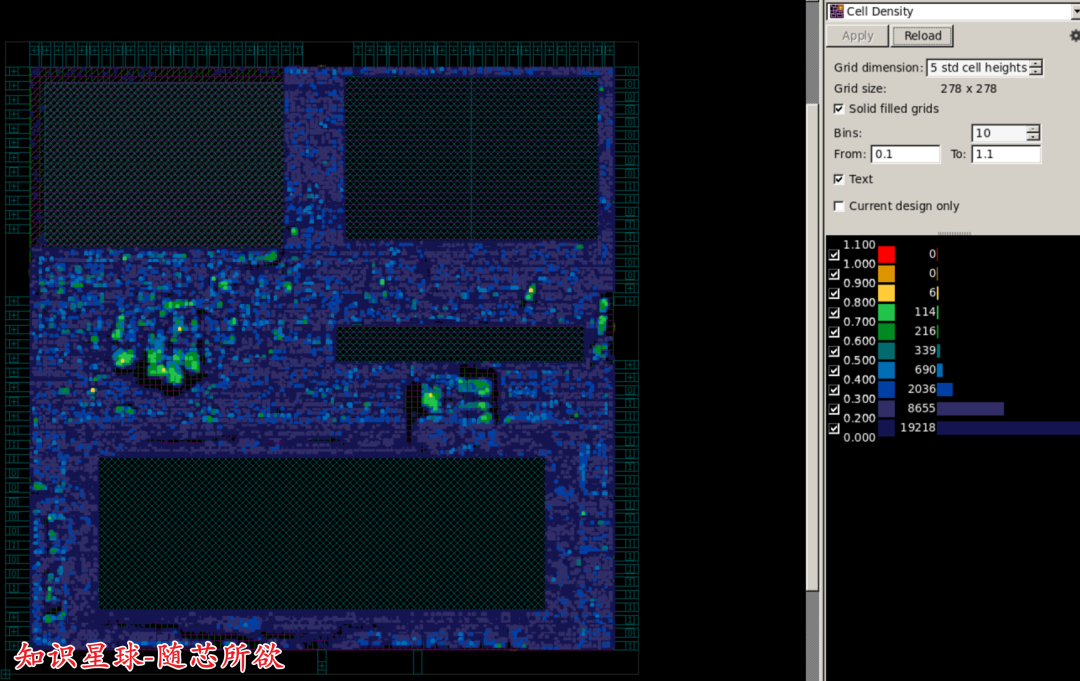

这个是对应的cell density分布图:

尝试了2种解决方案,都是有效的,这里分享一下两种方法以及对应的脚本。

方案1:加Hard placement blockage array

方案1: 在Place之前,在Macro周围要出Pin的地方创建Hard placement blockage array:

对应的tcl脚本:

set site_height [get_attribute [get_core_area] tile_height] set site_width [get_attribute [get_core_area] tile_width] create_placement_blockage_array -coordinate "$core_llx $core_lly $core_urx [expr $core_lly+2000]" -method checker -spacing 10 -height $site_height -width 4 -type hard -snap litho -prefix checkerboard_blkg set ALL_bbox [get_attribute [get_cells xxx/u_ra_m/u_sim_rram_multix4] bbox] # remove placement blockage overlapped with analog macro remove_placement_blockage [get_placement_blockage -within "$ALL_bbox"]

创建Hard placement blockage array的tcl proc分享

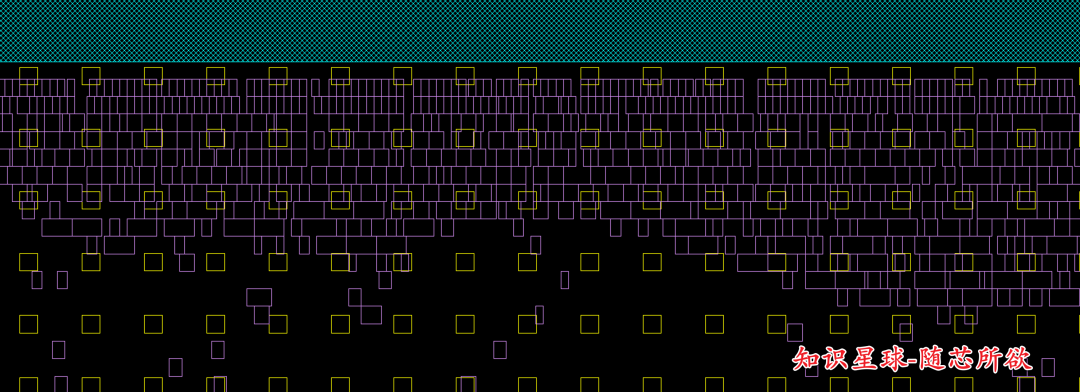

方案1的结果:

CTS之后可以看到Cell的分布散开了挺多,但是彼此之间还是有点拥挤的:

CTS的congestion改善非常多,除了局部有黄色的Congestion(overflow=6的1个,overflow=5的33个)之外其他地方都是可以接受的,如果把blockage的间距和尺寸再减小一点的话会改善更多。

方案2: 加Keepout margin

由于方案1的Cell在hard placement blockage之间的Cell拥挤程度还是蛮高的,所以想到了方案2:在Place之后给Macro周围的Cell加Keepout margin,然后做优化,CTS的时候也会避免把它们靠的太近。

对应的脚本见知识星球

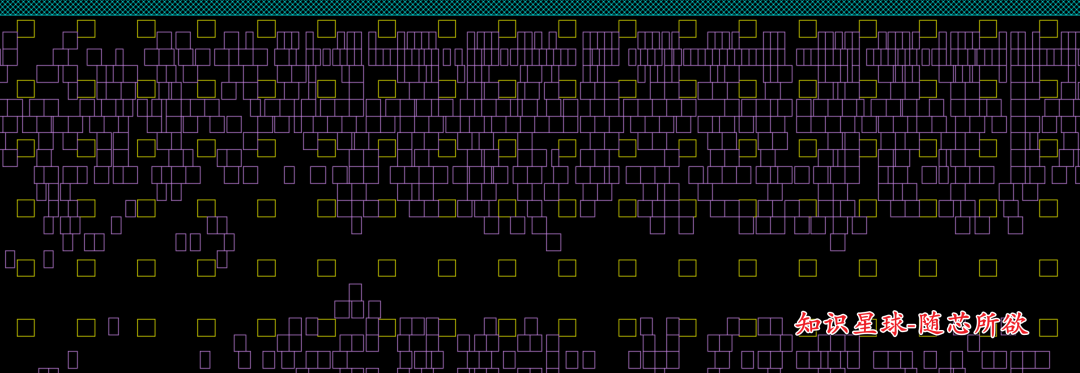

方案2的结果:

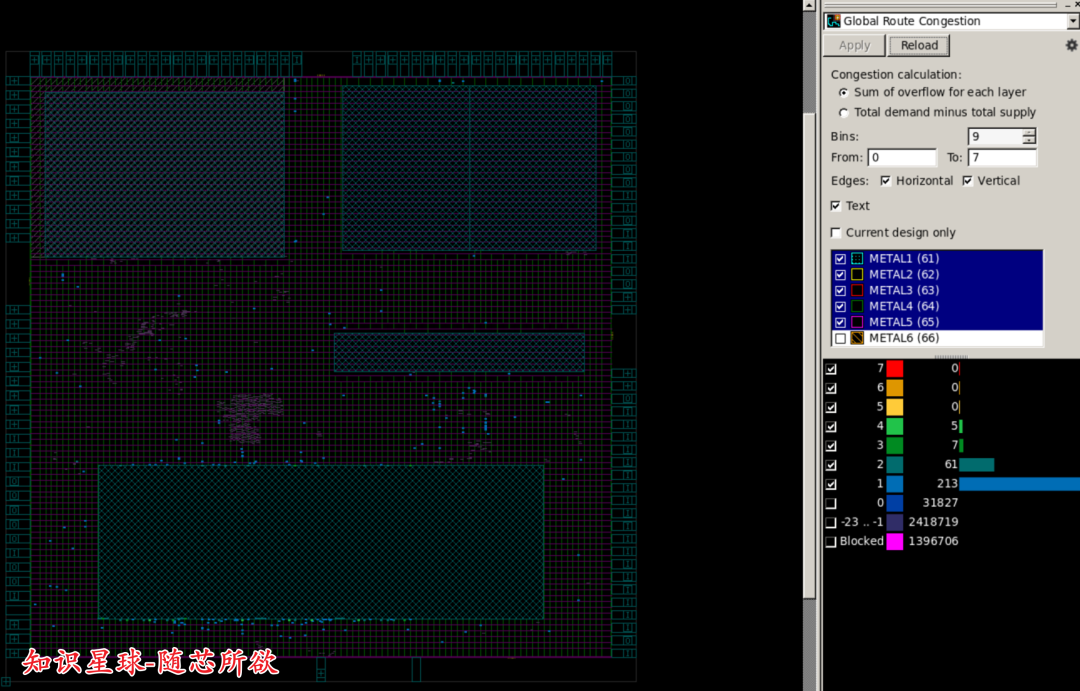

CTS之后的Congestion结果:

可以看到Congestion已经有了很大的改善,这种已经可以接受了。

对应Cell density的分布:

在Macro周围Cell的分布,可以看到Cell分布的非常均匀:

审核编辑:汤梓红

-

linux shell脚本分享2023-02-17 765

-

Linux shell脚本分享2023-07-18 917

-

实例中教你修复晶振2014-03-24 4936

-

ad2013 logo脚本分享!2019-08-20 5528

-

求分享NodeMcu Lua脚本实例2023-04-28 611

-

Design Complexity、congestion、Timing2017-02-08 5824

-

数字后端基本概念介绍——Placement Blockage的9中人为约束2018-01-02 11593

-

VBS脚本实例之一键升级哨位台核心板和底板程序脚本的资料说明2019-05-07 1205

-

如何使用符号执行的python实现攻击脚本分析平台2020-07-16 1266

-

JavaScript常用检测脚本实例代码免费下载2021-02-03 1002

-

109个实用shell脚本分享2022-03-16 3656

-

产生Congestion的主要原因2022-08-18 3086

-

5个shell脚本实例分享2022-12-29 1129

-

PR工具中blockage的定义、分类及其作用2023-12-06 2497

全部0条评论

快来发表一下你的评论吧 !