Vivado怎么避免信号被优化掉

描述

刚写了一段 Verilog代码,辛辛苦苦花了很长时间综合,在debug的过程中,却找不到需要debug的信号了,查看网表发现没有?

这种情况是因为我们的某些中间信号被优化掉了。

被优化掉的原因有可能是你这个信号确实对后面的输出没用,我写的这个项目由于还在中间过程,功能还没有完善,所以不想把大量的中间信号作为输出,所以被优化掉了,以至于在debug过程中找不到这些信号。

如何解决这个问题呢?

很简单,最常用的就是在变量定义的时候添加语句:

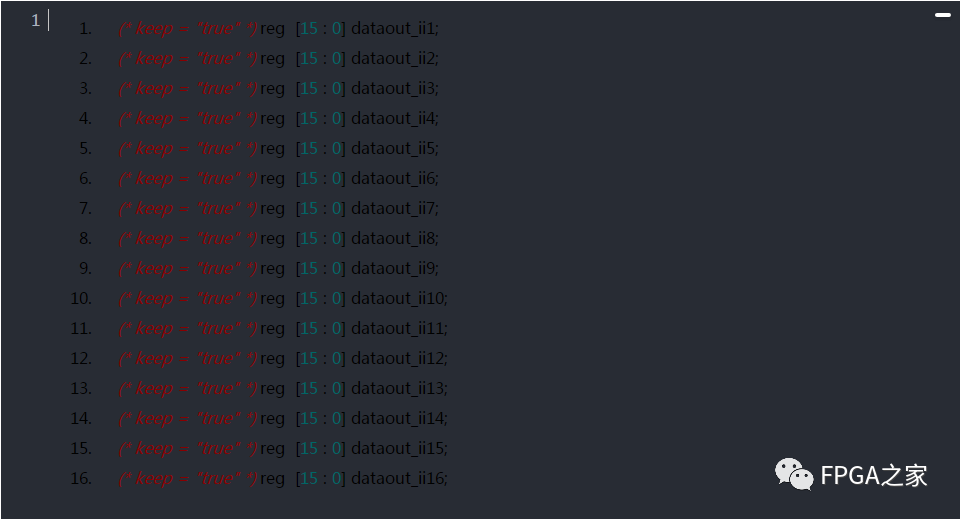

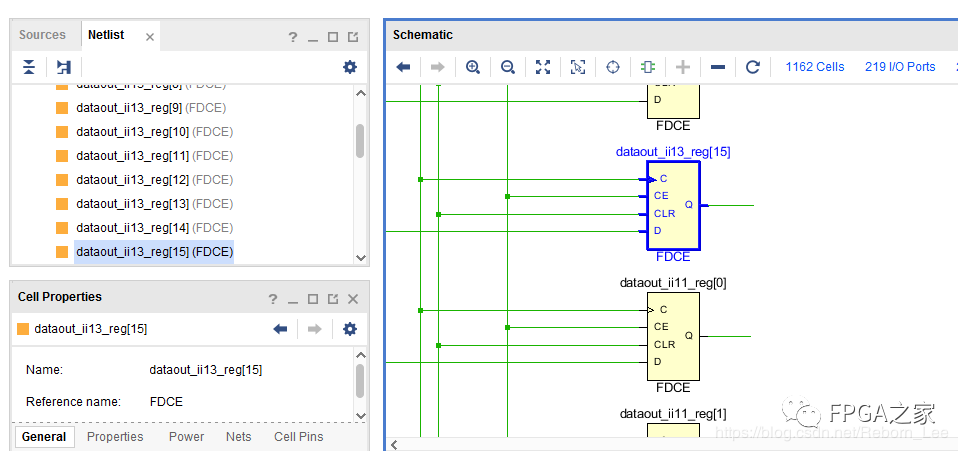

(* keep = "true" *)

例如:

这样即可,从网表中可以找到这些变量了。

当然还有其他办法,例如:

1、 信号前面将keep hierarchy选择yes ,或者选择soft(在综合时保持层次),这样有利于你从模块中找到你想抓取的信号和信号名不被更改。

(* keep_hierarchy = "yes" *)module fre( a, b, c, d);

or

(* keep_hierarchy = "yes" *)fre fre_inst( a, b, c, d);

2、 信号前面使用(* DONT_TOUCH= “{TRUE|FALSE}” *),可以防止信号在综合,以及布局布线的时候被优化掉。

(* dont_touch = "true" *) wire a;

不在话下。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

vivado:时序分析与约束优化2018-08-22 9391

-

如何确保在Vivado实现阶段没有优化逻辑模块资源?2018-10-24 7005

-

请问quartus有类似于vivado * ALLOW_COMBINATORIAL_LOOPS = "true"的关键词吗?2022-01-07 9839

-

CH32V103打开-flto选项后如何避免_write函数被优化掉?2022-05-24 1275

-

今日说“法”:如何防止reg、wire型信号在使用逻辑分析仪时被优化2023-05-16 1025

-

如何避免ADG1419的漏电流对被测电流信号的影响?2023-11-17 844

-

基于FPGA的Vivado功耗估计和优化2017-11-18 8084

-

Vivado防止信号被综合掉的三种方法2018-06-01 14120

-

如何在Vivado中应用物理优化获得更好的设计性能2018-11-23 4709

-

赛灵思Vivado ML版优化应用设计2021-07-02 3726

-

FPGA设计中如何防止信号被优化2023-05-25 5371

-

聊聊寄存器被优化的2种情况2023-09-08 3761

-

Vivado设计套件用户指南之功耗分析和优化2023-09-14 734

-

浅谈寄存器被优化的原因2023-09-26 2493

-

Vivado中IP核被锁定的解决办法2026-02-25 513

全部0条评论

快来发表一下你的评论吧 !