如何把FPGA调试中的数据给捕获出来并保存为文件

可编程逻辑

描述

在FPGA调试过程中,经常遇到这样的情况:出现BUG时,想采用仿真环境把FPGA调试中遇到的BUG给重现出来,但无论怎样改变仿真环境中的激励,都无法重现FPGA上的出现BUG的情况。

此时,如果有一种方法,能够把FPGA正在运行时产生BUG前所有的输入变量状态给捕获下来,然后作为激励,添加到仿真环境中去,这样以来,就能够重现FPGA运行时出现的BUG,就可以在仿真环境中去解决这个BUG,调试的复杂度瞬间降低很多,也能大大的提高FPGA调试的效率。

本文介绍一种利用Vivado进行FPGA调试时,如何把FPGA调试中的数据给“捕获”出来,并保存为文件,转换到仿真环境中进行仿真,“重现”FPGA调试运行场景的方法。

1、背景

从一个RTL代码描述的电路到FPGA样机的过程可以分为两个阶段,第一阶段为仿真验证,第二阶段为FPGA验证。仿真验证是激励数据源常常由自己编写,往往与板级验证数据源(如TestCenter等网络测试仪产生的以太网数据包)存在较大区别,因此在这里介绍一种将板级验证数据导入仿真Testbench中的方法。使用这种方法,可以使仿真验证数据源最大限度地接近板级数据源,可以辅助排除绝大部分的逻辑错误。

2、操作流程

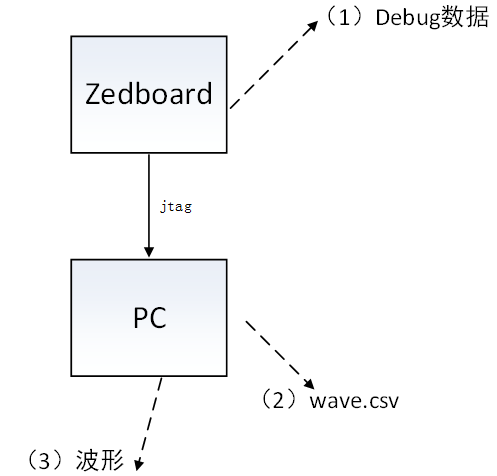

这里我们还以Zedboard Debug数据导出到Testbench为例,对具体实施流程进行介绍,如图1所示,该流程可以分为3个步骤: (1) Zedboard,抓取感兴趣的数据,并通过jtag线传输到上位机; (2) 在上位机Vivado软件的Tcl Console中输入命令,将抓取的数据另存为wave.csv文件; (3) 将wave.csv文件中的数据导入Testbench中,最终输出波形。

图1 操作流程

3、 操作实例

下面给出一个实例,针对图1的三个步骤,对操作流程进行详细介绍。

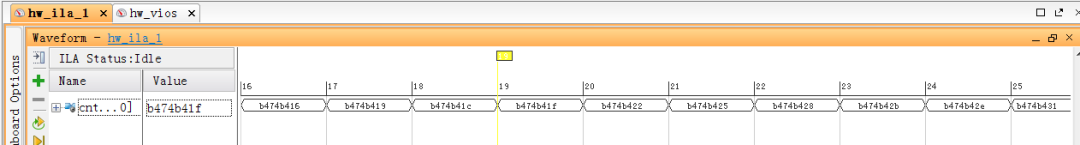

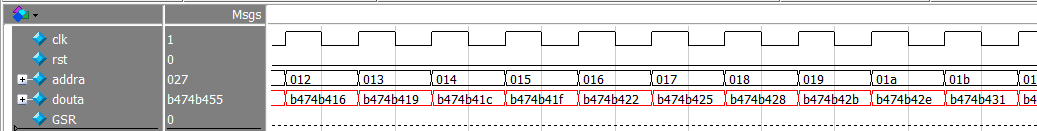

(1) 抓取感兴趣的数据,如图2所示。

图2 抓取感兴趣的数据

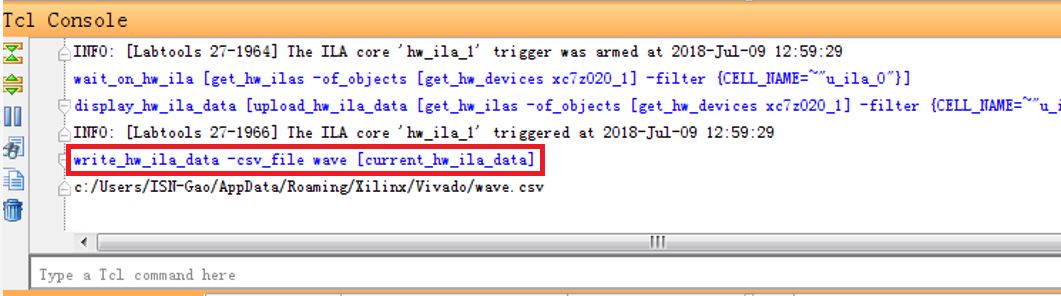

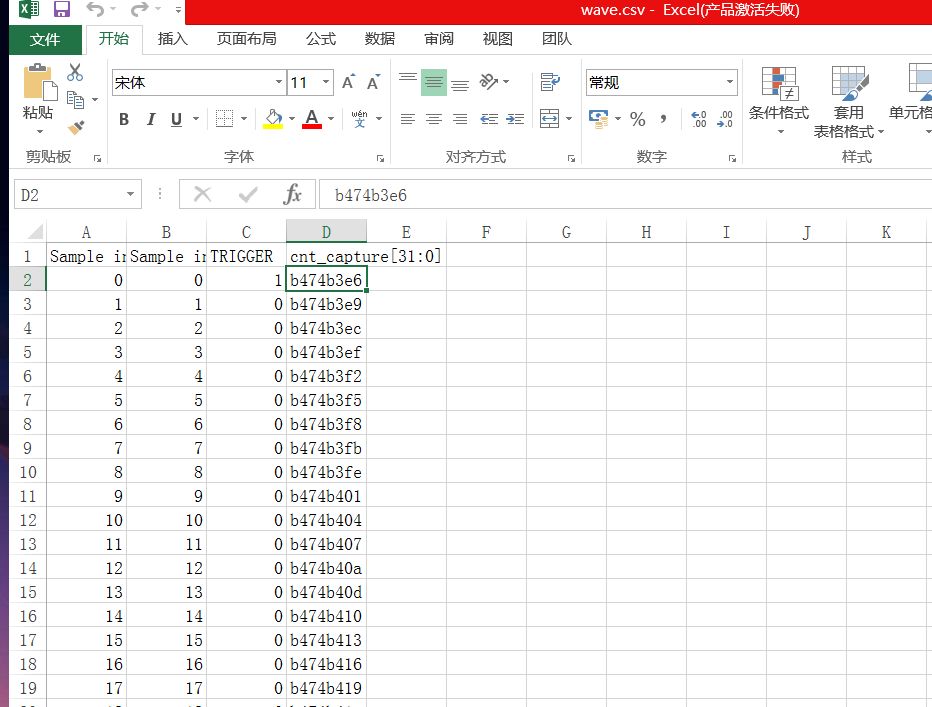

(2) 如图3所示,在tclconsole中输入命令,将抓取的数据转存为wave,csv,转存后的文件如图4所示。

图3 tcl console输入命令

图4 wave.csv文件

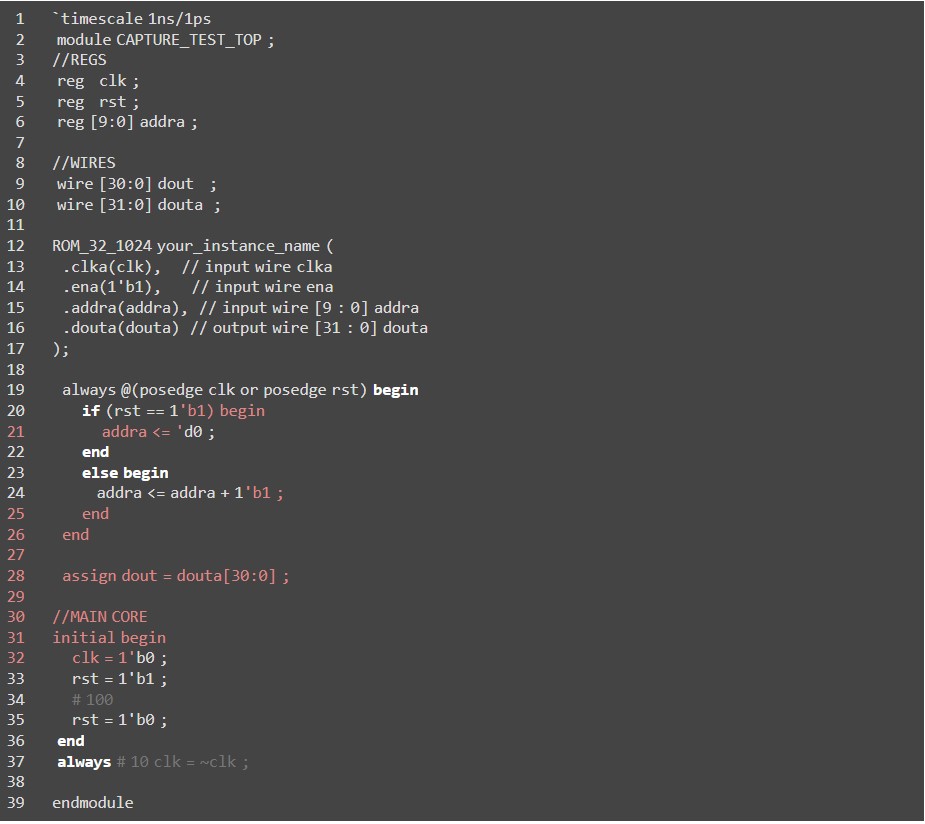

(3)将图4中的数据存入RAM中,并在Testbench中循环读取,获得波形数据,如图5所示。

图5 波形数据

通过这样的方法,就可以把FPGA运行时的输入激励数据捕获到文件中,进而转换到仿真环境中进行调试。

按照惯例,我们给出上述过程的源码。

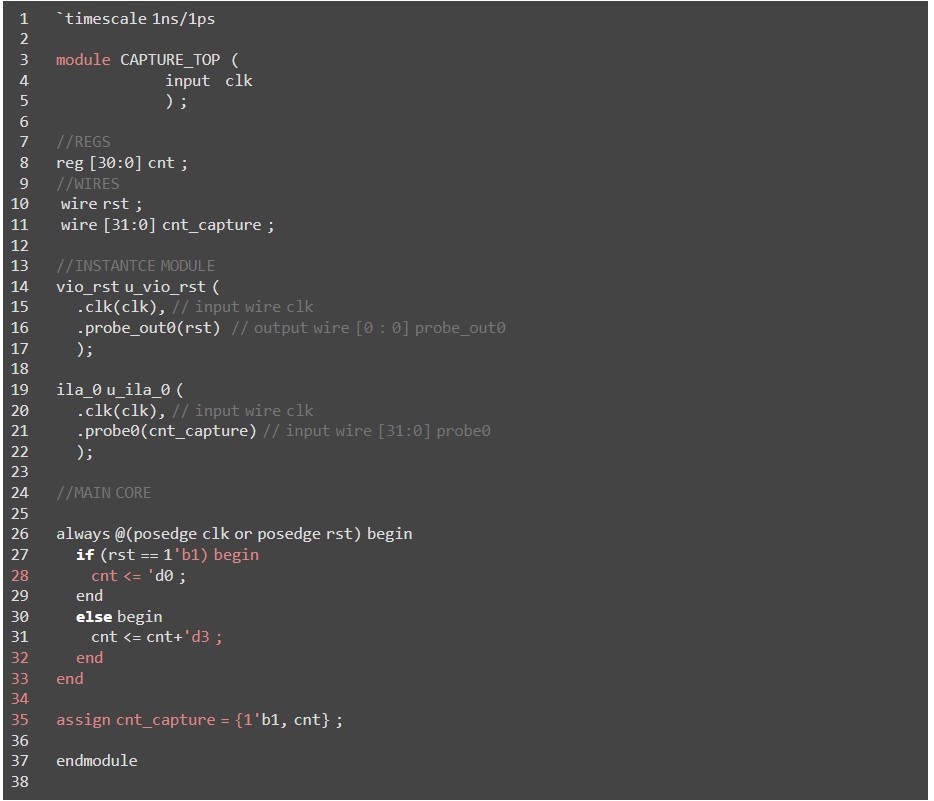

FPGA工程源代码

Zedboard开发板约束文件

仿真环境TESTBENCH文件

审核编辑:刘清

-

ADCPROADS1278EVM-PDK用ADCPro在连续采集模式下能否保存为1个文件?2024-12-02 301

-

labview数据保存为excel文件2023-05-16 8687

-

请问CH32V307可以通过摄像头采集数据并保存为视频文件吗?2022-05-12 1804

-

将framebuffer保存为图片来检查内容正确性2022-04-25 2831

-

程序怎么保存为emf格式?2018-06-07 6423

-

proteus 怎么保存为DSN格式2018-04-26 14819

-

怎么把.bin文件里面的数据读取出来2016-10-14 21976

-

求列表框内容保存为ini文件得操作方法?2016-01-28 3791

-

请问proteus如何保存为低版本的文件?2015-06-20 45834

-

怎样把table保存为txt格式?2014-08-19 2633

-

批量tdms格式保存为excel文件2014-05-12 4163

-

能否把labview采集到的数据,保存为office的exe文档?2013-05-13 2951

-

谁有Labview8.6啊,留个邮箱,帮我把8.6文件保存为8.5,谢谢2012-07-23 4549

-

新手求助:谁有数据保存源程序,最好是保存为excel2012-05-08 2216

全部0条评论

快来发表一下你的评论吧 !