关于TAP控制接口的各状态

接口/总线/驱动

描述

Test Access Port (TAP) 测试访问接口

TAP是JTAG总线的控制接口。

IEEE 标准定义了四个强制的 TAP 信号以及一个可选的 TAP 信号。

TDI (Test Data Input) –用于向目标输入数据的串行数据输入信号

TDO (Test Data Output) – 用于从目标获取数据的串行数据输出信号

TCK (Test Clock) – 用于 JTAG 指令/数据寄存器的测试时钟信号

TMS (Test Mode Select) – 控制 TAP 控制器状态机状态跳变的控制信号

[可选的] TRST (Test Reset) –用于 TAP 控制器的复位信号

TAP Controller 测试访问接口控制器

TAP controller 用于控制 JTAG 接口的行为。

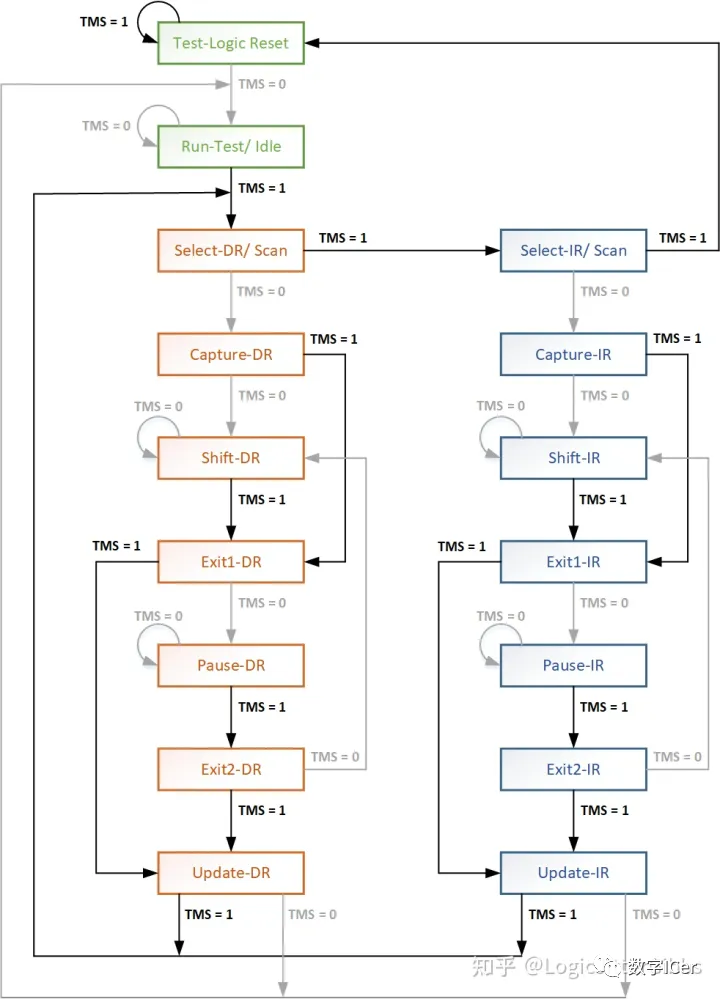

控制器主体是一个拥有 16 个状态的有限状态机(FSM,Finite State Machine),其状态跳变过程由TMS信号控制,如图 2 所示。

TAP 控制器只能在 TCK 的上升沿改变状态,FSM 接下来跳转到哪个状态(next state),由 TMS 的电平以及 FSM 当前的状态(current state)决定。

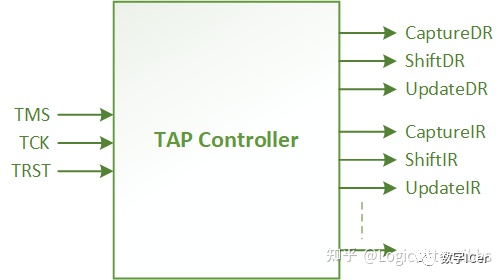

图1- TAP 控制顶层示意图

图 1 展示了 TAP 控制器非常简略的顶层信号示意图,TMS、TCK 以及可选的 TRST 信号输入至 16 状态的状态机,根据当前状态机的状态,产生多个控制信号输出。这些输出控制信号包括指令寄存器(IR)专用的一组控制信号:

CaptureIR

ShiftIR

UpdateIR

同样也为数据寄存器(DR)输出一组专用的控制信号:

CaptureDR

ShiftDR

UpdateDR

以及其他一些控制信号。

图 2- TAP 控制器 FSM 状态转移示意图

以下是关于 TAP 控制各状态的简要介绍:

Test-Logic-Reset: 该状态时,JTAG 电路逻辑会被复位。当可选的 TRST 信号置起时,状态机返回该状态。另外,无论状态机处于何种状态,当 TMS 置为 1 并保持 5 个 TCK 时钟后,均会返回该复位状态。这样以来,即使设计中不存在 TRST 信号,也能够复位 JTAG 电路。

Run-Test/Idle: 该状态用于表示状态机正在等待一些测试项完成。

Select-DR/Scan and Select-IR/Scan: Select-DR/Scan 和 Select-IR/Scan 状态都是临时状态,分别用于初始化选中的 DR 或者 IR 的测试数据序列。

Capture-DR and Capture-IR: 在这个状态中,各个寄存器并行地锁存输入端的数据。

Shift-DR and Shift-IR: 在这个状态中,所需的数据被串行地装填到选中的寄存器中,或者从选中的寄存器中移出。如图 2 所示,TAP 控制器处于这两个状态时,当 TMS 保持为 0 时,FSM 会停留在该状态。在每个时钟周期,单个数据比特被通过 TDI 移入选中的寄存器,同时 TDO 上也会输出从目标寄存器移出的数据。

Exit1-DR and Exit1-IR: 在这个状态中,所有并行装填的数据 (Capture-DR 和 Capture-IR 状态) ,和串行移入的数据 (Shift-DR 和 Shift IR 状态) 都在寄存器中保留。

Pause-DR and Pause-IR: FSM 在该状态中暂时停止,以等待所需的某些外部行为完成。

Exit2-DR and Exit2-IR: 该状态代表在 Pause-DR 和 Pause-IR 状态中暂停的行为将被恢复,TAP 控制器将返回 Shift-DR 或者 Shift-IR 状态,继续移入以及移出数据。

Update-DR and Update-IR: 存储在第一级触发器中的数据将被锁存到第二级触发器,一般所有寄存器中的每个比特都有两级触发器组成,稍后将详细讨论这点。

编辑:黄飞

-

接口的控制与状态寄存器什么作用2024-10-17 2462

-

求助,关于调试TAP3110D2遇到的几个疑问求解2024-10-12 211

-

泰克TEKTRONIX低压单端探头TAP3500的产品特点及其使用方法2024-04-12 1171

-

介绍一种基于任务的异步模式TAP2022-08-19 3557

-

二手TAP2500|泰克TAP2500探头回收2022-01-10 708

-

如何用Signal Tap去调试PCI主设备控制器?2021-04-29 1388

-

硬件接口协议技术:JTAG内部状态机——TAP控制器2020-11-27 21437

-

Tektronix TAP2500探头接口示波器TAP2500有源探头2020-08-07 1050

-

TAP1500/TAP2500回收泰克TAP1500有源探头2020-06-19 845

-

TAP网络分路器的作用2020-02-26 2134

-

JTAG调试接口的四个引脚介绍2019-06-12 5188

-

tap和click事件区别2017-11-28 5612

-

什么是JTAG接口2011-09-21 6084

全部0条评论

快来发表一下你的评论吧 !