电源管理:原理、问题和部件

描述

电源设计人员正在使用灵活的电源监控、排序和调整电路来管理其系统。本文讨论原因和方法。

多年来,对越来越多的电源电压轨进行监测和控制对于电子系统的安全性、经济性、耐用性和正常运行至关重要,尤其是对于采用微处理器的系统。确定电压轨是高于阈值还是在工作窗口内,以及该电压相对于其他电压轨是否以正确的顺序上电或关断,对于操作可靠性和安全性至关重要。

有许多方法可以解决这个问题的各个方面。例如,使用精密电阻分压器、比较器和基准电压源的简单电路可用于确定电源轨上的电压是高于还是低于某个电平。在ADM803等复位发生器中,这些元件与延迟元件相结合,以在上电时保持微处理器、专用IC(ASIC)和数字信号处理器(DSP)等器件处于复位状态。这种级别的监控足以满足许多应用的需求。

在需要监控多个电源轨的情况下,多个器件(或多通道比较器及其相关电路)被并联使用,但越来越多的机会要求监控IC不仅仅是简单的阈值比较。

例如,考虑电源排序的常见要求:FPGA(现场可编程门阵列)制造商可能规定,3.3 V内核电压必须在20 V I/O(输入/输出)电压之前5 ms施加,以避免器件上电时可能造成的损坏。满足这种排序要求对于可靠性而言可能与将器件的电源电压和温度保持在规定的工作限值内一样重要。

此外,许多应用中的电源轨数量也急剧增加。复杂、昂贵的系统,如 LAN 交换机和蜂窝基站,通常具有具有 10 个或更多电压轨的线卡;但即使是对成本敏感的消费类系统,如等离子电视,也可能有多达15个独立的电压轨,其中许多可能需要监控和排序。

许多高性能IC现在需要多个电压。例如,独立的内核和I/O电压是许多器件的标准配置。在高端,DSP可能需要每个器件多达四个独立的电源。在许多情况下,多个多电源器件可以在包含FPGA、ASIC、DSP、微处理器和微控制器(以及模拟组件)的单个系统中共存。

许多器件共享标准电压电平(例如 3.3 V),而其他器件可能需要特定于器件的电压。此外,特定的标准电压电平可能必须在许多地方独立提供。例如,独立的模拟和数字电源,如3.3 V模拟和 3.3 V数字,可能是必需的。为了提高效率(例如,以数百安培运行的存储器轨)或满足排序要求(3.3 V),可能需要多次产生相同的电压一个和 3.3 VB在不同时间由单独的设备需要)。所有这些因素都会导致电压源的扩散。

电压监控和排序可能会变得相当复杂,特别是如果系统必须设计为支持上电时序、省电时序以及对工作期间不同点各种电源轨上所有可能的故障条件的多重响应。中央电源管理控制器是解决此问题的最佳方法。

随着电源电压数量的增加,出现问题的可能性要高得多。风险与电源数量、元件数量和系统复杂性成正比。外部因素也会增加风险。例如,如果在初始设计时主ASIC没有完全表征,则电源设计人员必须致力于硬接线电压监控阈值和时序,这些阈值和时序可能会随着ASIC规范的开发而发生变化。如果要求发生变化,可能需要修改 PC 板,这显然会影响进度和成本。此外,某些器件的电源电压规格在开发过程中可能会发生变化。在这种情况下,一种随时调整电源的方法对任何中央电力系统管理者都是有用的。事实上,监控、排序和调整此类系统的电压轨的灵活性至关重要。

评估所选故障保护和时序的鲁棒性可能是一项艰巨的工作,因此简化此过程的器件将加快电路板评估并缩短上市时间。故障记录和数字化电压和温度数据是有用的功能,无论是在现场还是在从早期PCB开发到原型评估的所有设计阶段。

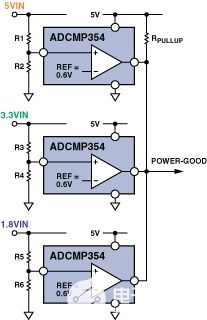

基本监控

图1显示了使用ADCMP354比较器和基准电压源IC监控多个电压轨的简单方法。每个电源轨使用单独的电路。电阻分压器可降低电压轨,为每个电源设置一个欠压跳变点。所有输出连接在一起以产生一个公共电源良好信号。

图1.基于比较器的欠压检测,具有用于三电源系统的通用电源就绪输出。

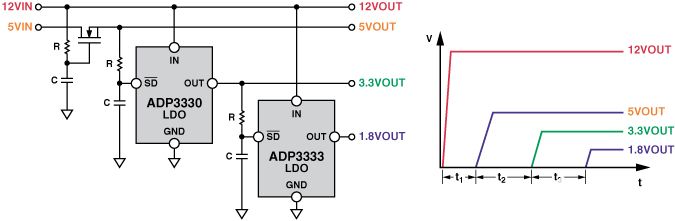

基本排序

图2显示了如何使用分立元件实现基本时序控制,使用逻辑阈值而不是比较器。12V 和 5V 电源轨已在其他地方产生。必须引入时间延迟以确保系统正常运行。这是通过使用电阻-电容 (RC) 组合缓慢斜坡使 n 沟道 FET 上的栅极电压与 5V 电源串联来实现的。选择 RC 值以确保在 FET 达到其电压阈值并开始导通之前有足够的时间延迟。3.3 V和1.8 V电源轨由低压差(LDO)稳压器ADP3330和ADP3333产生。这些电压的导通时间也由RC排序。无需串联FET,因为RC驱动每个LDO的关断(/SD)引脚。选择 RC 值以确保足够的时间延迟 (t2,t3),在 /SD 引脚上的电压攀升到其阈值以上之前。

图2.四电源系统的基本离散时序控制。

这种简单、低成本的电源排序方法占用的电路板面积很小,在许多应用中完全可以接受。它适用于成本是主要驱动因素、时序要求简单且时序电路精度不重要的系统。

但许多情况需要比RC滞后电路更高的精度。此外,这种简单的解决方案不允许以结构化方式处理故障(例如,5V 电源故障最终会导致其他电源轨下降)。

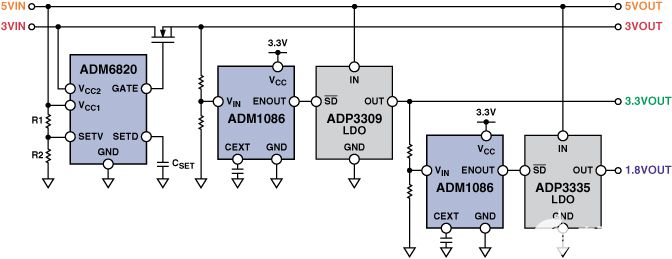

使用 IC 进行排序

图3显示了如何使用ADM6820和ADM1086电源排序IC在类似系统中精确可靠地对电源轨进行时序控制。内部比较器检测电压轨何时超过精确设定的水平。输出在可编程导通延迟后置位,使能ADP3309和ADP3335稳压器按所需顺序排列。阈值由电阻比确定;延迟由电容器建立。

图3.对带有监控IC的四电源系统进行排序。

提供多种电源排序IC。一些器件具有可用于直接启用电源模块的输出,并提供多种输出配置。有些包括板载电荷泵电压发生器。这对于需要对上游产生但缺少高压源(如 12V 电源轨)来驱动 n 沟道 FET 栅极的电源轨进行排序的低压系统特别有用。其中许多器件还具有使能引脚,允许来自按钮开关或控制器的外部信号在需要时重新启动序列或关闭受控电源轨。

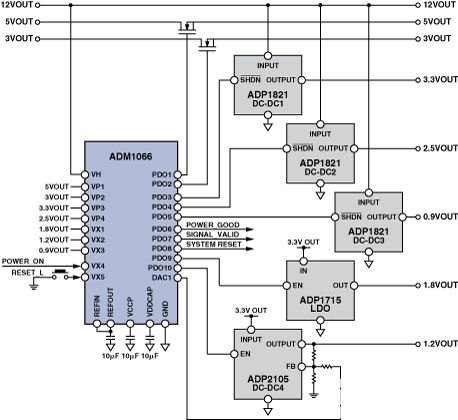

集成电源系统管理

一些系统具有如此多的电源轨,以至于使用大量IC并使用电阻和电容设置时序和阈值电平的分立方法变得过于复杂和昂贵,并且无法提供足够的性能。

考虑一个具有八个电压轨的系统,它需要复杂的上电顺序。必须监控每个电源轨的欠压和过压故障。发生故障时,可以根据故障机制关闭所有电压,或者启动断电序列。必须根据控制信号的状态采取措施,并且必须根据电源的状态生成标志。使用分立器件和简单IC实现如此复杂的电路可能需要数百个单独的元件、大量的电路板空间和巨大的综合成本。

在具有四个或更多电压的系统中,使用集中式设备来管理电源可能是有意义的。这种方法的一个示例如图 4 所示。

图4.适用于八电源系统的集中排序和监控解决方案。

集中监控和排序

这ADM106x超级时序控制器™家庭继续使用比较器,但有一些重要的区别。每个输入专用于两个比较器,因此可以实现欠压和过压检测,从而为ADP1821和ADP2105DC-DC转换器以及ADP1715 LDO创建的电源轨提供窗口监控。欠压故障是电源轨上电前的正常状态,因此此指示用于排序。过压情况通常表示严重故障(例如FET或电感短路),需要立即采取行动。

电源数量较高的系统通常具有更高的复杂性,因此具有更严格的精度限制。此外,在1.0 V和0.9 V等较低电压下,使用电阻设置精确阈值变得具有挑战性。虽然在 10V 电源轨上可以接受 5% 的容差,但在 1V 电源轨上,此容差通常不足。ADM1066允许将输入检波器比较器阈值设置在1%的最坏情况下,与电压(低至0.6 V)无关,并在整个器件温度范围内设置。它为每个比较器增加了内部毛刺滤波和迟滞。其逻辑输入可用于启动上电序列、关断所有电源轨或执行其他功能。

来自比较器组的信息,输入到强大而灵活的载物台机芯中,可用于各种目的:

测 序:当最近使能电源的输出电压进入窗口时,可以触发延时以接通上电序列中的下一个电源轨。复杂的时序,具有多个上电和断电序列,或者上电和断电的序列截然不同。

超时:如果已启用的电源轨未按预期亮起,则可以采取适当的操作过程(例如生成中断或关闭系统)。纯模拟解决方案将简单地挂在序列中的该点。

监测:如果任何电源轨上的电压移出预设窗口,则可以采取适当的行动方案 - 具体取决于发生故障的电源轨、发生的故障类型和当前工作模式。具有五个以上电源的系统通常价格昂贵,因此全面的故障保护至关重要。

板载电荷泵用于产生约12 V栅极驱动,即使最高可用系统电压低至3 V,也允许输出直接驱动串联n沟道FET。附加输出使能或关断DC-DC转换器或稳压器,允许输出在内部上拉至其中一个输入或板载调节电压。输出也可以置位为漏极开路。输出也可用作状态信号,例如电源良好或上电复位。如果需要,状态 LED 可以直接从输出驱动。

供应调整

除了监控多个电压轨并为复杂时序控制提供解决方案外,ADM1066等集成电源管理器件还提供临时或永久调整各个电源轨电压的工具。DC-DC转换器或稳压器的电压输出可以通过调整该器件的微调或反馈节点上的电压来改变。通常,模块输出和接地之间的电阻分压器在微调/反馈引脚上设置标称电压。这反过来又设置了一个标称输出电压。涉及切换额外电阻或控制反馈环路中的可变电阻的简单方案将改变微调/反馈电压,从而调整输出电压。

ADM1066配备数模转换器(DAC),可直接控制微调/反馈节点。为实现最高效率,这些DAC不在地和最大电压之间工作;相反,它们在一个以标称微调/反馈电平为中心的相对狭窄的窗口内工作。衰减电阻的值随DAC的每次LSB变化而缩放功率模块输出的增量变化。这种开环调整提供的裕量增大和裕量减小电平与基准电压源电路中的数字电阻开关所获得的水平相当,并将输出调整到类似的精度。

ADM1066还包括一个用于测量电源电压的12位模数转换器(ADC),因此可以实现闭环电源调整方案。在给定的DAC输出设置下,ADC对电源模块的电压输出进行数字化处理,并在软件中与目标电压进行比较。然后可以调整DAC,以校准电压输出尽可能接近目标电压。这种闭环方案为电源调整提供了一种非常精确的方法。使用闭环方法时,外部电阻的精度完全无关紧要。在图4中,DC-DC4的输出电压由其中一个片内DAC调节。

供应调整方案有两个主要用途。第一种是电源裕量调节的概念,即测试系统对在设备指定电源电压范围的裕量下操作电源的响应。数据通信、电信、蜂窝基础设施、服务器和存储区域网络设备的制造商在交付给最终客户之前,必须对其系统进行严格的测试。系统中的所有电源都将被指定为以一定的容差(例如,±5%,±10%)运行。裕量允许将板载所有电源调整到容差范围的高端和低端,并进行测试以确保正确操作。具有电源调节功能的集中式电源管理器件可用于执行此裕量测试,同时最大限度地减少对额外组件和PCB面积的需求,以执行仅在制造商测试现场进行裕量测试期间只需要一次的功能。

通常需要四角测试,即在设备的工作电压和温度范围内进行测试,因此ADM1062除了闭环电源裕量调节电路外,还集成了温度检测和回读功能。

电源调整方案的第二个用途是补偿现场的系统电源变化。造成这种变化的原因有很多。短期内,电压随着温度的变化而略有变化是很常见的。从长远来看,某些元件值可能会在产品的使用寿命内略有漂移,这可能导致电压漂移。ADC和DAC环路可以定期(例如,每10秒、30秒或60秒)与软件校准环路一起激活,以保持电压保持在应有的位置。

灵活性

ADM1066具有板载非易失性存储器,允许根据需要多次重新编程,同时系统的排序和监控需求在开发过程中不断发展。这意味着硬件设计可以在原型过程的早期完成,并且可以随着项目的进展进行监控和排序的优化。

数字温度和电压测量等功能简化并加快了评估过程。裕量工具将允许在开发周期中调整电压轨。因此,如果关键的ASIC、FPGA或处理器也在开发中,并且随着新芯片修订版的发布,电源电压电平或排序要求处于不断变化的状态,则可以通过软件GUI进行简单的调整。因此,电源管理器件可以在几分钟内重新编程,以考虑这些变化,而无需物理更改电路板上的组件,或者更糟糕的是重新设计硬件。

结论

电压轨数量的增加和电源排序的出现提高了对各种设备和系统的电源设计人员的要求,从笔记本电脑、机顶盒和汽车系统到服务器和存储、蜂窝基站以及互联网路由和交换系统。更严格的测试程序、更高水平的信息收集以及快速简单的可编程性也令人感兴趣,尤其是在中高端系统中。为了提高鲁棒性和可靠性,并增加这些重要的新功能,有许多新的电源管理集成电路可用于帮助安全、高效、最小电路板面积解决这些问题,同时缩短上市时间。

审核编辑:郭婷

-

智能零部件管理助力中电思仪的标准化管理2025-02-14 6098

-

电源管理芯片怎么判断好坏2023-09-06 7395

-

电源管理ic零部件是什么2023-02-21 1238

-

常用的电源管理ic有哪些2023-02-18 7777

-

电源管理#芯片jf_97106930 2022-08-27

-

B03_01电源管理 概述#电源管理系统硬件工程师Lukou 2022-08-01

-

电源管理基础知识电源管理基础知识电源管理基础知识2017-09-15 1767

-

电源管理芯片使用中的特性2015-10-08 3271

-

数字电源管理技术及电源管理总线2011-02-15 681

-

电源管理,电源管理是什么意思2010-03-23 1949

全部0条评论

快来发表一下你的评论吧 !