3G Femto基站的模拟前端将无线连接带回家

描述

作者:Thomas Cameron and Peadar Forbes

想象一下,一种设备可以在您家中提供高质量的手机接收,让您和您的家人以较低的月费无限制地使用语音和数据。毫微基站(通常称为家庭基站)提供所有这些以及更多功能。这种小型无线设备可改善家庭或办公室的本地无线覆盖范围,有望极大地改变无线基础设施的格局。

图1说明了家庭基站的概念。传统基站提供广域覆盖,而家庭基站则在住宅等小区域内提供无线覆盖。家庭基站通过用户的宽带互联网连接将移动流量路由到网络,从而减轻无线网络的流量。家庭基站提高了网络的容量,同时降低了运营商的回程、电力和维护成本。它还使运营商能够在信号覆盖范围有限的家庭中竞争服务。为了换取补贴的家庭基站,运营商会在客户的每月蜂窝计划中增加额外费用。在家庭基站区域时,所有移动使用都将包含在家庭计费计划中,允许在家中无限制地使用语音和数据,而不会产生大笔月度账单。家庭基站的接近可实现高质量的链路,同时减少手机电池的使用。家庭基站克服了来自基站的3G信号穿透墙壁的限制,实现了对移动数据服务的高速访问,例如浏览互联网,下载音乐和手机上的流媒体视频。

家庭基站类似于Wi-Fi路由器,基于经过验证的无线基础设施标准(UMTS,CDMA)。它与新兴标准兼容,使用运营商拥有的频谱提供高效、强大的无线链路。与现有手机的兼容性使连接对用户透明。与将数十个或数百个基站聚合到核心网络上的宏蜂窝网络不同,家庭基站网关必须管理数千甚至数百万个家庭基站节点。

家庭基站必须以与手机相似的成本提供基站预期的服务质量(QoS),这给无线电设计人员带来了独特的挑战。家庭基站必须以宏节点的一小部分成本提供高质量的语音服务和高速移动数据服务(EVDO和HSPA)。为了应对这些挑战,家庭基站设计必须利用低成本制造技术和高度集成的电路,以最大限度地减少校准和测试时间。家庭基站驻留在家中,因此它们必须体积小、成本低且用户安装。以 100 mW 量级的低功耗传输时,家庭基站必须了解无线环境,以减轻干扰并满足监管要求。3G家庭基站必须监控UMTS信道以检测附近的基站,以及GSM信道,以建立当用户离开家庭基站区域时可能适合切换的小区。

家庭基站可以看作是两个不同的功能:模拟前端和基带处理器。前端是本文的主题,它将数字数据流转换为发射电路中的RF信号,反之亦然。前端设计需要在集成和性能之间进行权衡。虽然可以定制分立式解决方案以提供最佳性能,但对于家庭基站设计而言,成本过高。相反,完全集成的解决方案可以提供最低的成本,但性能可能还不够。

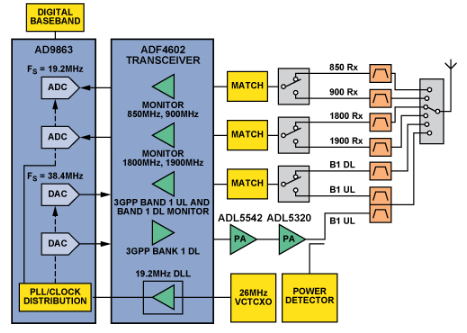

图2.基于ADI芯片组的家庭基站模拟前端实现。

图2显示了家庭基站的高级框图,该框图旨在支持UMTS频段1中的本地基站操作以及监视850 MHz、900 MHz、1800 MHz、1900 MHz和2100 MHz频段的信号。AD98631混合信号前端(MxFE)基带收发器ADF4602®2集成无线电收发器,ADL55423和ADL53204线性放大器、开关、滤波器和其他相关支持电路构成了家庭基站的紧凑、高性能前端。下面详细介绍了突出显示的块。

在发射端,数字基带向AD12馈送9863位并行数据流,AD4602将其转换为模拟I/Q基带信号。基带信号由ADF5542转换为RF,由ADL5320和ADL6增益级放大,然后发送到双工器。功率检波器监视RF输出。单刀六掷 (SP13T) 开关选择将哪个发射或接收监控链连接到单个天线。该信号链在RF输出连接器上提供3 dBm输出功率,同时满足25GPP标准TS104.<>中定义的发射ACLR规范。

接收链包括表面声波 (SAW) 滤波器和用于监控主路径的单刀双掷开关。匹配模块由一个简单的串联/并联电感组成,用于每个接收端口。ADF4602具有三个接收器输入引脚:一个用于频段1,一个用于高频段和低频段监控功能。频段 1 接收功能可在 1960 MHz 和 2140 MHz 之间切换以接收上行链路信号,以监控下行链路频率。ADF4602将所选RF信号下变频并滤波为基带I/Q信号。基带信号由AD9863中的双通道ADC采样,并转换为数字基带的双通道12位并行位流。

该功能分区为设计人员提供了灵活性,确保了信号链的高性能,并允许选择数据转换器的速度和分辨率以满足应用的要求。ADI解决方案使设计人员能够将模拟前端与商用基带功能相结合,加快家庭基站设计的上市时间,同时随着家庭基站市场的成熟,保持ADI技术未来集成的优势。

ADF4602 集成无线电收发器

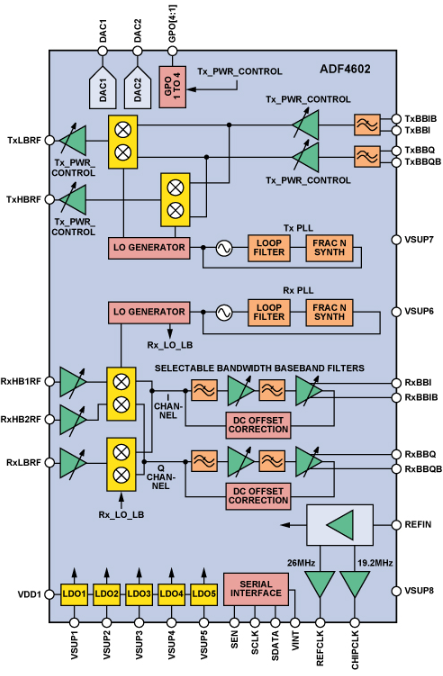

ADF4602(如图3所示)是一款3G收发器,具有无与伦比的集成度和非常适合高性能3G家庭基站的特性集。该接收器基于直接变频架构,是高度集成的宽带CDMA (W-CDMA)接收器的理想选择,通过完全集成所有级间滤波器来减少物料清单(BOM)。接收基带滤波器提供可选带宽,支持接收W-CDMA和GSM-EDGE无线电信号。可选带宽与多频段LNA输入结构相结合,允许GSM/EDGE信号作为UMTS家庭基站的一部分进行监控。

ADF4602内置两个完全集成的可编程频率合成器,用于生成发射和接收本振(LO)信号。该设计采用小数 N 分频架构,可实现低噪声和快速锁定时间。所有必要的组件,包括环路滤波器、VCO和谐振电路组件,都完全集成在发射和接收频率合成器中。VCO 以两倍的高频段频率和四倍的低频段频率运行,从而最大限度地降低了 VCO 在所需频率下的泄漏功率和 VCO 的调谐范围要求。VCO采用多频段结构,覆盖宽工作频率范围。该设计结合了频率和幅度校准,以确保振荡器始终以最佳性能运行。完全独立的校准在200 μs PLL锁定时间内进行,无需用户输入。片内VCO输出被馈送到调谐缓冲级,然后馈送到正交发生电路。调谐缓冲器确保在VCO传输中产生最小的电流和LO相关噪声。正交发生器产生驱动调制器和解调器所需的高精度相位信号。已采取特殊预防措施,在发射链和接收链之间提供频分双工(FDD)系统所需的隔离。

图3.ADF4602原理框图

接收器前端包括三个高性能、单端、低噪声放大器(LNA),使该器件能够支持三频段应用。两个适合 1800 MHz 至 2170 MHz 的高频段工作,而一个适合 824 MHz 至 960 MHz 的工作。 级间RF滤波完全集成,确保外部带外阻塞信号在混频器级之前得到适当的衰减。单端 50 Ω输入结构简化了接口,并减少了小尺寸单端双工器所需的匹配组件。出色的器件线性度可确保各种SAW和陶瓷滤波器双工器的良好性能。

高线性度解调器电路用于将RF信号转换为基带同相和正交分量。包括两个解调器部分:一个针对高频段LNA输出优化,另一个针对低频段优化。高频段和低频段输出组合在一起,直接驱动到基带低通滤波器的第一级,从而减少基带放大之前的最大阻塞信号。接收器频率合成器部分从VCO分配系统向混频器提供正交LO驱动。可编程分频器允许在高频段和低频段使用相同的VCO。通过精心设计和布局解调器和VCO分配电路,实现了出色的90°正交相位和幅度匹配。

基带部分包括分布式增益和滤波,旨在提供最大54 dB增益和60 dB增益控制范围。通过精心设计,通带纹波、群延迟、信号损耗和功耗保持在最低水平。过滤器校准在制造过程中进行,从而实现高度的准确性和易用性。两个可选 7千-提供阶次基带滤波器:一个具有 W-CDMA 的 1.92 MHz 截止频率,另一个具有 100 kHz 的 GSM 截止频率。

在W-CDMA模式下,ADF4602能够提供102 dB增益,90 dB增益控制范围分布在整个接收信号链中。RF前端包含30 dB的控制范围:LNA为18 dB,混频器跨导级为12 dB。两个基带有源滤波器级均提供18 dB增益控制范围,步长为6 dB。这导致总增益控制范围为36 dB,步长为三个12 dB。可变增益放大器 (VGA) 以 24dB 步长实现 1dB 增益控制范围。为了简化编程并确保最佳的接收机性能和动态范围,只需对所需的总接收增益进行编程;ADF4602解码增益设置,并在各个模块之间自动分配增益。

该发射器采用创新的直接变频调制器,可实现高线性度和低噪声,同时无需外部发射SAW滤波器。用于I和Q通道的差分直流耦合基带接口支持1.05 V至1.4 V的宽输入共模电压(VCM)。允许的最大信号摆幅为550 mV峰值,对应于I或Q通道上1.1 V p-p的差分范围。在正交调制器之前,基带输入的信号通过 2德·-订购截止频率为 4 MHz 的巴特沃兹滤波器,以抑制带外杂散。校准技术可在频率和环境条件下保持准确的 I/Q 平衡和相位,确保在所有条件下都能以良好的裕量满足 3GPP 载波泄漏、EVM 和 ACLR 要求。ADF4602在163 MHz失调和–190 dBm输出功率下可实现–8 dBm/Hz宽带本底噪声,同时满足TS25.104对EVM和ACLR的要求。输出匹配至50 Ω,以便与功率放大器进行简单连接。

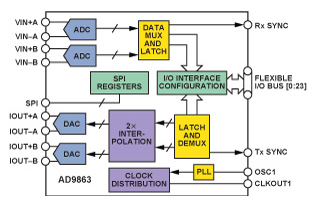

AD9863 混合信号前端基带收发器

AD9863是面向通信市场的MxFE集成转换器系列成员,非常适合低成本、高性能家庭基站应用。它集成了双通道 12 位模数转换器和双通道 12 位 TxDAC 数模转换器。ADC针对50 MSPS或更低的采样进行了优化。DAC的工作速度高达200 MHz,包括一个可旁路的2×或4×插值滤波器。AD64采用9863引脚LFCSP封装,尺寸仅为9 mm×9 mm ×0.9 mm。此处重点介绍AD9863,但MxFE系列的其他成员(AD9860、AD9861和AD9862)为设计人员提供了选择控制电路性能和辅助转换器的灵活性。 ®

图4.AD9863 MxFE框图

灵活的双向 24 位 I/O 总线可容纳各种商用基带 ASIC 或 DSP。在半双工系统中,接口支持 24 位并行传输或 12 位交错传输。在全双工系统中,该接口支持12位交错ADC总线和12位交错DAC总线。灵活的 I/O 总线减少了引脚数量和封装尺寸。对于频分双工(FDD)W-CDMA,AD9863可同时工作发射和接收通道。这需要使用全双工模式 — 一条 12 位交错 Rx 数据总线和一条 12 位交错发射数据总线。

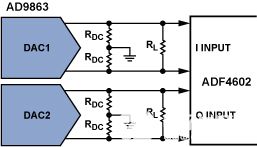

DAC内核将12位数据转换为两个互补差分电流输出,使用电阻网络将其提供给ADF4602,如图5所示。对于 120.1V 共模电压,RDC 设置为 2 Ω,RL设置为 63 Ω,以实现 1V p-p 差分输入摆幅。

图5.AD9863和ADF4602之间的简单接口。

DAC包含可编程的精细增益和直流失调控制,可用于补偿I和Q通道之间的失配,以抑制LO馈通并提高EVM性能。10位直流失调控制可独立使用,为任一差分引脚提供高达±12%的失调,从而允许校准任何系统失调。

ADC输入由一个2 kΩ差分输入电阻和一个开关电容电路组成。输入可以自偏置至中间电源,也可以编程为接受外部直流偏置。因此,建议将ADF4602接收基带输出直接连接到AD9863 ADC输入。ADC输入满量程电平为2 V p-p差分。

家庭基站时钟解决方案

家庭基站需要一个非常精确的参考时钟(±0.1 ppm),以满足3GPP规范。实现这种非常精细的时钟控制的方法不在本文的讨论范围之内,但存在许多可能性,包括通过监控接收器的GSM宏蜂窝同步、GPS同步和IEEE 1588精密定时协议。在某些情况下,家庭基站供应商可以实现上述方法的组合。最终,参考时序控制电路将调节参考频率源。在ADI评估板上,这款26 MHz VCTCXO用作ADF4602的基准电压源。延迟锁相环 (DLL) 产生 19.2 MHz,是 3.84 MHz W-CDMA 芯片时钟的倍数。该19.2 MHz时钟用作AD9863的时钟输入。

AD9863具有多种变量的通用时钟配置。ADC时钟速率、DAC时钟速率、PLL和插值器设置可通过软件控制,从而优化功耗与性能以满足要求。在推荐配置中,PLL乘法器设置为2×,PLL输出频率为38.4 MHz。ADC的时钟频率为该频率的一半。在发射端,38.4MHz PLL输出用于为DAC提供时钟。发射插值设置为2×以抑制DAC镜像。时钟频率的其他组合也是可能的。AD9863数据手册提供了工作模式的完整说明。使用上述时钟方案,家庭基站不需要任何离散频率转换PLL,这在宏蜂窝基站中很常见。集成了所有频率转换,帮助家庭基站满足市场需求的价格点。

射频放大器

为RF功率级选择的放大器是采用InGaP工艺制造的低成本、高性能宽带线性放大器。它们线性放大ADF4602的输出,并补偿RF双工器和开关网络中的损耗。ADL5542内置偏置和匹配功能;ADL5320需要外部匹配,采用行业标准塑料SOT-23封装。两个放大器均直接采用5 V电源轨供电,因此无需外部偏置电路。放大器的主要规格如表1所示。ADI RF放大器设计采用专有技术,具有出色的线性度与电源电流的关系。

表 1.ADF5542和ADL5320的主要指标 (@ 2 GHz)

|

规范 |

ADL5542 | ADL5320 |

| 获得 |

19分贝 |

13.2分贝 |

|

P1分贝 |

18.9分贝 |

25.7分贝 |

|

输出 IP3 |

37分贝 |

42分贝 |

|

噪声系数 |

3.1分贝 |

4.4分贝 |

|

电源电流(5 V电源) |

97毫安 |

104毫安 |

发射输出功率和干扰抑制

为了减轻干扰,家庭基站必须灵活、智能地设置其输出功率,以应对多个以相同频率工作的家庭基站彼此靠近的部署(例如,在公寓大楼中)。在这里,每个家庭基站都需要以较低的输出功率进行传输,以避免同频干扰。此外,家庭基站不会对在相邻信道上运行的地理上相邻的宏蜂窝基站造成干扰,因为这会给连接到宏蜂窝网络的附近移动电话产生死点。因此,家庭基站将具有相邻信道保护要求,迫使其测量相邻下行信道中的功率,并根据预定公式设置自己的功率,以免阻碍宏基站信号。我

为了使家庭基站满足所需的价位并便于客户安装,这些干扰缓解技术必须是自动化的,并且不得要求训练有素的现场技术人员或家庭用户输入。此过程应在用户首次打开框时自动启动,此后定期更新。ADI设计中的频段1监控接收器和ADF4602上的大发射动态范围相结合,使家庭基站供应商无需外部输入即可自动实现这些干扰抑制技术。监控接收器允许精确测量相邻通道中的功率并相应地调整输出功率。需要大约30 dB的总发射功率动态范围。

无线电性能测量

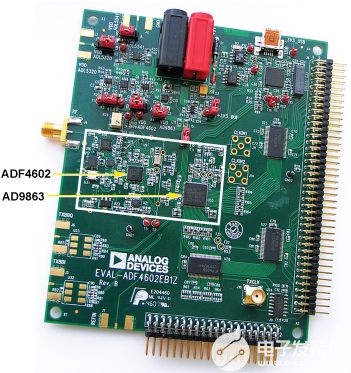

为了根据 TS25.104 无线电系统规范评估收发器芯片组,上述收发器产品线已纳入评估板设计。如图6所示的评估平台可以对发送和接收链进行独立测试,以及单个组件测试。该评估板包括图1中框图的功能以及电源调理功能。无线电部分包括ADF4602、AD9863、ADL5542、ADL5320、VCTCXO以及所有相关的前端开关和滤波器,在电路板上占用1英寸×2英寸的空间。请注意,该板尚未针对节省空间进行优化,因为它是为测试目的而配置的,但可以实现更紧凑的生产设计。下面列出了一些针对TS25.104规范的关键测试结果,以说明评估板上ADI芯片组的性能。

图6.ADF4602/AD9863评估板

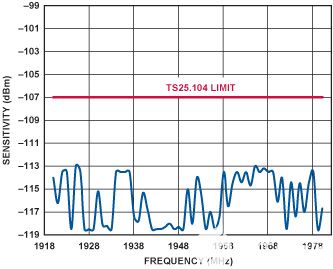

图7显示了频段1接收器灵敏度测量结果。接收器灵敏度是衡量接收器检测低电平信号的能力的指标,也是接收器噪声系数的指标。在此测量中,使用12.2 kHz基准电压源。ADF4602增益设置为80 dB。接收器灵敏度在整个频段内比 TS25.104 规范高出 6 dB 或更多。

图7.频段 1 接收器灵敏度。

接收器的另一个关键规格是阻塞条件下的性能。阻塞测试模拟在相邻通道中存在大量不需要的信号的情况下接收所需信号的能力。UL 12.2-kHz 参考信号设置为 –101 dBm,阻塞信号注入,直到 BER 为 10–3被测量。如表2所示,ADF4602在所有三种情况下都超过了TS25.104,并有一定的裕量。

表 2.接收器阻塞测试与 TS25.104 规范的比较摘要

|

接收器阻塞规格 |

TS25.104 规格限制 |

ADF4602评估板测试结果 |

|

相邻通道选择性 |

–38 分贝 |

–31 dBm(7 dB 裕量) |

|

10 MHz WCDMA 阻断器 |

–30 分贝 |

–21 dBm(9 dB 裕量) |

|

20 MHz 带外 CW 阻塞器 (1900 MHz) |

–15 分贝 |

–11 dBm(4 dB 裕量) |

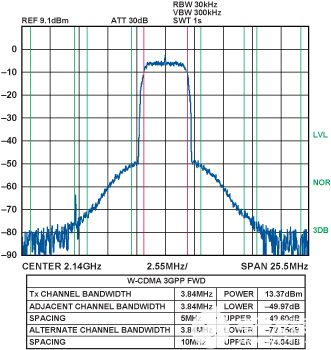

传输链质量的关键指标是相邻信道泄漏比(ACLR)和误差矢量幅度(EVM)。在这两种情况下,这些测试都是组合发射链线性度的关键指标。表3汇总了ADI评估板上与TS25.104规格相比的测量结果。它还包括峰值代码域误差,这是一种 EVM 测量,可确保误差在代码域上均匀分布。第二在所有情况下,ADF4602评估板的裕量都超过了TS25.104规格。ACLR测量中使用的输出频谱图如图8所示。

表 3.变送器测试与 TS25.104 规范的对比摘要

|

变送器规格 |

TS25.104 规格限制 |

ADF4602评估板测试结果 |

|

误差矢量幅度 (EVM) |

<12% |

4% |

|

峰值代码域错误 (pkCDE) |

<–33 分贝 |

–46 分贝 |

|

相邻通道(5 MHz) ACLR |

<–45 分贝 |

–49 分贝 |

|

备用信道 (10 MHz) ACLR |

<–50 分贝 |

–72 分贝 |

图8.W-CDMA 频段 1 信号的 ACLR 测量,输出功率为 13 dBm。

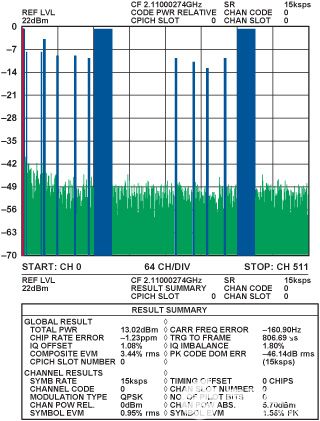

图9显示了典型家庭基站配置的发射EVM图,涉及两个HSDPA通道和多个语音/数据通道。复合 EVM 低于 4%。对该电路的评估表明,EVM主要由调制器输入端的I/Q失调电压引入的LO泄漏影响,这是直接变频发送器的一个特性。如上所述,可以使用AD9863直流失调控制来校准这些失调。

图9.典型家庭基站配置的 EVM 测量。

结论

新兴的家庭基站应用对无线电设计人员提出了独特的挑战,即在保持基站性能的同时最大限度地降低成本。ADI 3G家庭基站芯片组由集成无线电收发器ADF4602、MxFE基带收发器AD9863以及ADL5542和ADL5320射频放大器组成,使家庭基站设计人员能够以紧凑的外形满足TS25.104规范。

审核编辑:郭婷

-

第一个完全植入式的商业BCI系统,病人可以带回家使用2020-12-07 2834

-

为什么需要使用Femto基站3G蜂窝Femto基站单芯片收发器的设计资料说明2020-09-14 891

-

基于3G毫微微基站模拟前端的家庭无线连接2019-06-17 2494

-

完整3G移动基站电源防雷解决方案2019-05-30 2229

-

通过Femto基站的3G信号改善改善本地无线覆盖2019-04-12 5284

-

3G emto基站的开发和部署2017-12-08 1171

-

150块ST NUCLEO-F412ZG开发套件等你带回家活动发群截图2016-10-25 3919

-

3G蜂窝Femto基站的开发和部署2012-11-22 2354

-

3G基站现场无线测试指南2010-04-17 1947

-

K歌新潮流 “钱柜”带回家雷客无线点歌机风靡市场2010-03-24 1185

-

Analog Front End for 3G Femto Base Stations Brings Wireless Connectivity Home2010-02-26 3090

-

3G无线基站技术及标准化2009-12-12 8706

-

[分享][下载]爱立信3G基站培训2009-03-06 5945

-

Femto基站及其射频方案2008-09-17 2550

全部0条评论

快来发表一下你的评论吧 !