为逐次逼近型ADC设计可靠的数字接口

描述

逐次逼近型模数转换器因其逐次逼近寄存器而称为SAR ADC,适用于需要高达18位分辨率和高达5 MSPS的应用。它们的优点包括体积小、功耗低、无流水线延迟和易于使用。

主机处理器可以通过各种串行和并行接口(如SPI、I)访问或控制ADC2C 和 LVDS。本文讨论可靠集成数字接口的设计技术,包括数字电源电平和时序、导通期间的I/O状态、接口时序、信号质量以及数字活动引起的误差。

数字I/O电源电平和顺序

大多数SAR ADC提供独立的数字I/O电源输入V。IOASNW驾驶,这决定了接口的工作电压和逻辑兼容性。该引脚应与主机接口(MCU、DSP 或 FPGA)电源电压相同。数字输入通常应在DGND − 0.3 V和V之间IO+ 0.3 V,避免违反绝对最大额定值。具有短走线的去耦电容应连接在V之间IO引脚和 DGND。

采用多个电源工作的ADC可能具有明确定义的上电时序。应用笔记AN-932:电源排序为这些ADC的电源设计提供了很好的参考。为避免正向偏置ESD二极管并在未知状态下为数字内核上电,请在接口电路之前打开I/O电源。模拟电源通常在I/O电源之前上电,但并非所有ADC都是如此。阅读并遵循数据手册,以确保顺序正确。

开启期间的数字 I/O 状态

为了正确初始化,某些SAR ADC需要某些逻辑状态或序列来实现数字功能,例如复位、待机或关断。在所有电源稳定后,施加指定的脉冲或组合,以保证ADC在预期状态下启动。例如,RESET时需要至少50 ns的高脉冲,才能将AD7606配置为上电后正常工作。

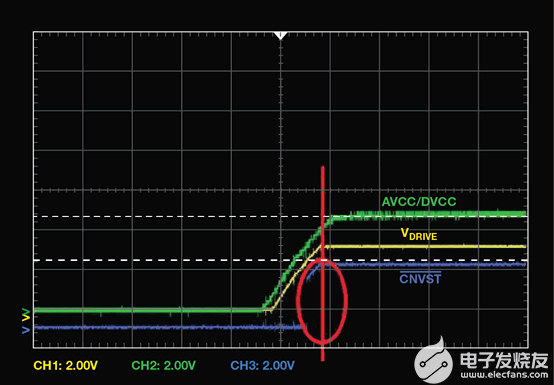

在完全建立所有电源之前,不应切换任何数字引脚。对于SAR ADC,转换起始引脚CNVST可能对噪声敏感。图 1 显示了一个示例,其中主机 cPLD 将 CNVST 调高,而 AVCC、DVCC 和 V驾驶仍在加速。这可能会使AD7367处于未知状态,因此主机应保持CNVST低电平,直到电源完全建立。

图1.在电源斜坡上升期间将CNVST调高可能会导致未知状态。

数字接口时序

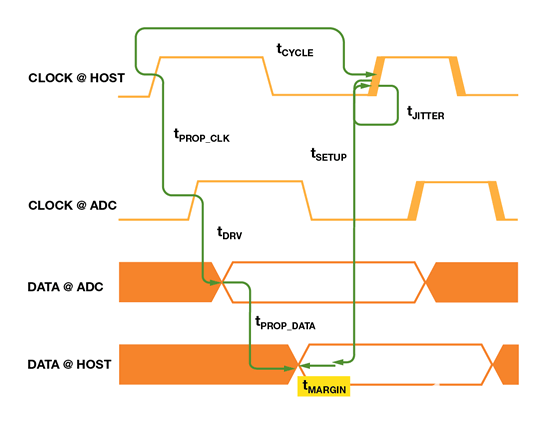

转换完成后,主机可以通过串行或并行接口读取数据。要正确读取数据,请遵循特定的时序策略,例如SPI总线使用哪种模式。不要违反数字接口时序规范,尤其是ADC和主机的建立和保持时间。最大比特率由整个周期决定,而不仅仅是指定的最小时钟周期。图2和以下公式显示了如何计算建立和保持时序裕量的示例。主机将时钟发送到ADC,并从ADC读取数据输出。

图2.设置并保持时序裕量。

t周期= t抖动+ 吨设置+ 吨PROP_DATA+ 吨PROP_CLK+ 吨.DRV+ 吨边缘

t周期: 时钟周期 = 1/f时钟

t抖动:时钟抖动

t设置:主机设置时间

t拿:主机保持时间

tPROP_DATA:沿传输线从ADC到主机的数据传播延迟

tPROP_CLK:沿传输线从主机到ADC的时钟传播延迟

t.DRV:时钟上升沿/下降沿后的数据输出有效时间

t边缘:保证金时间,≥0表示满足设置时间或保持时间;< 0 表示未满足设置时间或保持时间。

主机的设置余量为

tMARGIN_SETUP = tCYCLE, min – tJITTER – tSETUP – tPROP_DATA – tPROP_CLK – tDRV, MAX

设置时间方程根据最大系统延迟项定义最小时钟周期时间或最大频率。它必须≥ 0 才能满足时序规格。增加周期(降低时钟频率)以处理过多的系统延迟。对于总线上的缓冲器、电平转换器、隔离器或其他附加组件,将额外的延迟添加到PROP_CLK和 tPROP_DATA.

同样,主机的保持保证金为

tMARGIN_HOLD = tPROP_DATA + tPROP_CLK + tDRV – tJITTER – tHOLD

保持时间公式定义了最小系统延迟要求,以避免由于保持违规而导致的逻辑错误。它必须≥ 0才能满足时序规格。

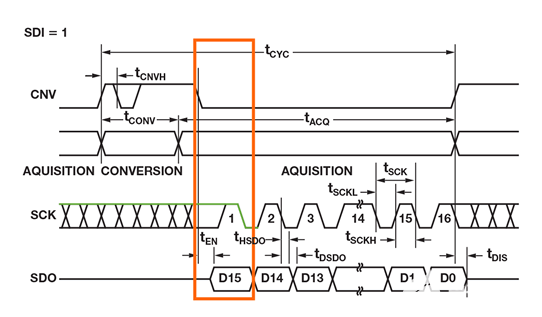

许多带有SPI接口的ADISAR ADC从CS或CNV的下降沿为MSB提供时钟,而其余数据位则遵循SCLK的下降沿,如图3所示。读取 MSB 数据时,在方程中使用 <> 而不是 t.DRV.

图3.AD7980 3线CS模式的SPI时序

因此,除了最大时钟速率外,数字接口的最大工作速度还取决于建立时间、保持时间、数据输出有效时间、传播延迟和时钟抖动。

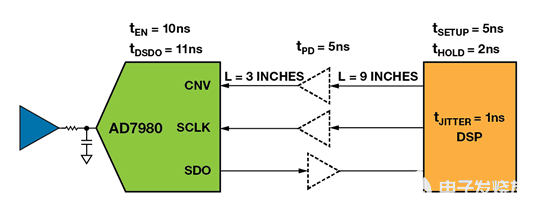

图4显示DSP主机在7980线CS模式下访问AD3,V.IO= 3.3 V.DSP将SDO信号锁存于SCLK的下降沿。DSP 指定 5 ns 最短建立时间和 2 ns 最短保持时间。对于典型的 FR-4 PC 板,传播延迟约为 180 ps/in。缓冲器的传播延迟为5 ns。CNV、SCLK 和 SDO 的总传播延迟为

t支柱= 180 ps/英寸×(9 英寸 + 3 英寸)+ 5 纳秒 = 7 纳秒。

t抖动= 1 ns。主机以 30 MHz 的频率运行 SCLK,因此周期= 33 ns。

tSETUP_MARGIN= 33 ns − 1 ns – 5 ns – 7 ns – 11 ns – 7 ns = 2 ns

tHOLD_MARGIN=11 ns + 7 ns + 7 ns – 1 ns – 2 ns = 22 ns

建立裕量和保持裕量均为正裕量,因此SPI SCLK可以在30 MHz下运行。

图4.DSP和AD7980之间的数字接口

数字信号质量

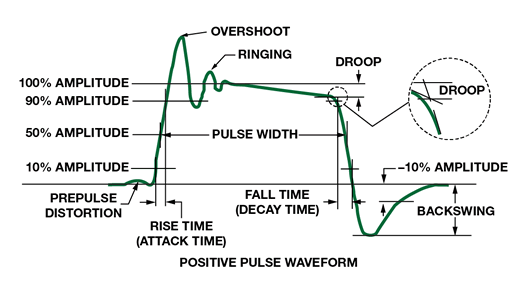

数字信号完整性,包括定时和信号质量,确保信号:以指定的电压电平接收;不要互相干扰;不要损坏其他设备;并且不污染电磁频谱。信号质量由许多术语指定,如图5所示。本节将介绍过冲、振铃、反射和串扰。

图5.信号质量的通用规格。

反射是阻抗不匹配的结果。当信号沿走线传播时,每个接口的瞬时阻抗都会发生变化。部分信号将反射回来,部分信号将继续向下。反射会在接收器上产生过冲、下冲、振铃和非单调时钟边沿。

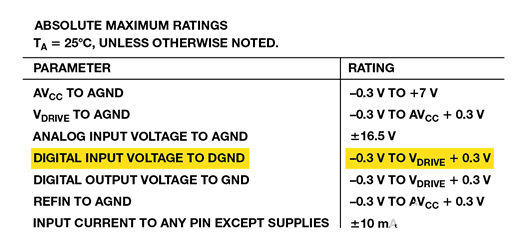

过冲和下冲会损坏输入保护电路或缩短IC的使用寿命。图6显示了AD7606的绝对最大额定值。数字输入电压应介于 –0.3 V 和 V 之间驾驶+ 0.3 V.此外,V以上振铃伊利诺伊州最大值或以下 VIH最小值可能会导致逻辑错误。

图6.AD7606的绝对最大额定值

要最大程度地减少反射,请执行以下操作:

使跟踪尽可能短

控制走线的特性阻抗

消除存根

使用适当的终止方案

使用环路面积小的实心金属作为返回电流参考平面

使用较低的驱动电流和压摆率

许多软件工具或网络可用于计算走线的特性阻抗,例如 Polar Instruments Si9000 PCB 传输线场求解器。通过选择传输线型号并设置介电类型和厚度、走线宽度、厚度和间隔等参数,可以轻松获得特性阻抗。

IBIS是一种新兴标准,用于描述IC数字I/O的模拟行为。布局前仿真可检查时钟分布、芯片封装类型、电路板堆叠、网络拓扑和端接策略。它还可以检查串行接口时序约束,以指导放置和布局。后仿真验证设计是否满足所有准则和约束,并检查反射、振铃和串扰等违规行为。

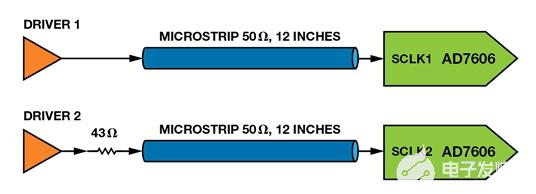

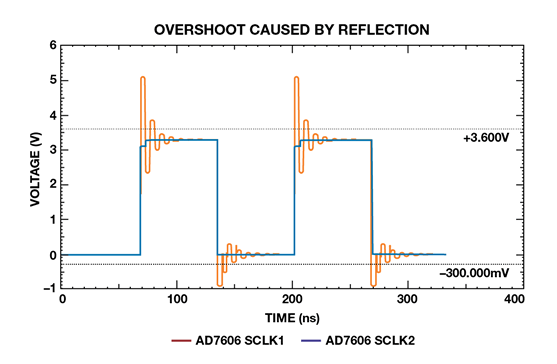

图7显示了一个驱动器通过1英寸微带线连接到SCLK12,另一个驱动器通过与微带串联的2 Ω电阻连接到SCLK43。

图7.驱动AD7606 SCLK。

图8显示了SCLK1上的大过冲,违反了–0.3 V至+3.6 V绝对最大额定值。串联电阻降低了 SCLK2 上的压摆率,使信号保持在规格范围内。

图8.AD7606 过冲的IBIS模型仿真

串扰是通过互电容(电场)或互感(磁场)在平行传输线之间耦合能量。串扰量取决于信号的上升时间、平行线的长度以及它们之间的间距。

控制串扰的一些常见做法是:

增加行距

最小化并行运行

使走线靠近参考金属平面

使用适当的终止方案

降低信号压摆率

数字活动导致的性能下降

数字活动会降低SAR ADC的性能,由于嘈杂的数字接地或电源、采样时钟抖动和数字信号干扰,SNR会降低。

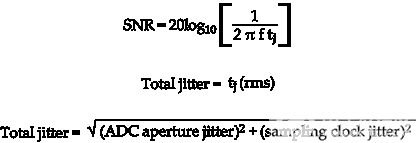

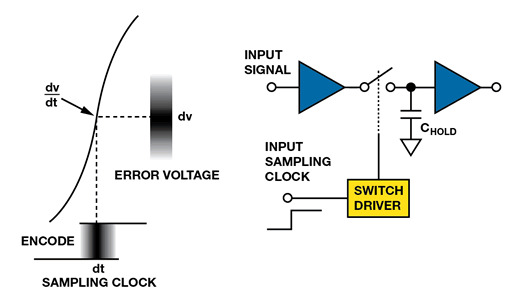

孔径或采样时钟抖动设定了SNR的限值,特别是对于高频输入信号。系统抖动来自两个来源:片内采样保持电路的孔径抖动(内部抖动)和采样时钟上的抖动(外部抖动)。孔径抖动是采样时间内的转换间变化,是ADC的函数。采样时钟抖动通常是主要的误差源,但两种来源都会导致不同的模拟输入采样时间,如图9所示。它们的影响是无法区分的。

总抖动产生误差电压,ADC的总SNR受以下限制

其中,f 是模拟输入频率,tj 是总时钟抖动。

例如,对于10 kHz模拟输入和1 ns总抖动,SNR限制为84 dB。

图9.采样时钟抖动引起的误差电压。

数字输出切换引起的电源噪声应与敏感的模拟电源隔离。分别对模拟和数字电源进行去耦,特别注意接地返回电流路径。

高精度SAR ADC对数字接口上的活动很敏感,即使电源已正确去耦和隔离。突发时钟通常比连续时钟性能更好。数据手册通常显示接口不应处于活动状态时的安静时间。在这些时间(通常是采样时刻和发生关键位决策时)最大限度地减少数字活动在更高的吞吐率下可能具有挑战性。

结论

仔细注意数字活动,以确保SAR ADC的有效转换。数字引起的误差可能会使SAR ADC进入未知状态,导致故障或降低性能。本文应帮助设计人员调查根本原因并提供解决方案。

审核编辑:郭婷

-

为逐次逼近型ADC 设计可靠的数字接口2023-11-03 212

-

12位逐次逼近型ADC转换的原理是什么2022-02-25 1758

-

关于为逐次逼近型ADC 设计可靠的数字接口原理2021-04-02 1931

-

MT-021:ADC架构II:逐次逼近型ADC2021-03-21 1265

-

为逐次逼近型 ADC 设计可靠的数字接口2019-10-18 2087

-

逐次逼近型ADC的基本原理分析与讲解2019-04-23 15579

-

给逐次逼近型ADC设计可靠的数字接口2018-10-17 1813

-

逐次逼近型ADC的原理2018-03-19 27201

-

如何为逐次逼近型ADC设计可靠的数字接口?2016-01-21 11216

-

为逐次逼近型ADC设计可靠的数字接口2016-01-04 757

-

什么是逐次逼近型adc2009-05-08 833

-

解析逐次逼近ADC2009-05-04 522

-

理解逐次逼近型ADC2009-04-16 945

全部0条评论

快来发表一下你的评论吧 !