I2C_CLK容性负载导致access失败问题总结

电子说

1.4w人已加入

描述

像这样的事情几乎每周都在发生,

前天是MDX access fail,今天是I2C fail。

因为做的次数多了,就成了熟练工,想起我刚工作前几周每隔几天都要问公司的前辈,我这I2C怎么又不通了...今天通了,明天又不通了。

故障现象:

I2C 接口访问reg不通。

Part 02

DEBUG过程:

三板斧,直接量I2C/SDA对地IO阻值,clk 几K、sda几M,没有太大异常,因为有上下拉电阻。

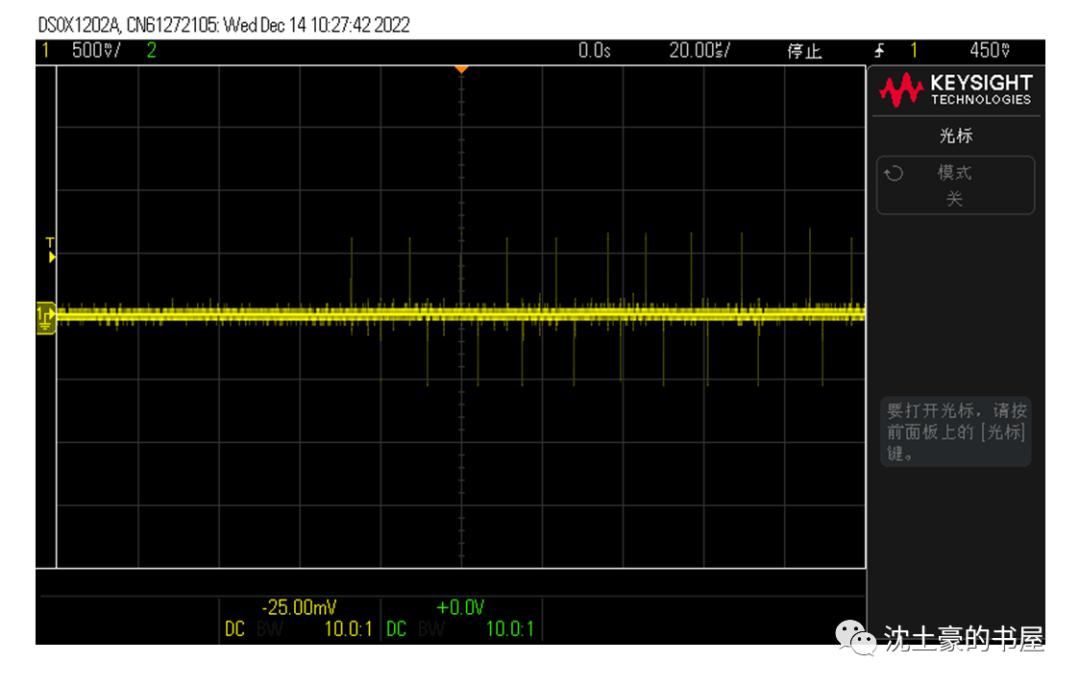

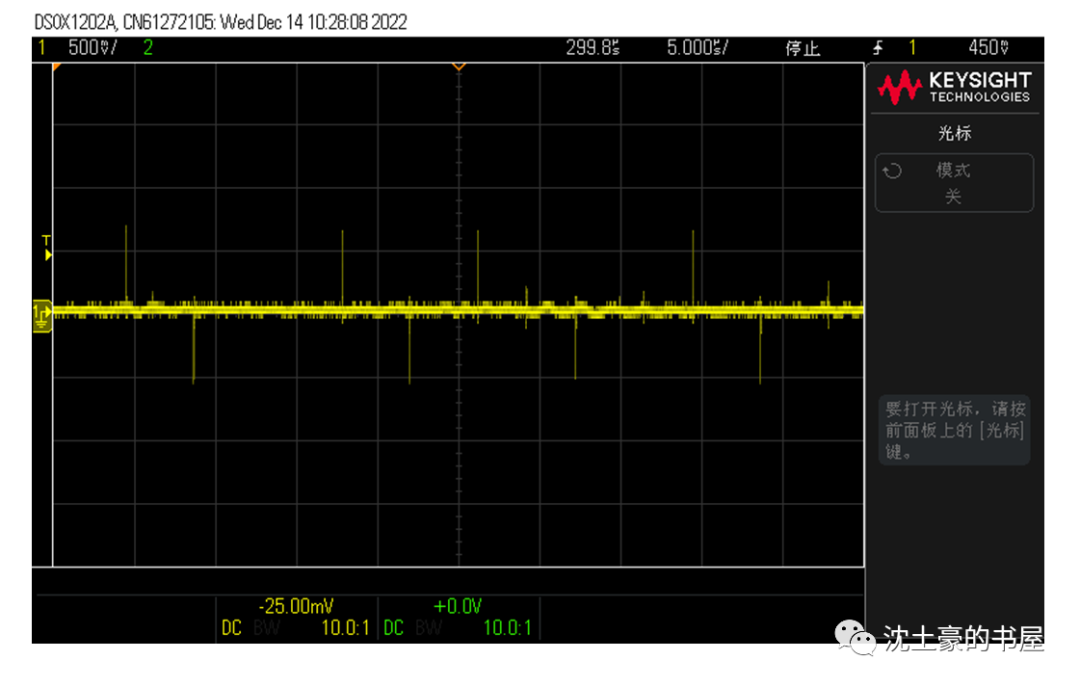

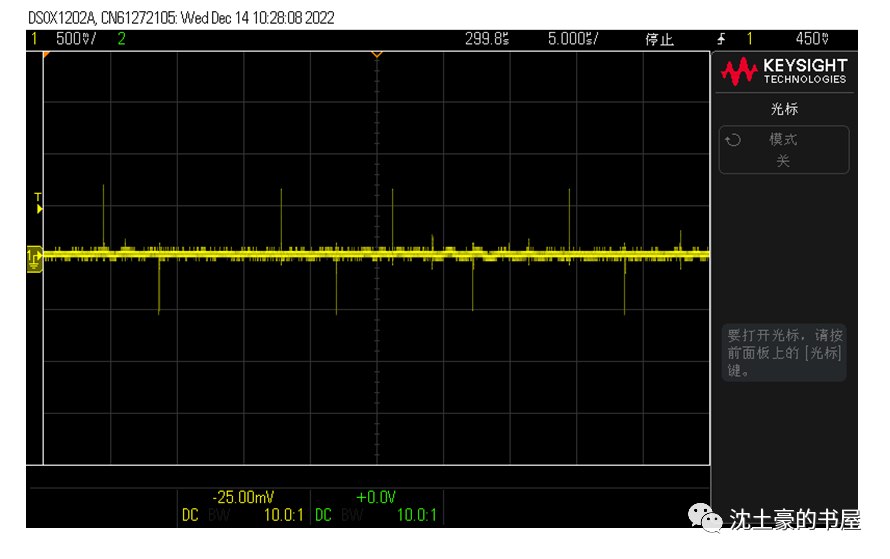

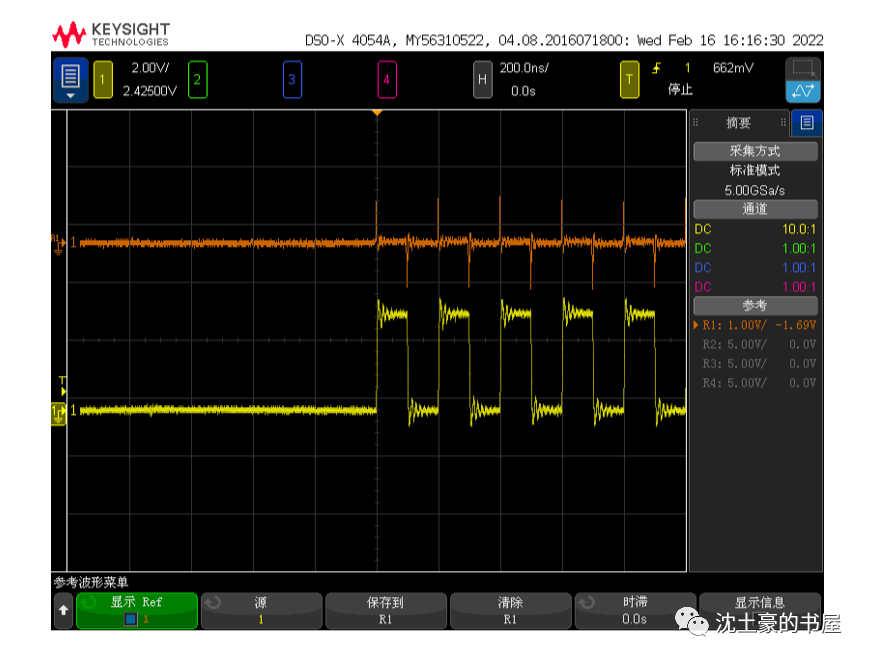

然后直接量示波器波图,很明显它“羊”了。

放大看一下,这些上下脉冲,其实就是clk的正负边沿

Part 03

因为有先前 [debug04]GPIO对地短路问题 的经验,波图极其相似。

我们这次直接给出结论:

CLK信号 drive不动,看波图疑似clock对地短路/存在较大容性负载。

查PCB背后贴了大电容(巨大,uF级)。拆除电容,故障恢复,结题~

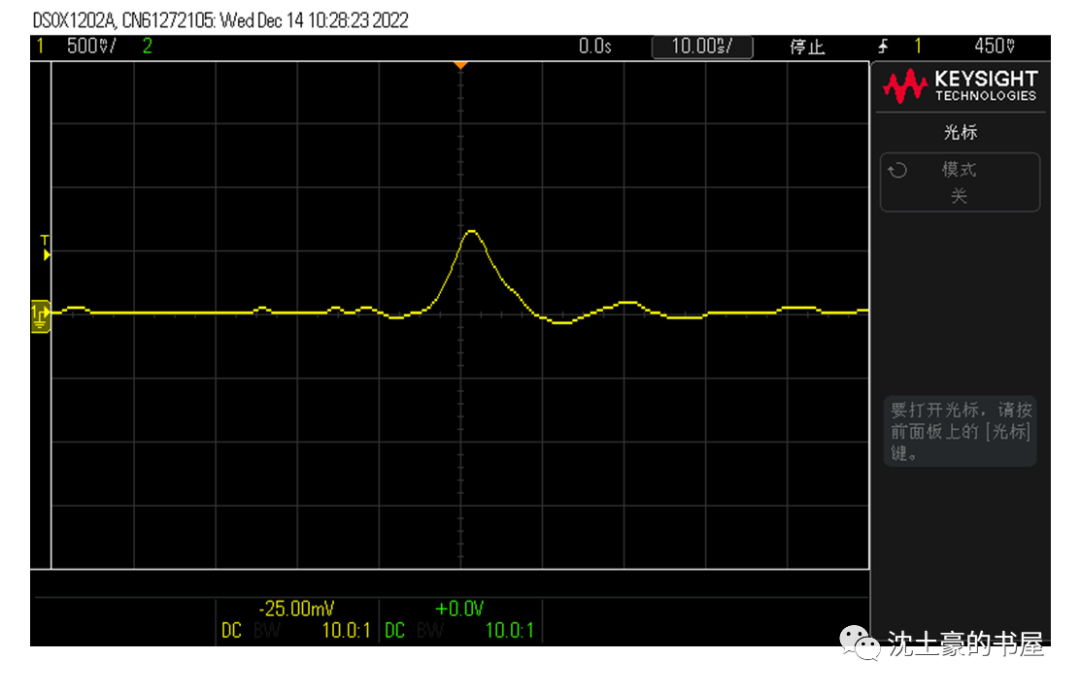

我们可以对比下2种case,短路/容性负载下的波图差异:

大容性负载:

短路:

我做下猜测:

clk跳变沿,短路的脉冲更窄,容性负载应当脉冲更宽,谁更容易产生振铃?打个问号

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

I2C通信开发障碍以及总结2023-04-17 2518

-

什么是容性负载箱?2024-09-25 4060

-

AC to DC电源容性负载,为什么AC电压输入小时容性负载也小?2013-09-10 3093

-

电源的容性负载是什么?2017-11-26 14042

-

关于ADA4807-2的容性负载问题2018-08-09 3258

-

容性负载对电源有什么影响?2019-10-17 8288

-

解析DDR设计中容性负载补偿的作用2023-05-16 1063

-

求助,关于ADA4807-2的容性负载问题2023-11-17 561

-

什么是容性负载2010-06-09 8846

-

I2C资料总结2017-08-16 920

-

阻性负载、感性负载、容性负载的区别2021-04-27 43943

-

I2C_CLK容性负载导致access失败怎么解决2023-02-01 1968

-

什么是容性负载、阻性负载和感性负载 阻性负载有哪些用电器2024-02-06 13118

-

led灯是容性负载还是感性负载2024-09-19 10940

-

感性负载,容性负载,阻性负载介绍2025-02-10 8705

全部0条评论

快来发表一下你的评论吧 !