单芯片数字立体声子系统

描述

AD1859在单芯片上提供业界功能最完整的16/18位立体声数字音频播放子系统。它将串行数字输入数据转换为滤波、缓冲、低失真、增益控制的立体声模拟输出。其异步主时钟数字锁相环(DPLL)允许其接受来自各种来源的数据,时钟速率为28 kHz至52 kHz(使用外部27 MHz晶体),抑制采样时钟抖动并大大简化了接口。

它是许多应用的理想选择,包括数字有线电视和直播卫星机顶解码盒、视频 CD 播放器、CD-I 播放器、高清电视、数字音频广播接收器、数字音频工作站、多媒体计算机以及各种形式的 CD 和数字磁带播放器。

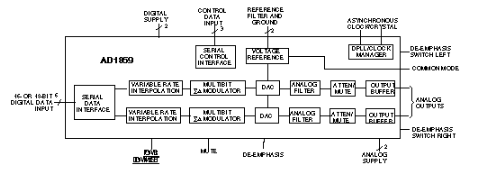

单芯片AD1859包括(图1)可变速率过采样数字插值滤波器、具有抖动功能的创新型多位Σ-Δ型调制器、耐抖动数模转换器(DAC)、开关电容和连续时间模拟滤波器、模拟输出驱动电路以及采用28引脚SOIC或SSOP封装的片内直流基准电压源。片内音量控制(节省系统成本)包括立体声衰减器和静音,完全通过SPI兼容串行控制端口编程†。

图1

作为AD1859具有特殊优势的典型应用,MPEG音频要求三种不同的采样速率:32、44.1和48 kHz。对于典型的Σ-Δ音频DAC,设计人员必须提供一个外部时钟电路来合成与这三个采样频率中的每一个相关联的“主时钟”。AD1859是首款具有异步主时钟的音频DAC,简化了这一任务。只需要一个 27 MHz 时钟(外部提供或使用外部 27 MHz 晶体在片上生成);AD1859的锁相环可自动适应不同的输入采样速率,从而显著节省系统成本。DPLL 将在 100 到 200 毫秒内锁定到任何新的采样率(应用于左右时钟引脚);高于和低于采样频率 15Hz 的抖动分量在每倍频程 6dB 时被抑制(例如,高于或低于采样速率 150Hz 的抖动降低 20dB)。

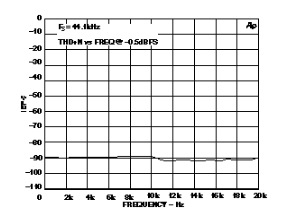

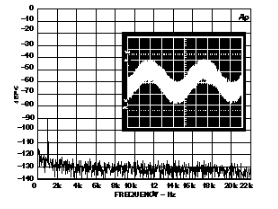

保证的性能特征包括使用A重量滤波器的最小动态范围为88dB(无滤波器为85.7dB),以及音频频段(84 Hz至0 kHz)上的最大总谐波失真和噪声(THD+N)为-0063dB(20.20%)。图2是-0.5 dBFS幅度下THD+N与频率的典型关系图。图3是-90 dB、1 kHz音调的FFT,并附有时域图,展示了在这种低电平下不受谐波、杂散和量化效应的影响,这是模拟系统的典型特征,但很难通过数字方式实现。

图2

AD1859的另一个独特特性是创新的多位Σ-Δ调制器(见侧栏),有助于抑制时钟抖动,从而增强系统可听性优势,降低带外能量,从而节省系统成本。

图3

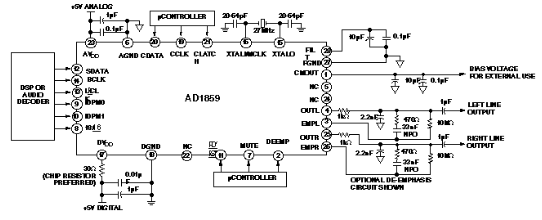

通过灵活的串行数据输入端口与AD1859的接口非常简单,该端口允许与各种ADC、DSP、AES/EBU接收器和采样速率转换器无缝互连。多功能串行数据输入端口可配置为左对齐,I2S 对齐、右对齐和 DSP 串行端口兼容模式。该芯片接受 MSB 优先、二进制补码格式的 16 位或 18 位音频数据。AD1859支持连续可变采样速率和基本线性(在±0.1%)以内的相位响应。在模拟输出级可选择去加重功能,只需添加几个外部组件即可实现改进的采样率不变降噪。(图4)

图4

省电模式(48mW vs. 330mW)可在器件处于非活动状态时最大限度地降低功耗。整个立体声数字音频播放子系统采用+5 V单电源供电,温度范围为-40°C至+105°C;它采用 28 引脚 SOIC 和 SSOP 封装。

AD1859性能的关键

AD1859具有极佳的保真度和低电平线性度,大大降低了电路复杂性,可轻松与DSP(数字信号处理器)和ADC(模数转换器)接口,并降低数字音频播放系统的功耗和成本。

它与传统设备有两个关键区别。首先是其独特的DPLL(数字锁相环)时钟管理器。这是一款异步采样速率管理器,可自动调整输入采样频率,并允许AD1859采用与其自身主时钟不同的频率进行时钟计时。它基于ADI公司开发的专利异步采样率转换技术(Analog Dialogue 28-1,1994,第9-11页)。到目前为止,还没有其他音频DAC具有此功能。其他音频DAC(数模转换器)需要一个调谐良好的高频主时钟,其运行速度是预期音频采样率的256或384倍。这种高频同步时钟的生成和管理对板级设计人员来说非常繁重。

外部异步时钟振荡器可用于提供AD1859的主时钟;但是,AD1859内置一个片内振荡器,因此设计人员只需提供廉价的石英晶体或陶瓷谐振器作为外部时基。AD1859的板载DPLL将在大约1 ms内锁定到主时钟频率的512/1至1024/100之间的任何输入采样速率。晶体时基或MCLK输入上的抖动被抑制(凭借片内开关电容滤波器),以及输入LRCLK输入上的抖动达到音频DAC前所未有的水平。

AD1859的第二个与众不同特性是其获得专利的多位Σ-Δ调制器,其带外噪声能量显著低于竞争IC。较低的带外噪声能量减少了对DAC后滤波的需求,因此所有必要的DAC后滤波(可选的模拟去加重除外)都集成在芯片上。多位Σ-Δ调制器的另一个特性是其对数字基板噪声的高抗扰度,进一步提高了音频信号的完整性。

什么是多位Σ-Δ调制器?在基本方法中,典型的Σ-Δ调制器具有两个量化级别,DAC必须平均脉宽调制的满量程方波;但在AD1859中,使用了17级量化,平均滤波器的输入可以被认为是对1级阶梯的16/17满量程元件进行平滑处理的简单得多的任务。此外,AD1859以输入采样速率的128倍对输入信号进行采样,是传统采样速率的两倍。额外的量化水平和更高的过采样率意味着输出频谱包含的带外噪声能量水平要低得多;允许更简单的DAC后重建滤波器。其降低的过渡带陡度和衰减要求可降低相位失真并提高保真度。

有缺点吗?传统上限制多位Σ-Δ转换器性能的问题是用于对量化电平求和的无源电路元件的非线性。设计师发明了一种革命性的架构来克服这个问题1.

该芯片的其他有趣功能包括使用具有三角概率分布函数的抖动来进一步降低量化噪声;片内低通滤波由二阶开关电容滤波器和一阶模拟连续时间滤波器组成。除了滤除噪声外,它还减少了任何残留的主时钟抖动的影响。

审核编辑:郭婷

-

MAX9879:高效立体声D类音频子系统的卓越之选2026-01-16 352

-

立体声模拟到数字转换器与单端模拟电压输入的ADC芯片-CJC18082025-12-05 1718

-

立体声DAC芯片与普通DAC芯片的使用区别是什么?2024-10-23 690

-

基于STK4141II的立体声功放电路2022-07-15 6411

-

请问我可以仅使用单输出立体声输出吗?2019-07-29 2288

-

数字音频最新技术:单芯片数字立体声子系统2019-04-10 3530

-

单芯片蓝牙立体声耳机解决方案:BC57F687A052019-01-09 5837

-

采用数字输入D类音频放大器的高性能立体声音频子系统2019-01-03 3688

-

LM4949立体声D类音频子系统与OCL耳机放大器2018-05-23 1950

-

影院数字立体声自同步系统的设计2011-04-10 1117

-

立体声数字音频AD18592010-03-18 3071

-

什么是准立体声/立体声?2010-02-05 716

-

电视节目立体声播出方案探讨2009-10-06 3964

-

TPA2050D4 模拟输入音频子系统 集成立体声D类功率放2008-09-01 1495

全部0条评论

快来发表一下你的评论吧 !