高压SiC MOSFET发展历程与研究现状

功率器件

描述

1、高压 SiC MOSFET 发展历程与研究现状

1.1 SiC 材料的优越性

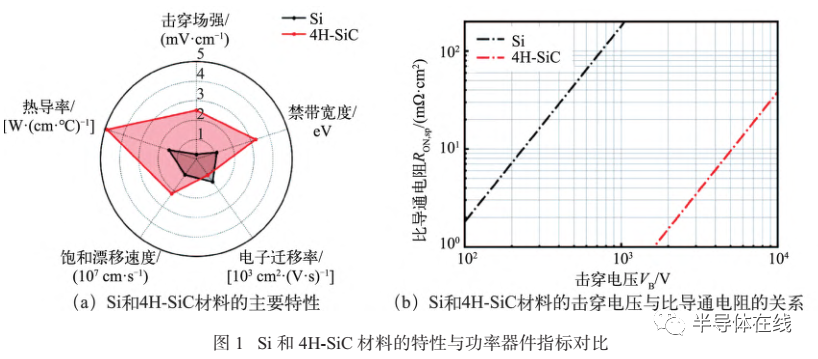

目前已知的 SiC 材料有 250 多种晶体结构,其中4H-SiC 晶型具有更高的迁移率,因此 SiC 功率器件主要基于 4H-SiC 材料。Si、4H-SiC 2 种半导体材料的主要特性如图 1 所示,其中 Si 的带隙宽度为 1.12 eV、热导率为 1.5 W/ (cm·℃)、击穿场强 Ec 为 2.5×105 V/cm,而 4H-SiC 的带隙宽度为 3.26 eV、热导率为4.9 W/(cm·℃)、Ec 可达 2.5×106 V/cm。4H-SiC 功率器件有着 10 倍于 Si 功率器件的击穿场强,这意味着在同等电压等级下 4H-SiC 功率器件的尺寸远小于 Si 功率器件,这将进一步提升器件的功率密度,改善器件的散热等特性,使其可以在更大电流和更高频率下工作。从比导通电阻 RON,sp 和击穿电压 VB 的关系可以进一步说明 4H-SiC 材料的先进性,二者都是衡量单极型高压功率器件的核心参数,在穿通结构下存在理论极限关系:RON,sp=(3/2)3 VB2 /εs μnEc3 ,其中 εs 和 μn 分别为半导体材料的介电常数和电子迁移率,从图 1(b)可以进一步看出,4H-SiC 功率器件与 Si 相比具有耐压更高、损耗更低的优良特点。

1.2 SiC MOSFET 器件的发展历程

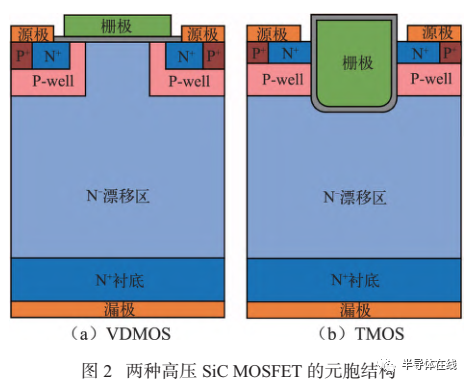

功率 SiC MOSFET 主要有 2 种技术路线,根据栅极工艺分为平面型 MOSFET (VDMOS) 和沟槽型MOSFET(TMOS),两种器件的元胞结构如图 2 所示。多数产品均采用 SiC VDMOS 结构,其工艺简单、阻断能力强,然而导通电阻较大;SiC TMOS 是目前的研究热点,其沟道迁移率高,但工艺较为复杂,受栅氧可靠性影响导致阻断能力较差。

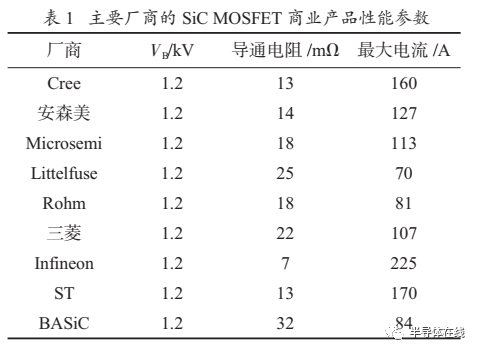

自20 世纪 80 年代第一款 3C-SiC 衬底上的横向MOSFET 和 1994 年首个功率 SiC MOSFET 研制成功以来,各大公司和研究机构都如火如荼地进行着 SiC功率器件的开发。2001 年,Infineon 公司推出了首款商用 SiC 二极管器件。2010 年,Cree 公司和 Rohm 公司相继推出了 SiC VDMOS 产品。2011 年起,各公司开始逐步推出商用 SiC 功率器件。Rohm 公司于 2012 年提出并使用双沟槽结构 SiC TMOS;Infineon 公司于2017 年推出了 CoolSiCTM 产品;Cree 公司专注于平面型并已推出第三代 1.2 kV/160 A 的 SiC VDMOS。主要厂商的 SiC MOSFET 商业产品性能参数如表 1 所示。3.3 kV 及以下等级的功率 SiC MOSFET 已经迈入产业化阶段,越来越多的研究也偏向沟槽、双沟槽(DT)结构;然而对于 3.3 kV 以上、特别是 10 kV 及以上的超高压等级 SiC MOSFET,只能使用平面型结构以避免沟槽底部的栅氧可靠性问题。

国际上对高压 SiC MOSFET 的研究起步较早,多家公司及科研机构均同步跟进该领域前沿方向。第一款性能较为完善的 10 kV 等级超高压 SiC VDMOS 是由美国 Cree 公司 RYU 等人于 2006 提出和研制的,其击穿电压为 10 kV,电流等级为 5 A,室温下测得比导通电阻为 111 mΩ·cm2 ,使用了由 65 个浮空场限环(FLR)组成、总长度为 550 μm 的终端结构。2012 年,日本 AIST 研究所在 DT 结构的基础上进行沟槽底部P+ 区注入并实现了 3.3 kV/7.0 mΩ·cm2 等级的高压SiC TMOS。2014 年,Cree 公司的 ALLEN 等人提出了 SiC VDMOS 电压等级从 900 V 到 15 kV 的提升流程,并进一步缩减裸片尺寸、增强器件性能。2015 年,日本住友电工分别通过靠近沟槽底部深 P+ 注入和终端结构注入剂量优化,研制了 1.7 kV/3.5 mΩ·cm2 等级的高压 SiC TMOS 和 3.3 kV/14.2 mΩ·cm2 等级的高压SiC VDMOS。2015 年,Cree 公司首次展示了全新一代 10 kV 等级的超高压 SiC VDMOS 器件的全部特性,其导通电阻从以往的 160 mΩ·cm2 改进到 100 mΩ·cm2 。

2017 年,Cree 旗下的 Wolfspeed 部门提出了新一代6.5 kV/30 A、 导 通 电 阻 小 于 90 mΩ 的 高 压 SiC VDMOS;同年,三菱电机公司研制出 6.5 kV/50 A 等级的高压 SiC VDMOS,并将肖特基势垒二极管(SBD)嵌入元胞结构中,还于次年进一步研究了不同终端结构对阻断特性保护的稳健性。2020 年,ABB 公司同样提出了具有宽反向偏压安全工作区域和大浪涌电流能力的 6.5 kV/8 A 的高压 SiC VDMOS。同年,Rohm 公司发布了第四代双沟槽 SiC TMOS,在不牺牲短路耐受时间的条件下降低了比导通电阻和寄生电容。

与国际相比,我国高压 SiC MOSFET 领域虽然起步较晚、目前大多停留在科研阶段,但研究已经逐渐成熟,与国外的差距正在逐步减小。中国电科集团第五十五所建立了高压 SiC MOSFET 研发部门并成功研发了 1.2 kV/50 A、3.3 kV/30 A、6.5 kV/25 A 和10 kV/15 A 等级的高压 SiC VDMOS;株洲中车时代电气股份有限公司、深圳基本半导体有限公司、华润微电子有限公司等也相继推出了 1.2 kV 等级系列高压 SiC VDMOS;电子科技大学的邓小川等人设计了一种多区步进间距 FLR 新结构,并据此生产了 13.6 kV等级超高压 SiC VDMOS,电流等级为 10 A;浙江大学也研制出 1.2 kV 等级的高压 SiC VDMOS。

1.3 静态特性优化现状

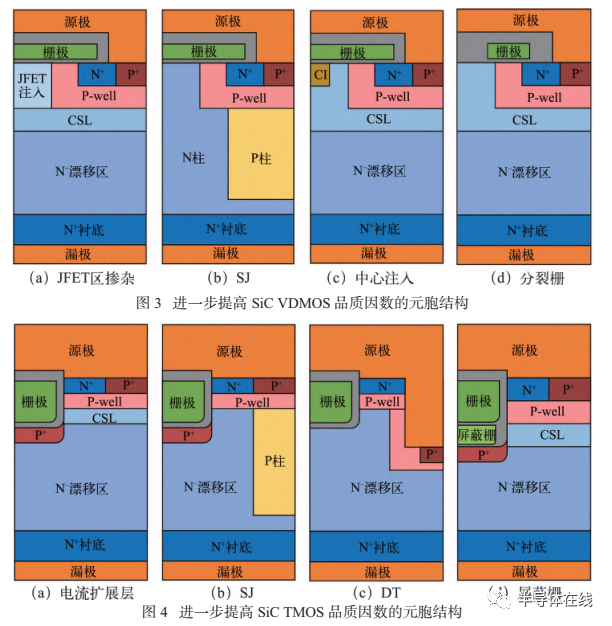

Baliga 品 质 因 数 (BFOM)FB 是 描 述 高 压 SiC MOSFET 静态特性的核心指标,关系式为 FB=VB 2 /RON,sp,它反映了击穿电压与比导通电阻之间的矛盾关系和导通特性的优劣程度。对器件元胞结构的主要参数进行优化,可以在维持电压等级不变的条件下降低比导通电阻,从而提升 BFOM,然而由于沟道击穿、栅氧可靠性等问题和衬底、电极金属的存在,比导通电阻无法达到理论值。要想进一步提高 BFOM,需要对器件的元胞结构进行改进,通过引入外加电荷等手段进一步降低导通电阻。目前主要有 2 种改进结构,分别是JFET 区掺杂结构和超结(SJ)结构,进一步提高 SiCVDMOS 和 SiC TMOS 品质因数的元胞结构分别如图3、4 所示。

1.3.1 JFET 区掺杂结构

从导通电阻的角度考虑,以 VDMOS 结构为例,当器件正向导通时,电流先从沟道水平通过,随后从狭窄的 JFET 区以梯形的形状流入漂移区,降低器件的正向导通能力。TMOS 虽然没有 JFET 区,但也存在电流流向漂移区时路径较窄的问题。如何降低 JFET区及其周围电子流通路径的电阻率,并拓宽电子在JFET 区的流动范围以降低导通电阻,是 JFET 区掺杂结构设计的核心目标。JFET 区掺杂主要存在 2 种实现方式:1)JFET 区注入,即在 P-well 区颈部进行大于外延层浓度的 N 型掺杂以降低电阻率,该方式只适用于平面型;2)电流扩展层(CSL),即在 P-well 注入之前进行一定深度的大于外延层浓度的 N 型掺杂,实现增大电流路径、减小导通电阻的效果,但是栅氧可靠性会受到一定程度的影响,该方式在高压 SiC VDMOS 和 SiC TMOS 中都已经得到了广泛的使用,特别是在 SiC TMOS 中可以与沟槽底部 P+ 屏蔽层(PS)配合使用以同时实现降低导通电阻和保护栅氧的作用。

1.3.2 超结结构

SJ 结构的出现打破了传统 Si 基器件比导通电阻与击穿电压之间的 RON,sp∝VB 2.5 极限关系,使得相同电压等级下 RON,sp 大幅降低,是功率 MOSFET 器件自发明以来的一个重要里程碑。SJ-MOSFET 通过在漂移区引入异型掺杂,将以往的电阻性耐压层转变为 N/P柱交替排列形成的结型耐压层,使得 N 柱和 P 柱之间形成横向耗尽,提高击穿电压。在正向导通时,电子从N 型掺杂区通过,因此可以提高 N 型掺杂浓度,使之在维持击穿电压的情况下进一步降低比导通电阻。陈星弼院士于 1991 年首次提出纵向功率器件的 SJ 结构并申请专利,该结构在当时被称为复合缓冲层。1998年开始,Infineon 公司推出了 CoolMOSTM 产品,其他公司也相继研制并生产了 Si基 SJ 器件,SJ 技术开始广泛运用于 Si 基功率器件中。Si 基 SJ 器件的成功让研究人员转向 SiC SJ 器件的研发当中。

目前 SiC SJ 器件主要有 2 种技术路线:1) 多次外延加离子注入(ME),即在多次外延形成 N 柱的同时多次离子注入形成 P 柱,此路线工艺方式复杂,但可以形成质量较高的结构,界面态密度和晶格缺陷较少,不过外延厚度的增加将导致成本无法控制;2) 深槽刻蚀加外延回填(TFE),该路线由日本 AIST 研究所提出,成本较低,然而深槽角度和 P 柱深度需要进行优化设计。

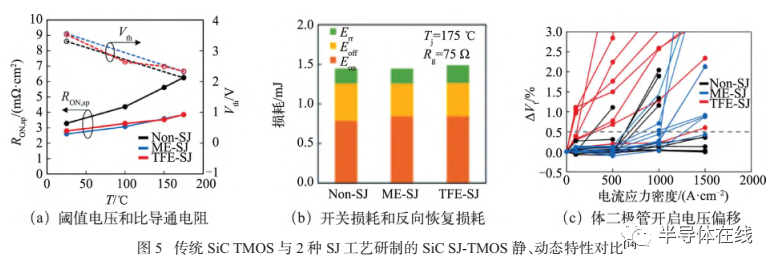

日本 AIST 研究所专注于 SiC SJ 器件的研究和制备。该研究所于 2013 和 2014 年分别通过 ME 和 TFE的技术路线研制出 SiC SJ 器件,并借助 TCAD 仿真研究了 ME 工艺下不同击穿电压器件的特性预测和 TFE工艺下回填外延区掺杂浓度对击穿电压的敏感性。结果表明,ME 工艺下 3.3 kV 等级器件的漂移区电阻为1.51 mΩ·cm2 ,是 4H-SiC 理论极限的五分之一;两次TFE 与单次 TFE 相比,回填外延区掺杂浓度的设计窗口更宽。2022 年,该研究所对 3 种工艺下 1.2 kV 等级SiC SJ-TMOS 器件的静、动态特性进行了对比和分析。从图 5(a)所示的比导通电阻随温度的变化趋势可以看到,2 种 SJ 工艺都可以降低器件温度系数并且 TFE工艺的器件温度系数更小;在结温 Tj 为 175 ℃、栅极驱动电阻 Rg 为 75 Ω 的条件下,从图 5(b)所示的开通损耗 Eon、关断损耗 Eoff 和体二极管反向恢复损耗 Err 的情况可以看到,3 种工艺下器件的动态特性基本一致,因此在相同特性下成本更低的 TFE 技术更具优势;图5(c)显示了 TFE 工艺下器件的体二极管开启电压偏移 ΔVf 更大,双极退化更为严重,这是载流子寿命在制造过程中没有减少和外延 / 衬底界面空穴浓度高导致的,因此如何在控制成本的基础上提高器件特性还有待进一步研究。

除了上述两种工艺之外,浙江大学于 2018 年首次使用沟槽侧壁倾斜离子注入技术研制了 1.35 kV/0.92 mΩ·cm2 等级的 SiC SBD,为 SiC SJ-TMOS 的研究提供了新的发展方向。

SJ 技术在高压 SiC MOSFET 器件整体应用中较少,还有着极大的发展空间。该结构可以提高 SiCTMOS 的电压等级。TMOS 电压等级受限于栅氧角落处的尖峰电场问题,而如果采用 SJ 结构,漂移区 N 型掺杂浓度的提高可以有效降低 RON,sp,同时 P 柱可以有效保护栅氧底部,如张跃等人设计了一种由上下掺杂浓度不同的 P 柱形成的 SiC SJ-TMOS 功率器件,仿真结果表明在击穿电压 1 kV 下可得到 0.88 mΩ·cm2 的比导通电阻。SJ 结构也可以与 SBD 同时嵌入MOSFET 元胞中,以同时改善器件比导通电阻和反向恢复特性。日本 AIST 研究院已研制出目前电压等级最高的 SiC SJ-VDMOS 器件,击穿电压达到 7.8 kV,离 15 kV 的超高压等级还有一段距离,值得进一步设计和研发。

SiC SJ 器件的终端结构较传统 SiC MOSFET 器件来说设计复杂度更高:一方面,终端结构同样需要考虑电荷平衡问题,以保证效率;另一方面,由于工艺的繁琐,终端结构的工艺技术应该尽量与元胞保持一致,以降低工艺复杂度,即如果元胞使用的是 ME 工艺,则终端也需使用同样的工艺形成 N/P 柱的交替结构。该领域目前国际上已有相关研究,如 MASUDA 等人将 ME 工艺和结终端扩展(JTE)技术结合起来,设计和研制了针对 1.2 kV 等级 SiC SJ-TMOS 的一种新型终端结构,然而研究成果总体较少,有待进一步深入研究。

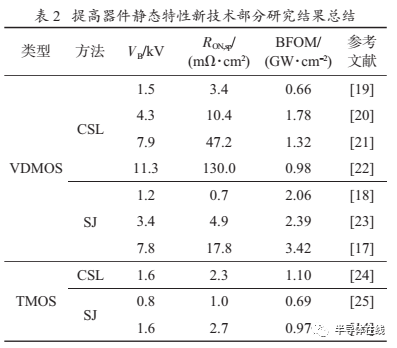

国内外针对 2 种结构器件 BFOM 优化的研究成果如表 2 所示,其中 JFET 区注入技术常常与 CSL 技术合并,因此不在表中列出。

1.4 动态特性优化现状

高频品质因数(HF-FOM)是高压 SiC MOSFET 另一个主要性能指标,它一般是 RON,sp 和比栅漏电荷 QGD,sp的乘积,反映了器件动态特性的优劣程度,其中影响栅漏电荷的主要因素是转移电容的大小。

对于高压 SiC VDMOS 来说,目前有几种技术和结构可以改善器件的 HF-FOM:1)中心注入技术(CI),如图 3(c)所示,即在栅氧下方注入一个 P 型掺杂区,该技术可以同时实现增强动态特性和减小栅氧电场的效果,只适用于平面型结构,以 Cree 公司的CIMOSFET 产品为代表[26],该技术与 CSL 技术同时使用可以在兼顾动态性能的基础上进一步降低 JFET 区导通电阻;

2)分裂栅(SP)结构,如图 3(d)所示,即只保留沟道上方的栅极多晶硅而去掉 JFET 区上方的部分,如 YOON 等人将 SP 应用于 3.3 kV 等级器件并进行了仿真验证;YU 等人在 SP 的基础上给源极加上场板结构,在降低栅极边缘电场强度的同时将HF-FOM 减小了 40%;LYNCH 等人研制了 15 kV 等级 SP 结构器件,栅漏电荷较传统平面型降低了70%。除此之外,AGARWAL 等人通过理论验证了将栅氧厚度从 55 nm 降低到 27 nm 后器件静、动态特性的提升。

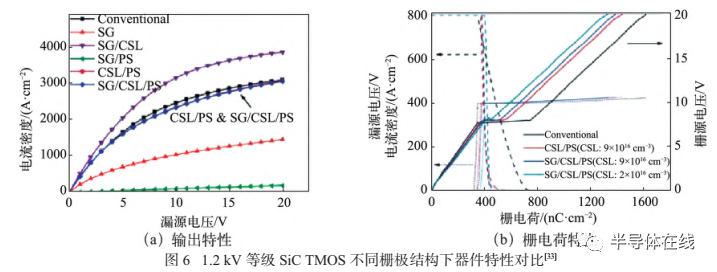

对于 SiC TMOS 来说,DT 结构和屏蔽栅(SG)结构可以有效改善动态特性。1)DT 结构以 Rohm 公司的双沟槽 SiC TMOS 产品为代表,如图 4(c)所示,它通过源极沟槽保护栅氧,实现了 1.26 kV/1.41 mΩ·cm2的优越特性。YANG 等人在 DT 的基础上引入了深 PS结构,较改进前栅漏电荷降低了 89%;YANG 等人提出了一种深氧化物沟槽代替源极沟槽的结构,在改善静态特性的情况下降低了开关损耗。2)SG 结构首先在 Si 基器件中提出,随后在 SiC TMOS 中得到了改进,如图 4(d)所示,它通过横向耗尽漂移区和减少栅漏之间有效重叠面积同时降低导通电阻和转移电容,大幅提升动态特性。JIANG 等人按是否有 SG、PS 和CSL 将 SiC TMOS 分为 6 种结构,并进行了静、动态特性仿真对比,如图 6 所示。结果显示,SG 结构可以降低栅电荷,但是 SG 与 PS 结构对导通特性影响严重,而通过 CSL 的引入,可以在降低 RON,sp 的基础上进一步降低 QGD,sp,显著提高器件的 HF-FOM。

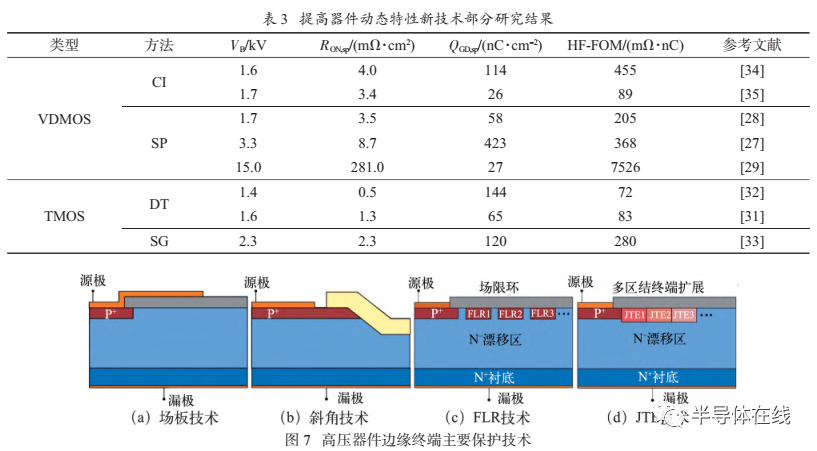

表 3 展示了 2 种元胞结构 HF-FOM 优化的部分研究结果。表 3 中只有文献[29]和[34]为实际流片测试结果,可以看出仿真结果较实际器件特性还有一定距离,因此如何更准确地预测和描述实际器件的动、静态特性并在此基础上进一步改进器件的高频工作性能,还需进一步研究和实践。

1.5 终端研究现状

器件在阻断状态下,主结的边缘处曲率较小,容易产生电场集中的现象,导致器件的阻断性能严重退化,击穿电压大大降低。特别是 4H-SiC 材料,其扩散系数较 Si 来说更小,对于 MOSFET 和 IGBT 等浅结器件来说,曲率效应更为严重。因此高压 SiC MOSFET的边缘终端需要进行保护。目前存在的几种高压器件边缘终端主要保护技术如图 7 所示。

场板技术和斜角技术在 Si 基器件中较为成熟,然而其耐压等级较低,不适用于高压 SiC 器件。FLR 技术和 JTE 技术被认为更加适用于高压 SiC MOSFET器件。

1.5.1 FLR 技术

FLR 技术也被称作浮空场环技术,即注入多个 P型场环,缓解主结边缘的电场集中问题,以改善器件的阻断特性。在实际制造过程中,FLR 往往和主结同时注入,不需要额外的工艺步骤,技术简单且成本较低,在 SiC 功率器件中已经得到了广泛的使用。已有相关研究推导了 FLR 结构的理论公式,然而对于高电压等级特别是 10 kV 及以上等级的 SiC MOSFET 来说,往往需要上百个场环,理论分析基本无法指导结构设计,而且受限于工艺条件,环间距无法做到与计算值一样精确。这就需要根据相关参数进行 FLR 结构设计和实验验证。

FLR 结构主要由环宽和环间距决定,根据二者的设计产生了多种结构,其中最经典的便是等环宽、等间距结构(Con-FLR),除此之外还有固定环宽、改变间距的结构,如路晓飞等人提出的间距呈指数变化的FLR 结构、间距呈线形变化的 FLR 结构,邓小川等人提出的多区步进间距 FLR 结构,以及环宽与间距协调配合的结构等。

FLR 技术的问题在于终端面积较大,这可以通过与其他技术相结合的方法进行优化,例如 WEN 等人针对 10 kV 等级器件,提出了一种刻蚀和 FLR 相结合的刻蚀均匀 FLR (EU-FLR) 结构,阻断能力达到14.2 kV 并且终端长度大幅降低。

1.5.2 JTE 技术

简单来说,JTE 技术就是在主结旁边额外注入一段长度的 P 型掺杂,为主结分压以减小曲率效应。该技术由 KALER 在 1977 年首次提出,其在高压 Si 基器件上的有效性得到验证后,JTE 技术便被业界广泛关注,多种改良型 JTE 结构也相继提出。随着 SiC 材料的研究和应用,功率器件的耐压等级已经超过10 kV,特别是超高压 SiC PiN 器件,目前国际上已经达到将近 30 kV 的水平,针对高压 SiC 器件的 JTE 技术被相继提出,从台面单区 JTE 到多区 JTE,再到空间调制 JTE,在 JTE 技术的保护下功率器件越来越逼近雪崩击穿的理论击穿电压,并且其终端区域的利用效率也不断提高,如 2018 年 NAKAYAMA 等人利用空间调制 JTE 技术研发出 27.5 kV 等级 4H-SiC PiN 功率二极管。

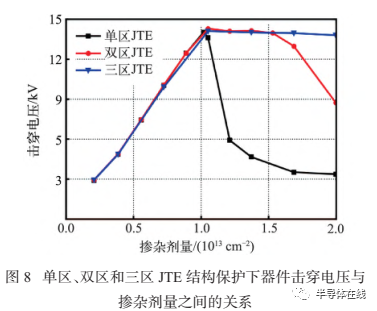

JTE 技术的核心问题在于终端保护效率对于掺杂剂量的敏感度较高,加上 4H-SiC 中杂质存在不完全电离的情况,即使精准控制注入剂量也会导致实际激活的剂量不受控制,因此大部分 JTE 改进结构都在朝着扩大掺杂剂量窗口的方向进行探索。对 10 kV 等级器件进行终端保护仿真,分别设计单区、双区和三区JTE 结构,得到的击穿电压与掺杂剂量之间的关系如图 8 所示。仿真中元胞击穿电压值为 14.4 kV,可以看到单区 JTE 的剂量窗口不足 0.3×1013 cm-2 ,双区结构下敏感性得到了明显改善,剂量窗口达到 0.8×1013 cm-2 ,到三区结构下剂量窗口超过 1.5×1013 cm-2 ,证明了多区JTE 结构可以有效改善剂量窗口问题。

单纯地增加区域数将增加工艺流程中的离子注入步骤,大大提高成本。目前 JTE 技术趋向于使用固定的 2 种或多种掺杂剂量,通过调制掺杂区域的形状和宽度来形成多个不同等效电离电荷浓度的区域。KAJI 等人首次结合空间调制技术和双区 JTE 技术在外延层厚度为 268 μm、掺杂浓度为 1×1015 cm-3 的条件下实现了 26.9 kV 的击穿电压[,保护效率达到 70%,剂量窗口大于 1.5×1013 cm-3 。在此基础上,改进 JTE 结构的保护效率越来越高,终端长度也有所改善,如WEN 等人于 2020 年研制和生产了使用在 13.5 kV 等级 4H-SiC PiN 二极管器件中的一种被称为电荷场调制 JTE(CFM-JTE)的结构,在 400 μm 的终端长度下实现了 96%的终端保护效率和大于传统双区 JTE 结构 1.8 倍的剂量窗口。

将 JTE 技术与其他技术进行结合,可以在相同终端面积下进一步提高保护效率,如 DAI 等人于 2021年提出的刻蚀沟辅助空间调制 JTE (TSM-JTE)结构;ZHOU 等人提出了一种结合刻蚀与单区 JTE 的超小角度斜角刻蚀 JTE 结构(ULA-BE-JTE),实现了超过 90%的保护效率。另外,对 JTE 技术的仿真工作已经使器件的击穿电压达到了 30 kV 以上的等级,如JOHANNESSON 等人在 TCAD 仿真上用 1800 μm 的单侧 JTE 区加 27 个外侧保护环实现了 41.4 kV 的击穿电压。

2 高压 SiC MOSFET 的瓶颈与挑战

当下,高压 SiC MOSFET 还存在一些瓶颈和挑战,这里对 4 个主要问题进行讨论。

2.1 双极退化效应

高压 SiC MOSFET 器件存在体二极管结构,理论上可以取代外接反并联二极管并降低电路寄生电感与损耗。然而在双极性运行条件下,体二极管的导通会带来双极退化效应,影响器件的导通电阻、漏电流和体二极管导通压降等特性,不利于器件的长期工作。

从应用的角度,人们普遍使用同步整流技术以尽量避免体二极管的开通;从器件结构设计的角度,近年来针对该问题出现了一些致力于将 SBD 或结势垒肖特基二极管嵌入 MOSFET 元胞结构当中的研究,如DENG 等人提出了一种低势垒二极管集成新结构,在1.2 kV 等级器件中获得了较体二极管低约 67%的开启电压;LI 等人提出了一种在双沟槽 SiC MOSFET中加入全耗尽 P-well 区以降低势垒并抑制双极退化效应的新结构。然而嵌入的方式将会导致器件特性和可靠性的改变,KONO 等人研究了 1.2 kV 等级 SBD嵌入式器件的比导通电阻与短路耐受能力之间的权衡关系。如何有效解决该问题还需进一步深入研究。

2.2 低电流等级问题

高压 SiC MOSFET 由于其单极工作模式,高击穿电压将严重限制器件的导通电流能力。例如对于10 kV 等级器件来说,室温下其电流等级约为 20~40 A/cm2 ,当温度增加到 200 ℃以上时,额定电流将下降 50%~70%。加之厚的外延层更容易引入缺陷,终端的存在导致芯片源区实际面积不大,因此 6.5 kV 及以上的单片并不能满足相应等级应用场景的需求。针对这一问题目前有 3 种解决方案:1) 制作多芯片并联模块以提高电流等级,如 Wolfspeed 研制了 12 个芯片并联的 10 kV/240 A 功率模块;2)使用双极型器件,如目前 15 kV 等级及 SiC 栅极可关断晶闸管器件电流等级可以超过 100 A;3)继续改进外延技术,找到控制外延缺陷的新技术。针对电流等级低的问题,未来需要继续优化器件结构以降低温度系数,不断改进关键工艺技术以降低缺陷密度,从而进一步提升高压 SiC MOSFET 的电流等级。

2.3 外延缺陷问题

高压器件的性能主要依赖于外延层的材料和技术。目前主流的外延生长工艺是化学气相沉积法(CVD),一方面在工艺过程会产生点缺陷,另一方面衬底中的微管、堆垛层错等扩展缺陷会进入外延中,严重影响外延层的质量和芯片良率。研究显示,对衬底表面采用氢刻蚀等工艺可以有效除去表面损伤和表面缺陷,对热壁式 CVD 的反应室进行改进也可以提高外延的质量和均匀性。国内外已有表面缺陷小于1 cm-2 、厚度为 30 μm 的成熟 6 英寸外延片,然而厚度大于 50 μm 时缺陷密度将进一步扩大,不利于高压SiC MOSFET 的发展和应用。如何改善工艺条件以控制外延缺陷和阻挡衬底缺陷的影响,仍需进一步的实验测试和验证。

2.4 可靠性问题

栅氧的工艺质量和缺陷水平是制约高压 SiC MOSFET 长期工作的关键因素之一。在重复栅偏电应力和高温工作环境的作用下,栅氧界面陷阱会不断地捕获或者释放电荷,严重影响器件的参数稳定性和运行可靠性。与 Si 基器件相比,高压 SiC MOSFET 的SiC/SiO2 界面缺陷密度比 Si/SiO2 界面高出约 2 个数量级,这是 SiC 与 Si 的材料特性差异和 SiC 工艺技术不成熟导致的,使得高压 SiC MOSFET 栅氧界面缺陷对电荷的捕获与释放效应更加严重,进而引起阈值电压、导通电阻、漏电流等器件参数的退化和不稳定。阈值电压漂移是器件参数稳定性中的一大问题,在 2006年就有研究展示了高达数百毫伏的阈值电压漂移量,AIVARS 等人报道了一氧化氮退火工艺在栅氧界面处 产 生 的 空 穴 陷 阱 会 导 致 阈 值 电 压 负 向 漂 移 。PUSCHKARSKY 等人针对阈值电压稳定性问题对比了 Si、SiC 功率 MOSFET 二者的区别,并讨论了在动态应力下的阈值电压测量技术。栅氧寿命也是评价器件长期可靠性的重要方面,这主要通过时变介质击穿实验进行表征。有研究显示,在器件正常工作的情况下,栅氧电场强度达到 3 MV/cm,栅氧寿命可达到100 年,也有工作通过改进氧化工艺以提高栅氧质量和寿命。整体上,高压 SiC MOSFET 的栅氧工艺还未成熟,需要进一步优化工艺水平,提高器件的可靠性和性能。

器件在极端工作条件下的可靠性对于保证系统的稳定运行起着至关重要的作用,主要的问题有雪崩失效、短路失效和浪涌失效等。高压 SiC MOSFET 在非钳位感性负载下的雪崩失效机理目前有 3 种解释,分别是由源区寄生双极结型晶体管(BJT)开启导致结温急剧上升产生坏点、温度升高导致沟道自开启和铝电极达到熔点,这 3 者最终都导致热失效,然而失效原因各不相同。白志强等人对 P-well 区的结构和掺杂进行调整和改进,通过降低 BJT 基区串联电阻和 JFET区曲率效应以提高器件的雪崩耐受性;KIM 等人通过减小栅氧厚度和调窄 JFET 区宽度降低了饱和电流,以提高雪崩能量。器件的短路失效和浪涌失效除了热失效原因外,场氧区断裂或铝熔化破坏栅氧导致栅源短路也是两个原因,这对于沉积、热氧化工艺也提出了更高的要求。除此之外,由于 SiC 高于 Si 的热导率和杨氏模量,继续使用传统 Si 器件的封装技术也将阻碍高压 SiC MOSFET 器件的可靠性提升。

针对以上问题,如何改进现有工艺以提高栅氧质量,如何改进器件结构或封装结构以缓解热失效问题或增加散热能力,都是未来需要进一步研究和解决的问题。

3 结束语

针对高压 SiC MOSFET 器件,本文首先回顾和总结了器件发展历程与该领域中的最新研究进展,其次介绍了用于优化品质因数的器件改进结构,进而针对高电压等级要求阐述了几种适用于高压器件的终端保护结构的保护机理与发展趋势,最后对高压器件当前存在的瓶颈和挑战进行了讨论。

高压 SiC MOSFET 器件将在当前乃至未来的电力电子领域发挥越来越重要的作用,推动电能变换朝着更高电压、更高频率、更高功率密度的方向前进。近年来,高压 SiC MOSFET 器件得到了越来越多的机构和企业中科研工作者的关注,发展势头越来越猛烈,这对于未来电能传输和变换应用方面的发展有着巨大的推动作用。虽然受到国外对我国先进半导体材料和工艺上的限制,但国内诸多高校和科研机构仍在持续进行技术研发并跟进国际最新发展方向,与国际先进水平的差距逐渐缩小,国内从业者需要坚持吸取先进技术和经验,早日达到国际领先水平。

编辑:黄飞

- 相关推荐

- 热点推荐

- SiC

- SiC MOSFET

-

SiC MOSFET 开关模块RC缓冲吸收电路的参数优化设计2025-04-23 1667

-

车规级功率模块封装的现状,SiC MOSFET对器件封装的技术需求2023-10-27 2609

-

浅谈高压SiC MOSFET发展历程与研究现状2023-05-04 4531

-

SiC MOSFET的器件演变与技术优势2023-02-27 1411

-

【罗姆SiC-MOSFET 试用体验连载】SiC MOSFET元器件性能研究2020-04-24 2083

-

浅析SiC-MOSFET2019-09-17 6298

-

SiC功率器件SiC-MOSFET的特点2019-05-07 5555

-

SiC-MOSFET有什么优点2019-04-09 4533

-

沟槽结构SiC-MOSFET与实际产品2018-12-05 4703

-

SiC-MOSFET与Si-MOSFET的区别2018-11-30 10935

-

SiC-MOSFET的应用实例2018-11-27 5920

-

如何用碳化硅(SiC)MOSFET设计一个高性能门极驱动电路2018-08-27 11649

-

为何使用 SiC MOSFET2017-12-18 5928

全部0条评论

快来发表一下你的评论吧 !