碳化硅技术壁垒分析:碳化硅技术壁垒是什么 碳化硅技术壁垒有哪些

描述

碳化硅技术壁垒分析:碳化硅技术壁垒是什么 碳化硅技术壁垒有哪些

碳化硅芯片不仅是一个新风口,也是一个很大的挑战,那么我们来碳化硅技术壁垒分析下碳化硅技术壁垒是什么?碳化硅技术壁垒有哪些?

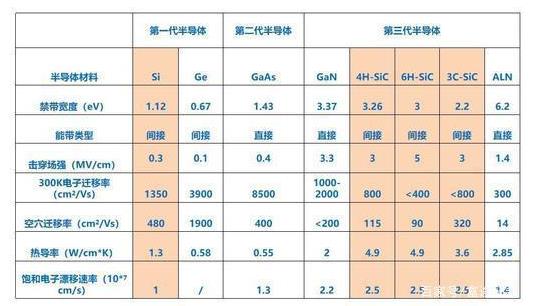

1) 第一代半导体材料以传统的硅(Si)和锗(Ge)为代表,是集成电路制造的基 础,广泛应用于低压、低频、低功率的晶体管和探测器中,90%以上的半导体产品 是用硅基材料制作的;

2) 第二代半导体材料以砷化镓(GaAs)、磷化铟(InP)和磷化镓(GaP)为代表, 相对硅基器件具有高频、高速的光电性能,广泛应用于光电子和微电子领域;

3) 第三代半导体材料以碳化硅(SiC)、氮化镓(GaN)、氧化锌(ZnO)、金刚 石(C)、氮化铝(AlN)等新兴材料为代表。

碳化硅是第三代半导体产业发展的重要基础材料,碳化硅功率器件以其优异的耐高压、耐高温、低损耗等性能,能够有效满足电力电子系统的高效率、小型化和轻量化要求。

因其优越的物理性能:高禁带宽度(对应高击穿电场和高功率密度)、高电导率、高热导率,有望成为未来最被广泛使用的制作半导体芯片的基础材料。特别是在新能源汽车、光伏发电、轨道交通、智能电网等领域具有明显优势。

碳化硅技术壁垒是什么?碳化硅技术壁垒有哪些?

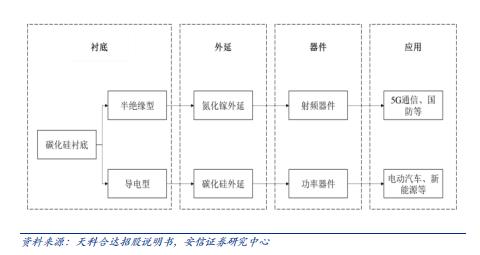

SiC 生产过程分为 SiC 单晶生长、外延层生长及器件制造三大步骤,对应的是产业链衬底、外延、器件与模组四大环节。

主流制造衬底的方式首先以 物理气相升华法,在高温真空环境下将粉料升华,通过温场的控制在籽晶表面生 长出碳化硅晶体。以碳化硅晶片为衬底,使用化学气相沉积法,在晶片上淀积一 层单晶形成外延片。其中,在导电型碳化硅衬底上生长碳化硅外延层,可制成功 率器件,主要应用于电动车、光伏等领域;在半绝缘型碳化硅衬底上生长氮化镓 外延层,可进一步制成射频器件,应用于 5G 通讯等领域。

就目前而言,碳化硅产业链中碳化硅衬底的技术壁垒最高,碳化硅衬底生产难度最高。

SiC的生产瓶颈尚未完全彻底的解决,原料晶柱的质量不稳定存在良率问题,这就导致了SiC器件的成本过高。

硅材料长晶平均只要3天即可长成一根晶棒,但碳化硅晶棒则需要一周,一般的硅晶棒可以长200公分的长,但一根碳化硅的晶棒只能长出2公分。

而且SiC本身属于硬脆性材料,由其制成的晶圆,在使用传统的机械式切割晶圆划片时,极易产生崩边,影响产品良率及可靠性。

SiC基板与传统的硅晶锭有很大不同,从设备、工艺、处理到切割的一切都需要进行开发,以处理碳化硅。

碳化硅产业链主要分为衬底、外 延、器件和应用四大环节,衬底材料是产业链的基础,外延材料是器件制造的关键,器件是产业链的核心,应用是产业发展的动力。产业上游利用原材料通过物 理气相升华法等方法制成衬底材料,再利用化学气相沉积法等方法生长外延材料, 产业中游基于上游材料制成射频器件、功率器件等器件,最终应用于下游 5G 通 信、电动汽车、轨道交通等。其中,衬底和外延共占产业链成本 60%,是产业链主要价值所在。

SiC衬底:SiC晶体通常用Lely法制造,国际主流产品正从4英寸向6英寸过渡,且已经开发出8英寸导电型衬底产品,国内衬底以4英寸为主。由于现有的6英寸的硅晶圆产线可以升级改造用于生产SiC器件,所以6英寸SiC衬底的高市占率将维持较长时间。

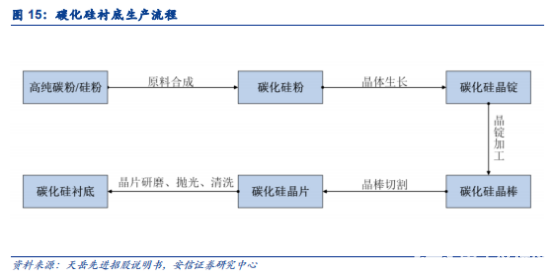

碳化硅衬底工艺复杂,制作难度大。碳化硅衬底是一种由碳和硅两种元素组成的 化合物半导体单晶材料。目前行业内主要以高纯碳粉、 高纯硅粉为原料合成碳化 硅粉,在特殊温场下,采用成熟的物理气相传输法(PVT 法),在晶体生长炉中 生长不同尺寸的碳化硅晶锭,最后经过加工、切割、研磨、抛光、清洗等多道工 序产出碳化硅衬底。

稳定量产性能稳定的高品质碳化硅晶片的技术难点有:

1)由于晶体需要在 2000℃以上的高温密闭环境生长,对控温要求极高;

2)由于碳化硅存在 200 多种晶体结构,但只有少数几种结构的单晶型碳化硅才是 所需的半导体材料,在晶体生长过程中需要精确控制硅碳比、生长温度梯度、晶 体生长速率以及气流气压等参数;

3)气相传输法下,碳化硅晶体生长的扩径技术难度极大;

4)碳化硅硬度与金刚石接近,切割、研磨、抛光技术难度大。

SiC外延:通常用化学气相沉积(CVD)方法制造,根据不同的掺杂类型,分为n型、p型外延片。国内瀚天天成、东莞天域已能提供4寸/6寸SiC外延片。

对于SiC外延来说,高压领域控制难,SiC外延质量对SiC器件影响较大。而且外延设备被行业四大龙头企业 Axitron、 LPE、TEL 和 Nuflare 所垄断。

碳化硅外延片,是指在原有碳化硅衬底 上生长了一层有一定要求的、与衬底晶相同的单晶薄膜(外延层)的碳化硅片。 外延生长主要使用 CVD(Chemical Vapor Deposition,化学气相沉积)设备或者 MBE(Molecular Beam Epitaxy,分子束外延)设备。由于碳化硅器件是直接在外 延层制造,外延质量的好坏直接影响了器件的性能和良率,随着器件需求耐压性 能的不断提高,对应的外延层厚度就越厚,控制难度也就越高。一般电压在 600V 左右时,所需要的外延层厚度约在 6 微米左右;电压在 1200-1700V 之间时,所需 要的外延层厚度就达到 10-15 微米。如果电压达到一万伏以上时,可能就需要 100 微米以上的外延层厚度。而随着外延层厚度的不断增加,对厚度和电阻率均匀性 以及缺陷密度的控制就变得愈发困难。

SiC器件:国际上600~1700V SiC SBD、MOSFET已经实现产业化,主流产品耐压水平在1200V以下,封装形式以TO封装为主。价格方面,国际上的SiC产品价格是对应Si产品的5~6倍,正以每年10%的速度下降,随着上游材料器件纷纷扩产上线,未来2~3年后市场供应加大,价格将进一步下降,预计价格达到对应Si产品2~3倍时,由系统成本减少和性能提升带来的优势将推动SiC逐步占领Si器件的市场空间。

传统封装基于硅基,三代半导体材料具有全新设计。若将传统硅基封装结构用于 宽禁带半导体功率器件时,会在频率、散热、可靠性等方面带来新的问题与挑战。 SiC 功率器件对寄生电容和寄生电感更加敏感。相比于 Si 器件 SiC 功率芯片的开 关速度更快,这会对驱动电压的波形带来过冲和震荡,引起开关损耗的增加,严重时甚至会引起功率器件的误开关。此外 SiC 功率器件工作温度更高,对散热的 要求也更高。

宽禁带半导体功率封装领域研发出多种不同结构。传统 Si 基功率模块封装不再适 用。针对传统 Si 基功率模块封装存在寄生参数过高,散热效率差的问题,SiC 功 率模块封装在结构上采用了无引线互连(wireless interconnection)和双面散热 (double-side cooling)技术,同时选用了导热系数更好的衬底材料,并尝试在模 块结构中集成去耦电容、温度/电流传感器以及驱动电路等,研发出了多种不同的 模块封装技术。

而且在SiC器件制造存在较高的技术壁垒,生产成本很高。

碳化硅器件是通过 CVD 在碳化硅衬底上 叠层外延膜,经过清洗、氧化、光刻、刻蚀、去光阻、离子注入、化学气相沉积 沉淀氮化硅、抛光、溅镀、后加工等步骤后在 SiC 单晶基板上形成元件结构所得。 其中,SiC 功率器件主要包括 SiC 二极管、SiC 晶体管和 SiC 功率模块。受制于上游材料生产速度慢、良品率低等原因,碳化硅器件具有较高制造成本。

此外,碳 化硅器件制造具有一定技术难度:

1)需要开发与碳化硅材料特性吻合的特定工艺,如:SiC 具有高熔点使传统热扩 散失效,需要采用离子注入掺杂法,并精准控制温度、升温速率、持续时间、气 体流量等参数;SiC 对化学溶剂具有惰性,应采用干刻蚀等方法,并优化和开发掩 膜材料、气体混合物、侧壁斜率的控制、蚀刻速率、侧壁粗糙度等;

2)碳化硅晶片上金属电极的制造要求接触电阻低于 10- 5Ω2,符合要求的电极 材料 Ni 和 Al 在 100℃ 以上时具有较差热稳定性,但具有较好热稳定性的 Al/Ni/W/Au 复合电极材料接触比电阻高 10- 3Ω2;

3)SiC 切割磨损高,SiC 硬度仅次于金刚石,对切割、研磨、抛光等技术提出了更高的要求。

而且,沟槽型碳化硅功率器件具有更大制造难度。根据器件结构的不同,碳化硅功率器 件主要可以分为平面型器件和沟槽型器件。平面型碳化硅功率器件具有较好的单 位一致性,制作工艺简单,但易产生 JFET 效应,具有较高的寄生电容和通态电 阻。相较于平面型器件,沟槽型碳化硅功率器件单位一致性较低,具有更复杂的 制作工艺,但沟槽结构有利于增加器件单位密度,不易产生 JFET 效应,有利于解 决沟道迁移率低等问题,具有导通电阻小、寄生电容小、开关能耗低等优良性能, 具有显著的成本优势和性能优势,已成为碳化硅功率器件发展的主流方向。根据 Rohm 官网,ROHM Gen3 结构(Gen1 Trench 结构)仅为 Gen2(Plannar2)芯片 面积的 75%,且同一芯片尺寸下 ROHM Gen3 结构导通电阻降低 50%。

碳化硅衬底、外延、前段、研发费用和其他分别在碳化硅器 件制造成本中占比 47%,23%,19%,6%,5%。

最后我们再着重分解一下碳化硅产业链中衬底的技术壁垒。

碳化硅衬底生产过程与硅基衬底类似,但是难度更大。

碳化硅衬底的制作流程一般包括原料合成、晶体生长、晶锭加工、晶棒切割、晶片研磨、抛光、清洗等环节。

其中晶体生长阶段为整个流程的核心,该步骤决定了碳化硅衬底的电学性质。

碳化硅材料在一般条件下很难液相生长,如今市场流行的气相生长法,生长温度在 2300℃以上,而且需要精确调控生长温度,整个操作过程几乎难以观测,稍有差错就会导致产品报废。

相比之下,硅材料只需要 1600℃,要求低很多。

制备碳化硅衬底还面临长晶速度慢,晶型要求高等困难。碳化硅晶圆生长约需要 7 至 10 天,而硅棒拉晶只需要 2 天半。

而且碳化硅是硬度仅次于金刚石的材料,切割、研磨、抛光时候也会损失掉的很多,产出比只有 60%。

我们知道碳化硅衬底的尺寸做大是趋势,随着尺寸不断增大,扩径技术的要求也越来越高。需要综合多方面的技术控制要素,才能实现晶体的迭代扩径生长。

据集邦咨询数据,预计到 2025 年,全球电动汽车市场对 6 英寸碳化硅晶圆的需求为 169 万片。市场空间很大,但是碳化功率技术、工艺、产能等方面都还有很大的发展空间。

综合整理自 未来智库 富途证券 盖世汽车 中泰证券 兴业证券 车质网 GaN世界 集邦咨询 安信证劵

-

碳化硅压敏电阻 - 氧化锌 MOV2024-03-08 8375

-

国内碳化硅衬底生产企业盘点2023-10-27 3920

-

碳化硅技术壁垒是什么?碳化硅技术壁垒有哪些?2023-08-04 1937

-

浅谈硅IGBT与碳化硅MOSFET驱动的区别2023-02-27 2998

-

归纳碳化硅功率器件封装的关键技术2023-02-22 2937

-

请教碳化硅刻蚀工艺2022-08-31 41987

-

传统的硅组件、碳化硅(Sic)和氮化镓(GaN)2021-09-23 6155

-

碳化硅的应用2021-08-19 3973

-

什么是碳化硅(SiC)?它有哪些用途?2021-06-18 9391

-

碳化硅器件是如何组成逆变器的?2021-03-16 2820

-

碳化硅基板——三代半导体的领军者2021-01-12 4419

-

碳化硅半导体器件有哪些?2020-06-28 4391

-

碳化硅深层的特性2019-07-04 6074

-

碳化硅的历史与应用介绍2019-07-02 5034

全部0条评论

快来发表一下你的评论吧 !