三管MOS DRAM基本单元电路原理 单管MOS动态RAM基本单元电路原理

描述

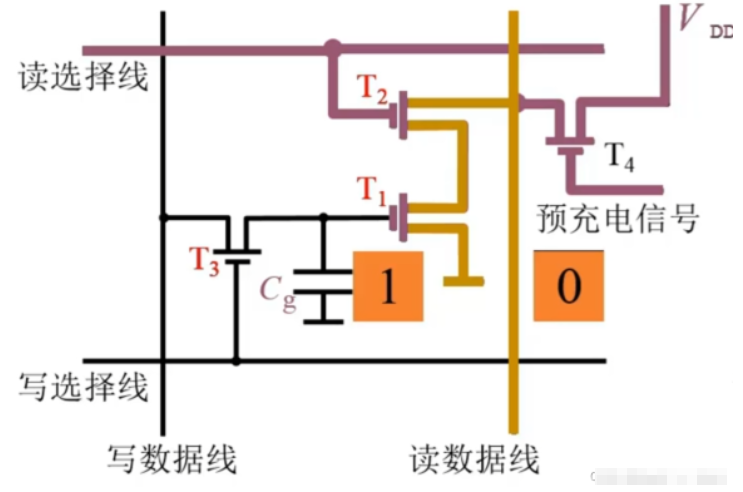

一、三管MOS DRAM基本单元电路原理

如果需要读出数据,首先需要给T4加上一个预充电信号,然后VDD给读数据线充电,代表需要读出的数据是“1”,进行读出时,读选择线是高电平。此时,如果原来存储在电容里面的数据是“0”,则电容为低电平,不带电,那么T1并不会接通。因此此时存的数据是“0”,读出的数据却是“1”。//相反,如果存的数据是“1”,那么T1管就会接通,T1、T2导通接地,所以此时读数据线为低电平,读出的数据就是“0”,。这就是“读出与原存信息相反”,因此需要在读数据线输出端加一个与门。

如果需要写入数据,写选择线为高电平,T3管接通,写数据线若是高电平,就会给Cg充电,写入数据“1”,如果写数据线是低电平,则Cg会通过T3管放电,存入的数据是“0”。这就是“写入与输入信息相同”。

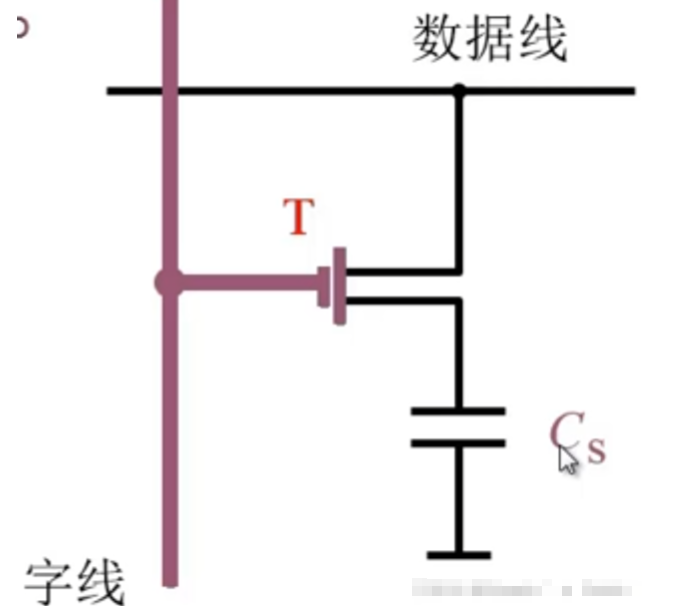

二、单管MOS动态RAM基本单元电路原理

当行被选中时,字线就会通电。

读出数据时:如果Cs存储的是数据“1”,那么就会通过T给数据线放电,使数据线产生电流,如果存的是数据“0”,则数据线会给CS充电,那么此时数据线内部就不会有电流。

写入数据时:数据线要传输的数据如果是“1”,则数据线里面会有电流,就会通过T给Cs充电,存入数据“1”,数据线如果要传输的数据是“0”,则数据线不带电,Cs会立马向外放电,放电后代表存储的数据是“0”。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

mos管短路保护电路的原理和应用2023-08-25 12956

-

MOS管开关电路图 MOS管开关电路设计2023-07-20 4962

-

MOS管开关电路原理图2023-06-20 5132

-

分享几种常用的三极管和MOS管的基础知识及应用电路2023-03-30 9263

-

MOS晶体管结构与CMOS单元电路与版图阐述2023-01-28 3623

-

MOS管开关电路2021-10-22 2245

-

MOS存储单元的工作原理2021-07-28 2082

-

揭秘MOS管放大电路及原理2018-10-30 13311

-

mos管开关电路_pwm驱动mos管开关电路图分享2018-01-04 63168

-

MOS管驱动电路的基础总结2017-08-01 33314

-

MOS管开关电路是什么?详解MOS管开关电路2017-05-17 132527

-

四管动态MOS存储单元2009-12-04 2726

-

三态MOS动态存储单元电路2009-10-10 1519

全部0条评论

快来发表一下你的评论吧 !