使用具有精密相位控制的超宽带PLL/VCO用硅代替YIG调谐振荡器

描述

作者:Bob Clarke and Ian Collins

射频和微波仪器,如信号和网络分析仪,需要宽带、扫描频率信号来进行许多基本测量。然而,不合常理的是,宽带压控振荡器(VCO)通常具有最差的相位噪声,因为低Q和高K。VCO(VCO的调谐灵敏度,单位为MHz/V)来最大化其调谐范围。钇铁石榴石 (YIG) 调谐振荡器 (YTO) 凭借良好的宽带相位噪声性能和倍频程调谐范围巧妙地解决了这个问题,但可能很大、价格昂贵,并且由于其调谐电流而可能消耗数百 mA 电流。当然,它们仍然需要一个外部锁相环(PLL)来闭合环路,需要一个压控电流源来提供调谐电流。

YIG晶球看起来像一个高Q LC电路,其谐振频率与外部施加的磁场成线性比例。振荡器由电流通过单圈环路调谐,通过GHz范围内的倍频程或更多倍频程。YIG调谐振荡器具有低电平相位抖动,其约2 GHz至18 GHz的宽带特性(具有非常线性的调谐曲线)使其成为许多测量应用的热门选择。

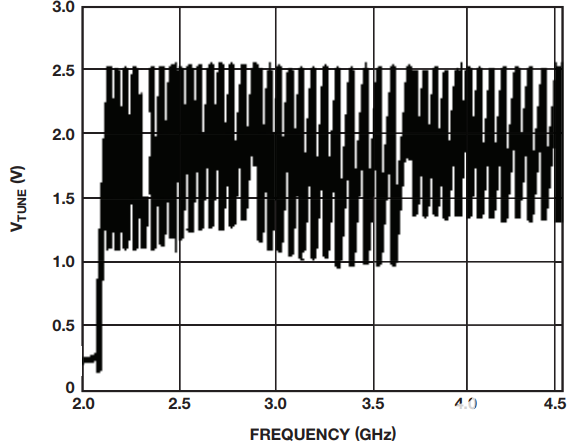

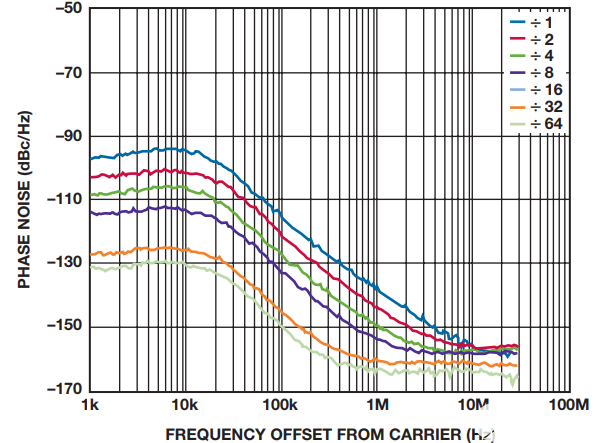

然而,YIG调谐振荡器和集成PLL/VCO IC之间的性能差距正在缩小。例如,集成PLL/VCO IC的最新进展,如ADI公司的ADF4355,其相位噪声比其前代产品有了很大的改善。他们还通过设计技术解决了宽调谐范围问题,例如将输出频率范围划分为多个相邻的子频段,其中每个子频段可以有一个专用的频段切换VCO,以增加调谐范围,同时使频段切换VCO看起来像具有中等K的单个VCO。VCO(如图 1 所示)给用户。接下来,辅助分频器和倍频器扩展了VCO调谐范围的频率覆盖范围,包括上面乘法和以下的除法。例如,ADF4355的基本调谐范围为3.4 GHz至7.2 GHz,通过分频扩展到54 MHz。频率每减半,相位噪声就会降低3 dB(如图2所示)。

图1.ADF4355 PLL/VCO中的多频段VCO由一系列振荡器组成,每个振荡器调谐整个频段的一小部分,并保持均匀的KVCO因此 V调整在整个范围内。调谐电压图的形状看起来像锯齿波,因为每个振荡器都有固定电容,这些电容与电压可变电容并联切换,一次切换一个,以最大化每个VCO的整体调谐范围。

图2.输出频率每减半,总相位噪声就会降低3 dB。在这种情况下,将3.4 GHz VCO除以64 GHz会导致相位噪声在130.10 MHz时以53 kHz偏移时优于−125 dBc/Hz。

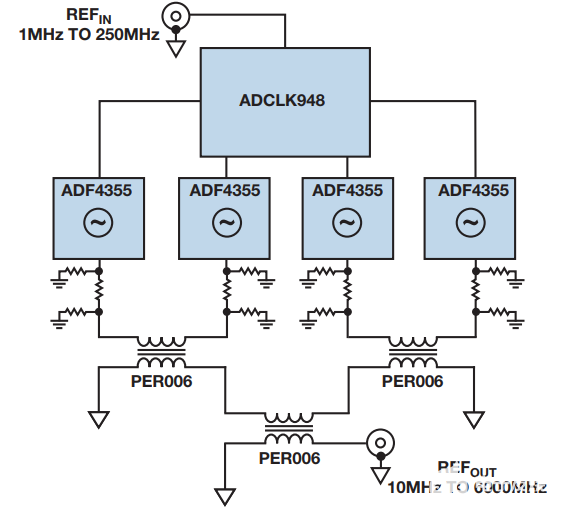

然而,即使集成PLL/VCO IC的调谐范围比YIG调谐振荡器更具可比性,仍然存在一个问题:YIG调谐振荡器仍然比最佳集成VCO提供12 dB的相位噪声性能。即使尚未闭合,也可以通过并联多个PLL/VCO的输出来缩小这一差距(如图3所示)。输出可以求和,相位噪声每增加一倍(3 dB),并联的PLL/VCO数量就会提高3 dB。例如,两个ADF4355 PLL/VCO可改善3 dB,4355个ADF6 PLL/VCO可改善4355 dB,9个ADF4 PLL/VCO可改善<> dB(如图<>所示)。

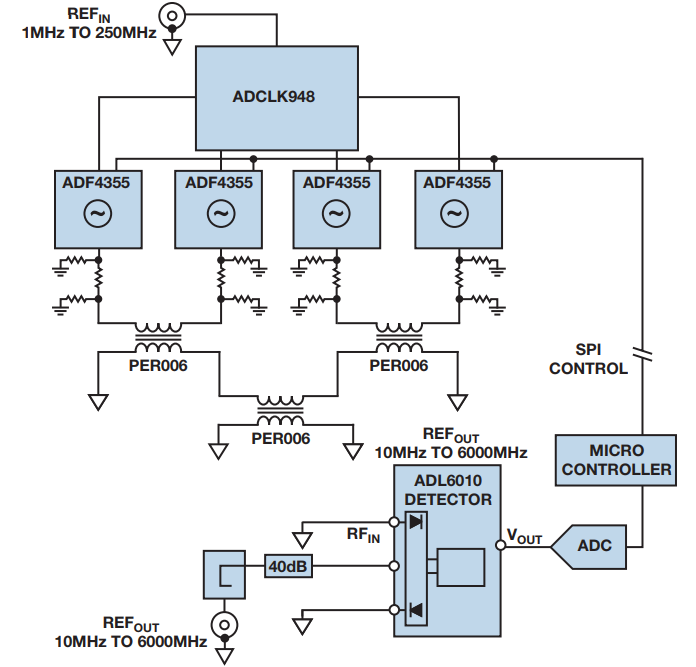

图3.通过同步多个PLL/VCO并组合其输出,VCO数量每增加一倍,相位噪声就会降低3 dB。此处并联显示了四个ADF4355,使整体相位噪声降低了6 dB。

图4.通过相位锁定并组合八个ADF4355 PLL/VCO的输出,与单个PLL/VCO相比,可以将整体相位噪声降低近9 dB。此处的频谱显示了单个ADF4355的输出相位噪声和4355个并联工作的同步ADF<>的输出总和的相位噪声。

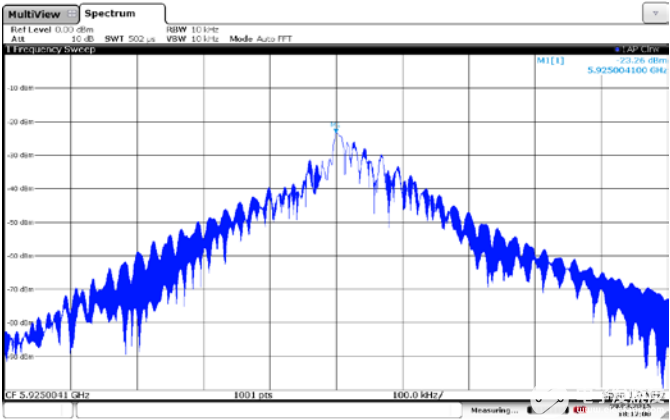

对PLL/VCO输出求和的关键是按相位操作所有振荡器的输出。我们将在这里讨论的示例并行使用四个PLL/VCO。正如人们可能猜到的那样,在同一印刷电路板上以相同的频率放置四个锁相环和压控振荡器会带来许多挑战。这些挑战中最主要的是孤立。PLL之间的隔离不良会导致一种称为注入锁定的现象(如图5所示),其中振荡器锁定到强信号或其谐波,而不是锁相环本身提供的调谐电压选择的频率。注入锁紧可以通过看到噪声和杂散的最初细微下降来观察到,因为两种锁定机制会产生互调失真。在更严重的情况下,信号看起来更像是调制载波,而不是连续的正弦波音调。

图5.当VCO的频率锁定到外部振荡而不是其控制电压时,就会发生注入锁定。结果是互调和相位噪声增加。

隔离需要各种技术和电路。例如,将参考信号缓冲到每个PLL(引脚REF伊纳和参考文献国际投资银行),通过使用缓冲器,在本例中为ADI ADCLK948 LVPECL 8:1时钟缓冲器。此外,最小化串扰需要正确端接源,负载引脚尽可能靠近源极和负载。还包括额外的接地并联电容(18 pF),以衰减VCO输出的任何泄漏,同时通过所需的基准频率。

其他需要隔离的路径是电源线。为了提供所需的隔离,每个PLL都有自己的高性能稳压器(ADI ADM7150),一个用于+5 V线路V。VCO、副总裁和 V雷格维科,VCO 供应在这里更为关键。模拟(AVDD)、数字(DVDD)和输出级(V射频) 线路也需要 3.3 V,并且每条线路也使用单独的稳压器。将每个PLL上的3.3 V线路连接在一起是可以接受的,前提是使用了良好的去耦。

在RF输出级上,辅助输出(引脚RF)输出+和参考文献出——) 被禁用并终止,以确保不会生成不需要的音调。输出射频呸——端接在 50 Ω负载及其互补输出 RF出达+,被馈送到高隔离功率组合器(Marki微波,PBR0006SMG)。选择该合路器是为了确保输出级之间的耦合保持在最低限度,同时在公共输出端提供组合信号。为了提高隔离度,其中一对组合两个PLL的输出,第三个合路器对前两个PLL的输出求和。

最后,Laird 的现成屏蔽提供了额外的隔离,以最大限度地减少可能以电磁方式耦合 VCO 的任何杂散辐射。总之,所有这些步骤确保了最佳的隔离。

ADF4355内置高分辨率24位调制器,除了允许生成小数N分频值外,还包含允许对RF信号相位进行小幅调整的电路。为了有用,相位值需要可重复。这需要使用功能相位重新同步。

相位再同步最好描述为在频率更新后将分数分频器(具有噪声整形的∑∆调制器)置于已知状态的功能。由于相位是相对测量值,因此当从相位为P1的频率F1变为频率F2时,重新同步功能被定义为功能,当变回频率F1时,相位应再次为P1,就像第一次测量一样。此功能与重新同步相结合,使我们能够调整相位,以最小化四个PLL中每个PLL之间的相位差,从而获得四个PLL的最大功率总和,从而最大程度地改善相位噪声。除了这些步骤之外,同时复位每个PLL的计数器也很重要,这可以通过使用芯片使能(CE)引脚的硬件关断和上电轻松实现。

过程和器件间的变化意味着,在遵循复位和重新同步程序时,我们不能假设每个PLL之间的相位差将足够接近于零,以最大限度地提高信噪比;因此需要一个外部校准电路。

校准过程很简单:打开单个PLL/VCO,并将其相位定义为零相。依次打开每个附加的 PLL/VCO,改变其输出相位,直到导通 PLL/VCO 的组合输出功率达到最大值,然后打开下一个 VCO 并再次调整其相位,直到 PLL/VCO 的组合输出功率再次达到最大值。请注意,当第二个 PLL/VCO 打开时,功率变化最大,因为组合功率加倍;对于每个后续的PLL/VCO,差异都会减小。实际上,这意味着并联的PLL/VCO数量每次增加一倍,信噪比就会增加。也就是说,两个并行提供 3 dB 的改进,四个提供 6 dB 的改进,八个提供 9 dB 的改进。当然,功率组合器的复杂性也会翻倍,因此四个PLL/VCO是一个实际的上限,16个和<>个PLL/VCO的并行回报递减。

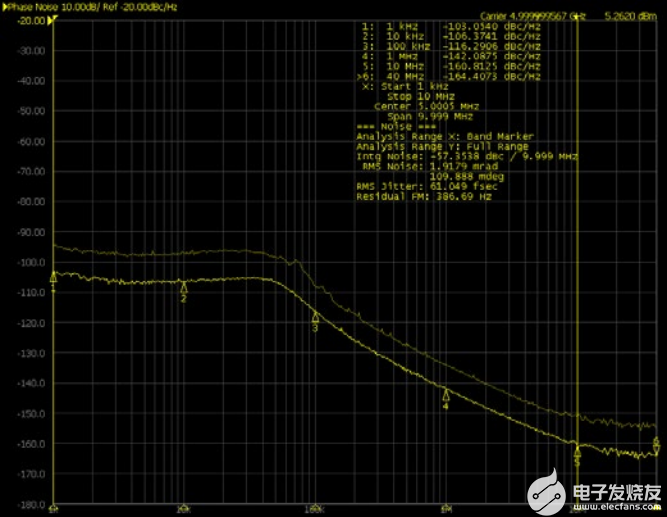

请注意,最佳相位性能和最大输出功率是巧合的,因此功率测量足以确保最佳的相位噪声性能。本例中的校准器是ADI ADL6010功率检波器,用于测量组合信号的输出幅度。通过这种方式,可以调整每个PLL的相位(在每个频率下),并在组合功率达到最大值时调整相位恒定(如图6所示)。对每个额外的PLL重复此过程,直到所有四个PLL都上电并进行调整,从而使合路器输出端的信号达到最大值。

图6.图中所示为四相对齐的ADF4355集成PLL/VCO,带有ADCLK948时钟缓冲器、合路器(PBR-0006SMG)和校准电路。

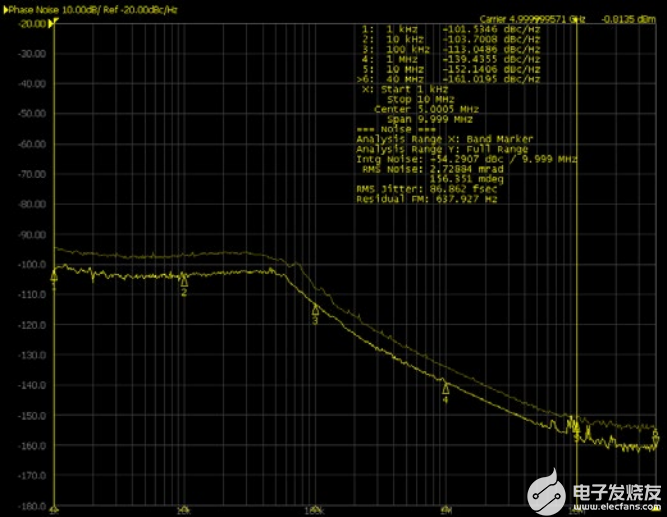

图7显示,实际结果遵循理论,即对于PLL/VCO的每加倍,并且写入正确的相位字,四个PLL/VCO的组合相位噪声比单个PLL/VCO的相位噪声提高6 dB。因此,当四个PLL/VCO同相组合时,一个ADF4355 PLL(134 MHz偏移时为–1 dBc/Hz)的性能可以提高6 dB,达到约–140 dBc/Hz。

图7.输出相位噪声图显示了单个ADF4355 PLL/VCO振荡器和四个ADF4355同相组合的相位噪声。

审核编辑:郭婷

-

基频高达20GHz的宽带YIG振荡器解决方案2020-07-10 2572

-

MLXB-0820调谐振荡器2020-03-02 739

-

MLXB-0218调谐振荡器YIG产品介绍2019-10-14 1518

-

MLTO-50613调谐振荡器YIG产品介绍2019-10-12 1040

-

MLMB-0306调谐振荡器YIG产品介绍2019-10-11 1197

-

使用具有精密相位控制的超宽带PLL/VCO替代YIG调谐振荡器硅片2017-06-09 1066

全部0条评论

快来发表一下你的评论吧 !