应用笔记|使用 STM32 缓存来优化性能与功率效率

描述

目录预览

1 ICACHE 和 DCACHE 概述

2 ICACHE 和 DCACHE 主要特性

3 ICACHE 和 DCACHE 的性能与功耗

4 结论

1.ICACHE 和 DCACHE 概述

本节概述了嵌入在基于 STM32 Arm Cortex内核的微控制器中的 ICACHE 和 DCACHE 接口。详细介绍了 ICACHE 和 DCACHE 框图架构以及在系统架构中的集成。

1.1 STM32L5 系列智能架构

此架构基于总线矩阵,允许多个主设备(Cortex-M33、DMA1/2 和 SDMMC1)访问多个从设备(如Flash 存储器、SRAM1/2、OCTOSPI1 或 FSMC)。

下图描述了 STM32L5 系列智能架构。

由于将 8-Kb 的 ICACHE 接口引入其 C-AHB 总线,通过快速总线从内部存储器(Flash 存储器、SRAM1 或SRAM2)或通过慢速总线从外部存储器(OCTOSPI1 或 FSMC)提取代码或数据时,Cortex-M33 的性能有所提升。

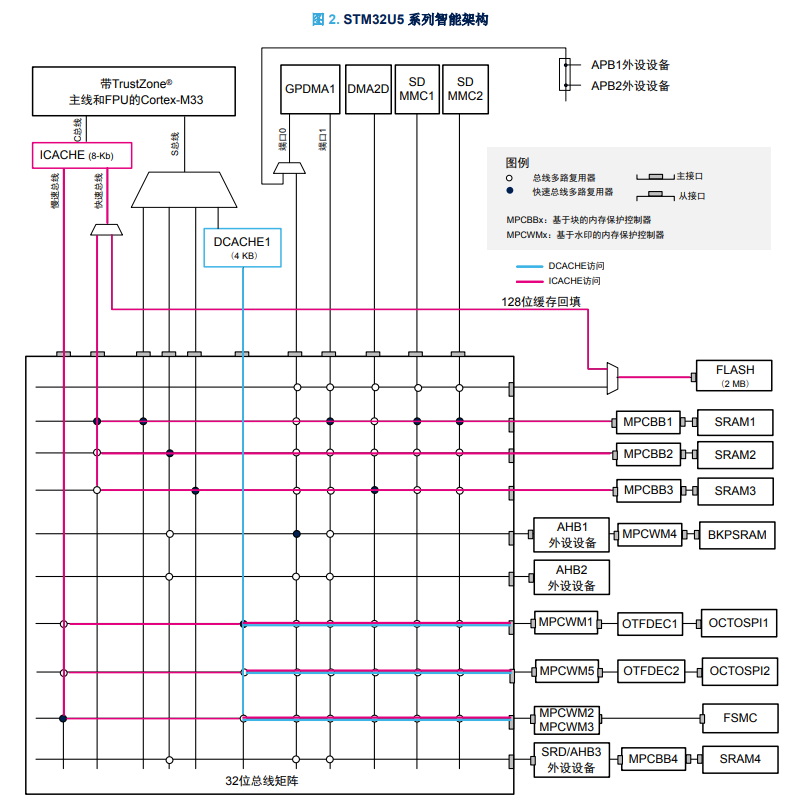

1.2 STM32U5 系列智能架构

此架构基于总线矩阵,允许多个主设备(Cortex-M33、GPDMA1、DMA2D 和SDMMC1/2)访问多个从设备(如 Flash 存储器、SRAM1/2/3/4、BKPSRAM、OCTOSPI1/2 或 FSMC)。

下图描述了 STM32U5 系列智能架构。

其 C-AHB 总线引入了 8-Kb 的 ICACHE 接口,通过快速总线从内部存储器(Flash 存储器、SRAM1、SRAM2 或SRAM3)或通过慢速总线从外部存储器(OCTOSPI1、OCTOSPI2 或 FSMC)提取代码或数据时,Cortex-M33 的性能有所提升。其 S-AHB 总线引入了 4-Kb 的 DCACHE 接口,提高了外部存储器(OCTOSPI1、OCTOSPI2 或 FSMC)的数据流量。

1.2 ICACHE 框图

ICACHE 框图如下图所示:

ICACHE 存储器包括:

• 具有以下元素的 TAG 存储器:

– 指示将哪些数据包含在缓存数据存储器中的地址标签

– 有效位

• 数据存储器,包含缓存的数据

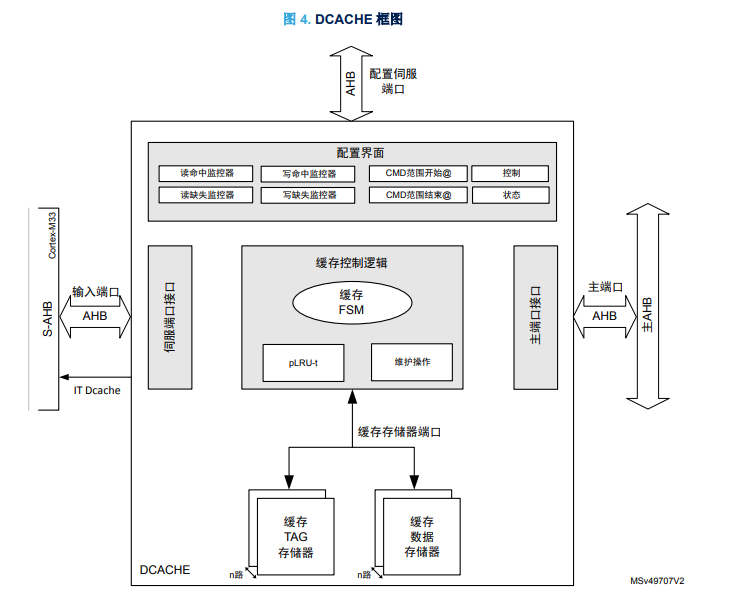

1.4 DCACHE 框图

DCACHE 框图如下图所示。

DCACHE 存储器包括:

• 具有以下元素的 TAG 存储器:

– 指示将哪些数据包含在缓存数据存储器中的地址标签

– 有效位 特权位

– dirty 位

• 数据存储器,包含缓存的数据

长按扫码关注公众号

更多资讯,尽在STM32

▽点击“阅读原文”,可下载原文档

原文标题:应用笔记|使用 STM32 缓存来优化性能与功率效率

文章出处:【微信公众号:STM32单片机】欢迎添加关注!文章转载请注明出处。

-

STM32GUI_使用 STLINK+stm32gui-pydfb 工具来实时查看图形缓存的图片2023-10-27 1789

-

AN2784应用笔记2023-10-10 1313

-

使用STM32缓存来优化性能与功率效率应用笔记2023-08-01 495

-

使用STM32缓存来优化性能与功率效率2023-02-06 3506

-

AN5597_STM32WB3或5xxx和STM32WB1xxx应用笔记2022-11-21 627

-

STM32CubeIDE使用笔记记录2022-01-26 2280

-

STM32官方应用笔记分类汇总2021-12-29 757

-

Linux和Android系统故障和优化性能的方法和流程探讨2019-07-22 1233

-

STM32_正交编码器接口应用笔记2016-11-10 1571

-

∑-ΔADC应用笔记2012-03-16 1988

-

IR推出高效率氮化镓功率器件2010-05-10 1427

-

PRM及VTM并联应用 应用笔记2009-11-20 3986

全部0条评论

快来发表一下你的评论吧 !