为什么要针对性的测试扩频时钟SSC呢?

电子说

描述

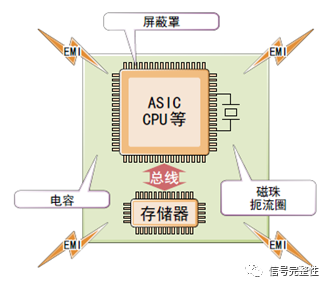

EMI是电子产品设计工程师不可绕开的一个话题。很多工程师在设计时都会遇到如何减小EMI的影响,使产品能正常的工作或者上市。

当然,解决EMI问题的方法非常多,比如做好电路匹配、做好隔离、屏蔽、减缓信号边沿变化速率等等。

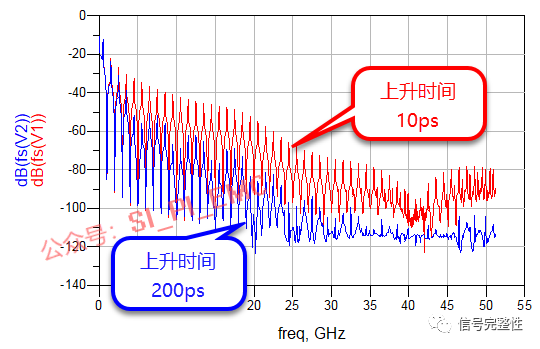

减缓边沿变化速率的方法有使用端接的方法、减小信号的驱动能力、使用扩频时钟等。

本文主要分享的是扩频时钟。扩频时钟(SSC:Spread Spectrum Clock)是为了防止数字信号或者时钟由于频谱在某个频点上功率过高而引起的EMI问题,所以对时钟或者数据的周期进行周期性调制(三角波调制)。SSC的单位是ppm(百万分之一个时钟或者一个数据的周期),该值表示最大的时钟周期或者数据周期为UI*(1+Xppm)。

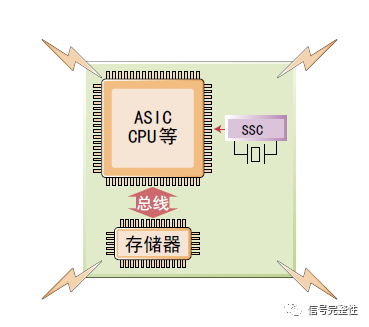

以前使用SSC都是外部器件,一般在电路上加上SSC器件,如下图所示:

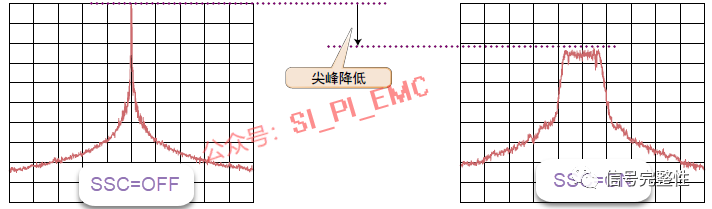

当使用SSC之后,其EMI辐射能量会显著降低,并且波峰更加的宽平:

现在很多总线,如USB3.0、QPI、PCIE、SATA、SAS等信号都支持SSC功能,并不需要在外部添加额外的SSC器件。使用SSC功能可以大幅降低无用的辐射,从而减少旁路电容、扼流圈、磁珠以及屏蔽罩等其他抑制干扰组件的使用,这样能有助于实现产品快速上市,并且能使产品小型化。

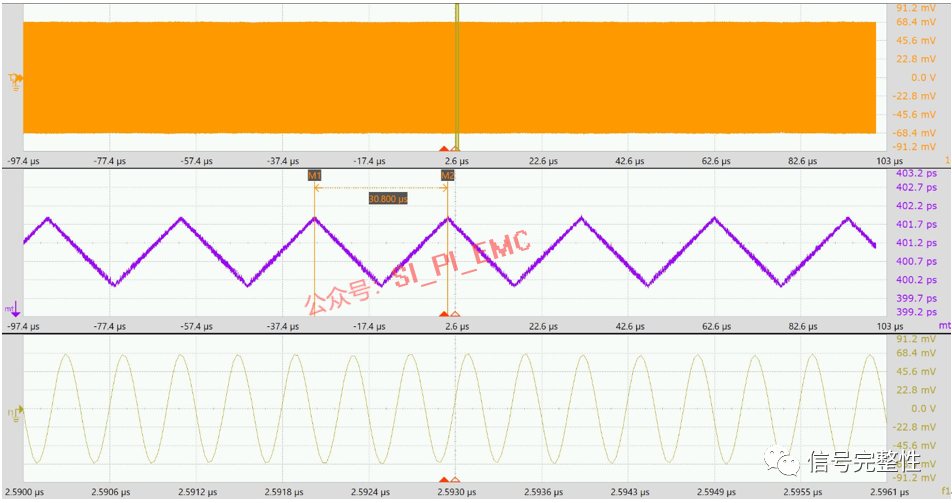

在某些高速串行总线测试时,也会针对SSC项进行测试,如下图则为SB3.0 5Gbps 使用CP1 码型测量SSC 的结果:

当然,为什么要针对性的测试呢?其中一个重要原因就是SSC确实能抑制EMI的影响,但是会导致信号的抖动增加。如果抖动过大或者超过总线规范要求时,这就有可能导致信号的误码增加,进而影响到电子产品系统的稳定性。所以在产品设计过程中,要平衡EMI的表现和SI的性能。

审核编辑:刘清

-

LMK3H0102-Q1 参考无晶体时钟发生器技术文档总结2025-09-10 1393

-

扩频时钟技术分享:SSC技术是什么、SSC对测试高速总线信号的影响2025-01-06 9185

-

关于AD9627针对性能指标测试有一些疑问求解2023-12-22 593

-

SSC扩频时钟概述和主要参数2023-11-22 10321

-

面向验证工程师的PCIe扩频时钟(SSC)2023-05-26 11589

-

讲讲SSC扩频时钟2022-08-11 15795

-

频谱仪维修知识:常见故障该如何进行针对性解决2021-12-13 2828

-

针对性的接口电路设计方案2021-12-01 1377

-

时钟扩频改善车载电子电磁兼容性能2017-11-09 947

-

中兴的无线LTE开发部,该看什么针对性的书?2014-12-03 4771

-

高速信号扩频时钟测试2011-05-17 6202

-

解决TD-SCDMA室内覆盖的针对性策略2009-12-19 671

-

如何进行PCI-Express的一致性测试和分析2009-04-08 4302

-

REACH预注册截止日期临近,IPC出版针对性指导手册2008-11-22 1063

全部0条评论

快来发表一下你的评论吧 !