基于iMAX6的DDR设计方案

电源/新能源

3642人已加入

描述

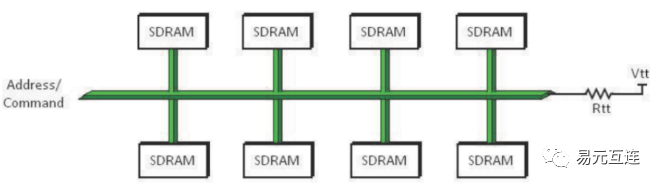

随着DDR频率的不断提高,DDR芯片也在不断增多,本文就以iMAX6的DDR设计来阐述。iMAX6采用4G(8片)DDR设计,使用CS[1:0]两个片选信号,每个片选信号各控制2G(4片)DDR,如下图所示,当使用这种拓扑结构时,终端的匹配电阻是不可缺少的。

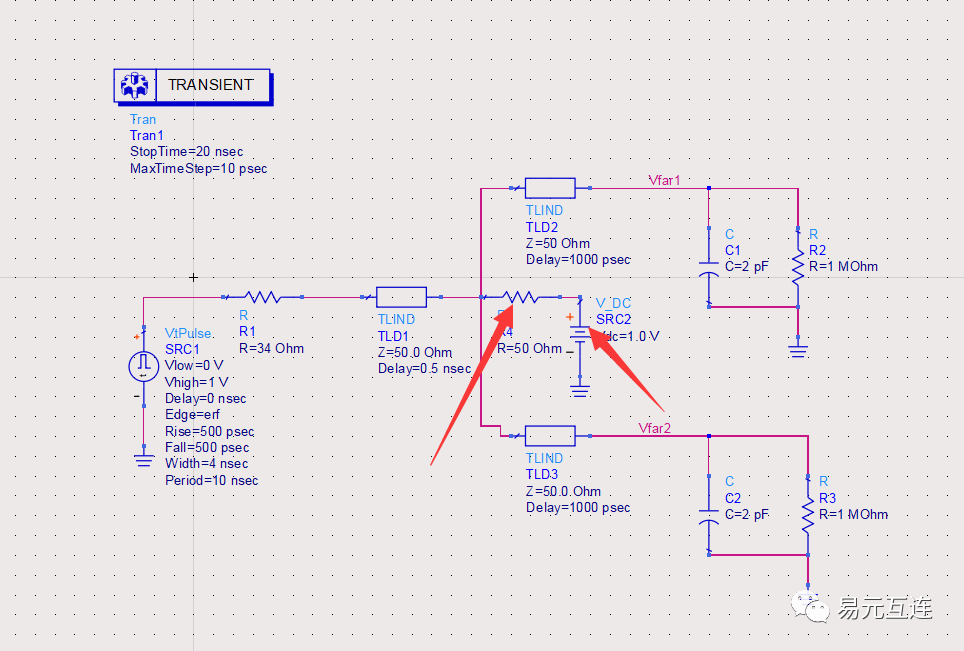

如上图,这个上拉的匹配电阻为什么要加?HW工程师也很难说清楚的,只是说是按照设计手册来添加的,今天小易就用ADS来仿真下添加匹配电阻和不添加匹配电阻的效果。 如下图先在ADS中新建一个信号完整性原理图,在DDR的分叉处添加一个50欧的上拉电阻。

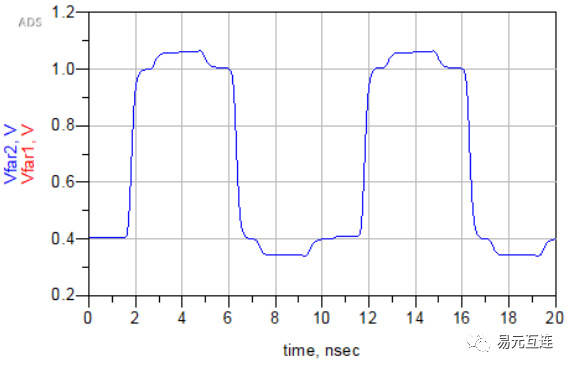

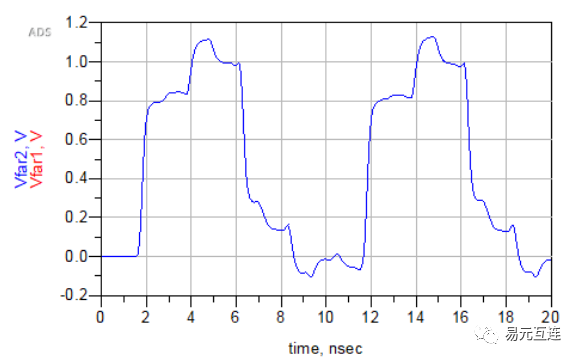

对该Address信号线进行仿真,仿真后的结果如下图所示。

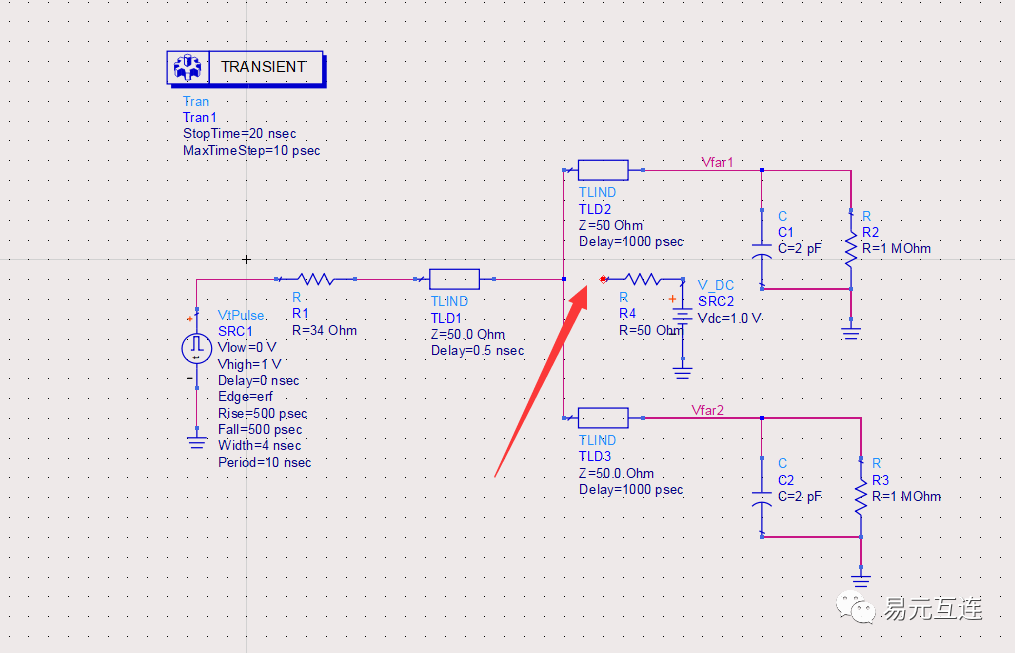

然后,将该电阻的电路断开,如下图所示。

然后,仿真后波形如下图所示,可以看到明显不如加了上拉的电阻的效果。

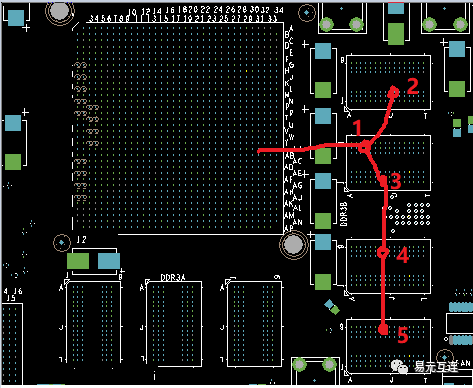

那接着讨论下一个问题,比如下图的布局,一根Address的线,要同时连接到4片DDR上去,1-5处打孔的地方都可以放置该上拉电阻,那究竟该放到哪处合适呢?

从ADS的信号完整性原理图上可以看到,仿真时将50欧的上拉电阻放在1的位置,也就是第一个从CPU打孔分叉的地方,这样效果才最好,放在其他地方的效果比较差,比如放在5处,实际和不放上拉电阻的效果差不多。

编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

分享----单相智能电表设计方案2012-06-05 6636

-

直立行车参考设计方案2016-08-17 2684

-

STM32设计方案与示例分享2018-09-03 3691

-

基于IMAX6单独编译simpleCamera APK2019-10-30 1461

-

求一种嵌入式IPv6协议栈的设计方案2021-05-27 2391

-

求一种UPS电源逆变器设计方案2021-11-15 1923

-

求一种基于STM32F103C8T6的无线飞鼠设计方案2021-12-20 1895

-

基于Spartan-6的FPGA SP601开发设计方案2010-04-02 2849

-

并网逆变器的设计方案2016-01-11 1221

-

6进制计数器设计方案汇总(三款模拟电路原理图分享)2018-01-17 81380

-

DDR SDRAM控制器的设计与实现2021-03-28 1232

-

小米首款IMAX Enhanced认证机型 - 小米电视6至尊版 正式发布2021-06-28 3184

-

IMAX Enhanced 亮相ChinaJoy IMAX展台2021-08-02 673

-

基于6LoWPAN协议的智能小区设计方案2023-10-19 433

-

DDR6和DDR5内存的区别有多大?怎么选择更好?2024-01-12 14525

全部0条评论

快来发表一下你的评论吧 !