解析Armv8.1-M的一些特性

描述

简单阐述下ARMv8.1-M的一些特性,更多的特性及其详细信息,请查看Armv8-M Architecture Reference Manual-DDI0553B_m。

1. MVE(M-Profile Vector Extension) or Helium technology

MVE其实就是ARM-M系列的SIMD特性,使得M-profile processor在DSP和AI等应用领域具有更强的处理能力。

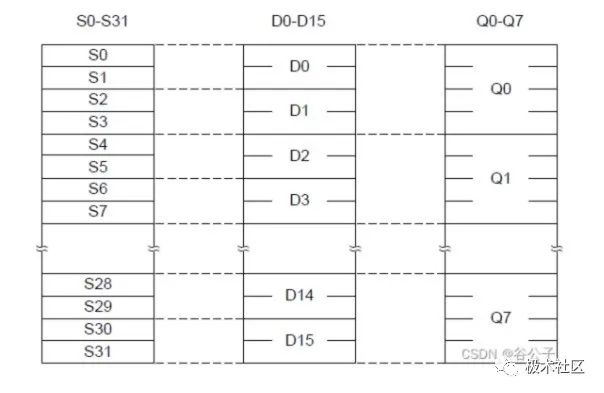

8个128bit的vector size,可以拆成多个elements。

lane predication,适用code形式:if (a[i] != 0) then b[i]=a[i]*b[i],当然还有其它变形形式,这时候需要结合VPTE指令来配合。

Vector gather load和vector scatter store,如VLDRB, VLDRH, VLDRW, VLDRD (vector)和VSTRB, VSTRH, VSTRW, VSTRD (vector)等。

MVE interleaving/de-interleaving loads and stores,如VLD2/VLD4和VST2/VST4等。

Beatwise operation,因为vector可能的一条指令会执行多个步骤,如果在执行期间有中断,可以用ECI寄存当前instruction执行到哪个步骤了。

Support Circular Buffer,combine an instruction that generates wrapping offsets(VIWDUP) with a scatter‐gather instruction to access data at these offsets。

2. LoB/Loop Tail Predication/BF

LoB/Loop Tail Predication/BF可以用于提高loops循环和branches分支的效率,减少不需要耗在control flow指令上的时间。

Loop iteration optimization: LoB,在LO_BRANCH_INFO寄存器里存入end_addr和jump_addr,然后next instruction的address匹配上end_addr就可以直接跳转了,甚至都不需要去去LE跳转指令了。减少在必须要的循环控制指令上的时间消耗。需要用到WLS和LE指令。

Loop Tail Predication,假如处理的elements个数不是vector length的整数倍内,例如vector length=4,但要处理7个elements?一种方法就是最后一个使用普通的非vector去处理,前面的仍然用vector处理。另一种更好的方法是MVE中引入了WLSTP/LETP指令对,允许loop迭代中的最后一条vector instruction只处理remaining elements,在loop开始之前用WLSTP设置LR寄存器的值为多少个要处理的elements,每循环一次,LETP对LR减去vector的elements个数。

Branch feature:类似于提供“variable length delay slots” – to further eliminate bubbles caused by branch instructions (but only direct branches), since we already have the “LO_BRANCH_INFO” hardware available and can double use it to squeeze out a bit more performance.BFX指令执行的时候,会设置LO_BRANCH_INFO去指示在哪一个address上会发生跳转,因此当执行执行到该address时,就可以执行跳转了,甚至都不需要取和译码BX LR指令了,因此减少因为执行分支而造成的branch penalty(通常那些已经取的instruction会被处理为Bubbles)。如果在BFX和BX期间发生interrupt了,那么LO_BRANCH_INFO会被清除,这时候就需要BX LR了。如果在processor中不支持Branch Feature这个特性,那么将被实现为NOP。

3. Security 由于越来越多的MCU会运行第三方软件和连接到互联网上,如何保证不被黑客攻击也成了重要的问题。

Execution permission:例如在v8.1-M里有PXN/UXN,减少被利用堆栈溢出攻击而导致的安全问题。PXN是Privileged Execute-Never(这个是因为有些code就是想让它在non-priv模式下执行,来限制访问权限,防止资源受到破坏),UXN是non-Privileged Execute-Never。在MPU_RLAR寄存器中有PXN bit,如果某个region的该bit置为1,那么privilege去访问该region的code会fault exception。

V8.2-M PAC(Pointer Authentication): 减少利用RoP(Return-oriented Programming)攻击导致的安全问题 。将会对return address(pointer)进行加扰,然后要返回时去除扰动,如果认证通过,那么就正常返回,反之报出exception。

V8.2-M BTI(Branch Target Instructions): 减少利用JoP(Jump-oriented Programming)攻击导致的安全问题。BIT的基本思想就是限制indirect branch只能跳转到特定的address空间上(only branching to allowed “landing pad instructions”)。

DIT(Data Independent Timing):同样的instruction可能会花费不同的执行时间,例如处理11和9999999999的算术运算占用时间不一样的,这样可能会暴露data信息给黑客。因此在AIRCR寄存器中增加了DIT bit,如果使能DIT功能,那么所有ALU instructions的执行时间才会采用最长的cycle数,也就是通过降低performance来换取安全。

UDE(Unprivileged Debug Extension):在v8.0-M中,如果secure debug打开,那么software开发人员对priv和un-priv的secure world有完全的debug访问权限。但是,如果禁用了secure debug,那么debugger将不能访问所有的secure world。在v8.1-M中新增了更细粒度的debug方式(UDE),当secure debug被关闭了,secure priv software可以通过DAUTHCTRL寄存器的UIDEN和UIDAPEN来使能UDE。这样也可以使用unpriv去debug一些library code的了,而不是局限于privilege模式才能debug。另外说下,ARMv8在handler mode下是privilege的,在thread mode下,可能是priv或un-priv,取决于CONTROL寄存器的值。

4. 附注

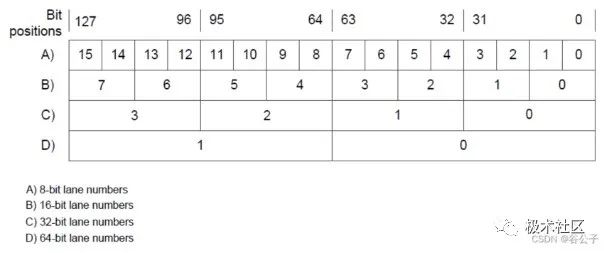

在ARM-M手册中涉及到lanes、beats和elements的概念。

operation的lane宽度是由正在执行的instruction决定的。允许的lane宽度和每一个beat进行的lane operation如下:1个beat是32bit,lane width可以有8/16/32/64bit.

For a 64-bit lane size, a beat performs half of the lane peration.

For a 32-bit lane size, a beat performs a one lane operation.

For a16-bit lane size, a beat performs a two lane operations.

For an 8-bit lane size, a beat performs a four lane operations.

elements就是表示有多少个data会放在每个lane中。比如lane=16bit,那么element的size就为16bit(2Byte, size=2’b01)。其它类似。因为lane最大为64bit,也就是说elements最大也就是64bit(4Byte, size=2’b11)。

虽然vector instruction可以同时进行多个elements的运算,有时候element size(esize)可以为32bit,但要运算的data实际为16bit,如VLDRH,这时候会对从memory里load过来的data进行zero或sign-extended,然后才放到vector register。这个实际给每个element load的data大小就是msize,因此msize肯定不大于esize的。总得来说,msize永远不会大于esize,如果msize

当然,在processor实现时,不只是每一个beat只load一个msize大小的data,这样效率太低,如果在data width允许的情况下,可以load多个msize大小的data,也就是一次搞定multiple elements。

我们假设一次实际load的data为dsize,对scalar来说,由于不会进行vector操作,esize没什么用,msize也永远等于dsize。对vector来说,vector register存在多个elements的操作,如果esize用于表示每个element的大小,msize是element中真正会填充的数据大小,如果dsize>msize,也就是说每一次load的data其实可以填充多个elements的,比如dsize=Word, msize=Byte, esize=Byte,那么只需要load 4次data就可以填满1个register vector了,如果每次load的size为msize(Byte),那么需要load 16次才可以填满,想想就知道效率很低的。

如果dsize

不过有一点要注意,在做对齐检查和atomicity分析时,由于实际其实就是要load msize大小的数据,dsize只是投机多搞一些数据回来,因此检查和分析还是要按msize来的。

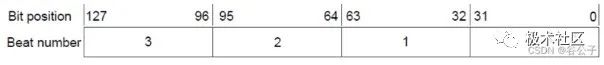

Vector instruction涉及到128bit,也就是有4个beats,因此是从beat0到beat3顺序执行的。

在每一个architecture tick下,会执行多少个beat,表征了该system是多个beat。如下:

In a single-beat system, one beat might occur for each tick.

In a dual-beat system, two beats might occur for each tick.

In a quad-beat system, four beats might complete for each tick.

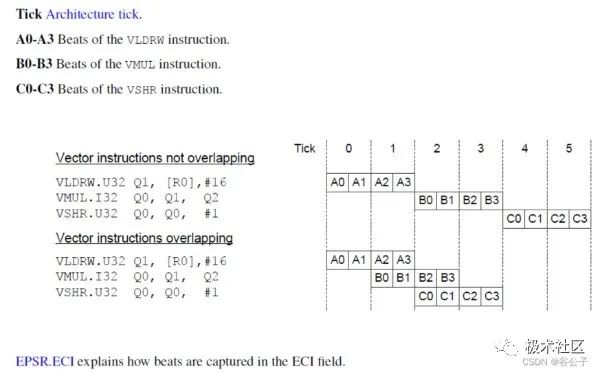

ARM的cortex-M55就是一个dual-beat的processor。在dual-beat overlap system中,意味着上一条vector instruction的最后two beats可以和后一条vector instruction的two beats可以重叠起来,加快执行效率。以下是dual-beat system在每一个architecture tick下,执行的示意图。

如果data dependency是以beat粒度,而不是instruction粒度进行的,architecture是允许vector instructions有overlap的。在每一个architecture tick下,architectural instruction的重叠情况可由EPSR.ECI值来表示。

审核编辑:汤梓红

-

keil mdk的一些常见错误解析2018-07-06 1502

-

使用ISE 13.3更改8.1 FIFO IP内核中的一些参数可能有什么问题?2019-06-26 1589

-

ARMv8-A AArch32主要特性2021-02-19 2837

-

Armv8.1-M PAC和BTI扩展简析2022-08-05 2916

-

介绍Armv8.6-A引进的一些新功能的概况2022-08-08 2076

-

ARMv8-M处理器故障处理和检测2023-08-02 689

-

Armv8.1-M性能监控用户指南2023-08-22 717

-

模拟电路的一些简单的特性2009-11-21 1014

-

下一代Armv8.1-M架构能够提升最小型边缘设备的机器学习能力2019-02-19 1574

-

直流电机的一些特性2021-09-15 940

全部0条评论

快来发表一下你的评论吧 !